第四篇:zc706的SOC简单介绍

目的:在上面几篇的感性基础认识上,深入探索zc706的SOC芯片的构成,对SOC作简单介绍。

1、 概述

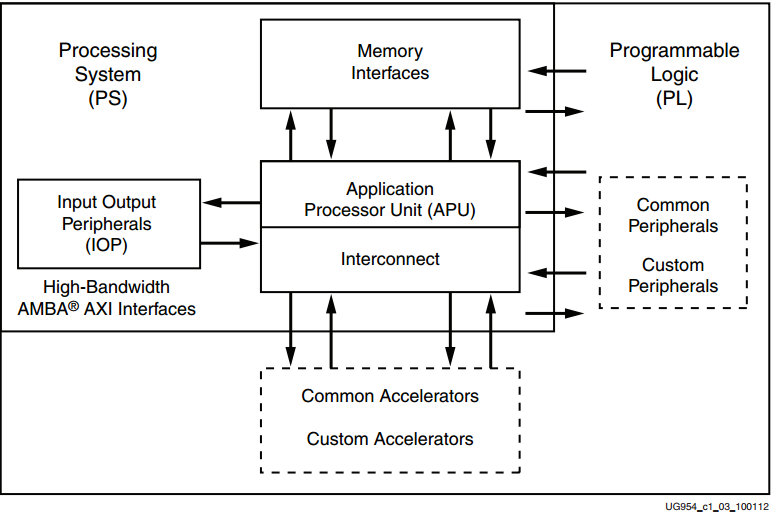

Zc706评估板核心是Zynq-7000 XC7Z045-2FFG900C AP SoC。这个XC7Z045 AP SoC由集成的PS和可编程的PL构成。高层框图如图1-1所示。

图1-1 高层框图

图1-1知道,PS主要由APU处理器、Interconnect互联、内外部memory接口、IOP构成。PS独立于PL运行,且在上电或重启时启动。

目前我们只关注与PS部分,因此对于PL部分以及如何与PL交互的通信接口将不会涉及。

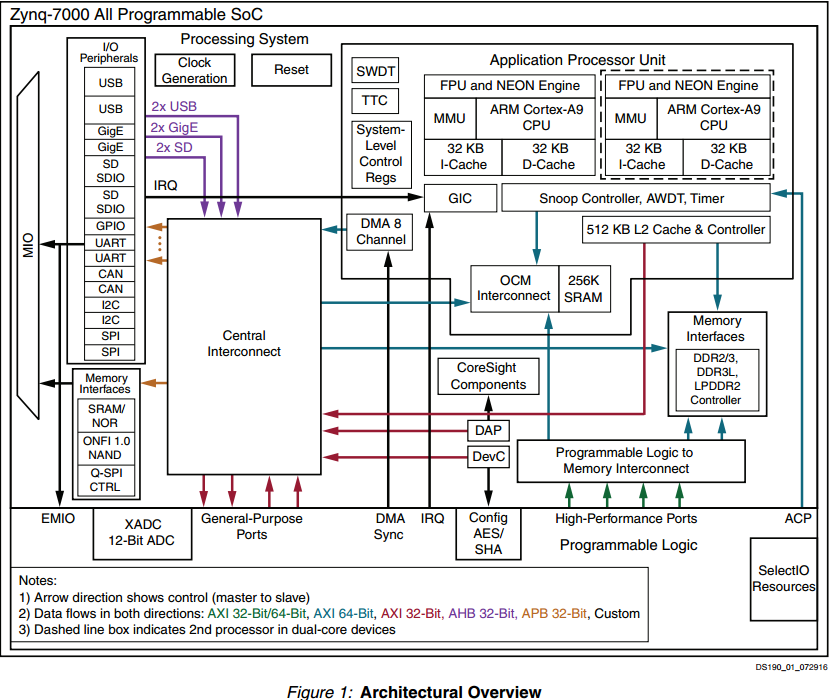

更详细的系统级框图见1-2图:

图1-2 zynq-7000框图

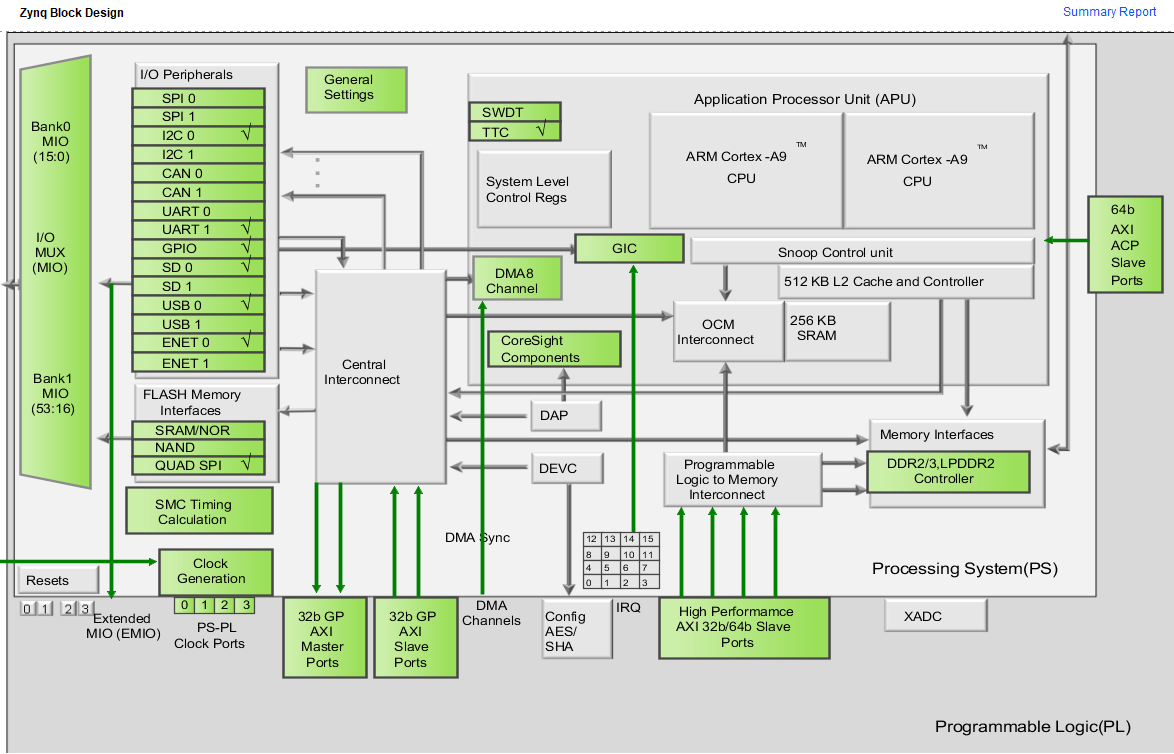

在vivado下选择zc706开发板,且导入zynq7芯片后,双击打开芯片,将看到整体SOC的构成图:

可看到SOC由PS和PL构成。Xilinx对zynq7000系列提供了大量的IP核,且对于在PS和PL下的外设裸机和Linux驱动程序都是可用的。(注意这里的驱动是指操作底层硬件状态的驱动已经提供,但是对于如何配置/操作外设来真正收发数据是需要自行开发的。虽然在SDK中提供了示例程序,但并不包含所有使用情形。)

上图中绿色部分是可以配置的,灰色部分则不可以配置。

对于一般开发板的arm程序,即使用PS侧的常用外设即usb、uart时,由上述两个图可以看到外设与存储器memory的收发都通过Interconnect交换,且外设的IRQ中断连接到APU的GIC(一般中断控制器)。

备注:更详细的SOC器件信息,见DS190和UG85文档。

备注:更详细的SOC器件信息,见DS190和UG85文档。

备注:更详细的SOC器件信息,见DS190和UG85文档。