3-8译码器

数字电路(真值表)

| A | B | C | OUT |

| 0 | 0 | 0 | 0000_0001 |

| 0 | 0 | 1 | 0000_0010 |

| 0 | 1 | 0 | 0000_0100 |

| 0 | 1 | 1 | 0000_1000 |

| 1 | 0 | 0 | 0001_0000 |

| 1 | 0 | 1 | 0010_0000 |

| 1 | 1 | 0 | 0100_0000 |

| 1 | 1 | 1 | 1000_0000 |

my3_8.v

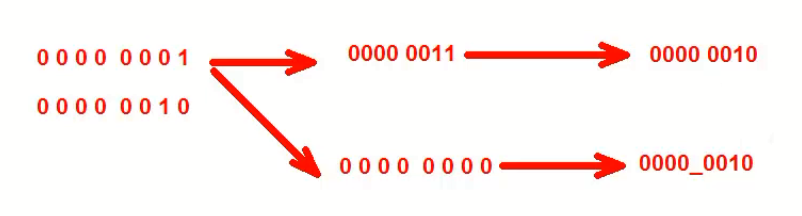

1 module my3_8(a,b,c,out); 2 3 input a; //输入端口A 4 input b; //输入端口B 5 input c; //输出端口C 6 7 output [7:0]out; //输出端口 8 reg [7:0]out; //寄存器型“在always块中的out必须是reg寄存器型” 9 10 always@(a,b,c)begin 11 case({a,b,c}) 12 3'b000:out = 8'b0000_0001; 13 3'b001:out = 8'b0000_0010; 14 3'b010:out = 8'b0000_0100; 15 3'b011:out = 8'b0000_1000; 16 3'b100:out = 8'b0001_0000; 17 3'b101:out = 8'b0010_0000; 18 3'b110:out = 8'b0100_0000; 19 default out = 8'b1000_0000; 20 endcase 21 end 22 endmodule

testbench

my3_8_tb.v

1 `timescale 1ns/1ps 2 3 module my3_8_tb; 4 5 //激励信号 6 reg a; 7 reg b; 8 reg c; 9 10 //观测信号 11 wire [7:0] out; 12 13 my3_8 u1( 14 .a(a), 15 .b(b), 16 .c(c), 17 out(out) 18 ); 19 20 inintial begin 21 a = 0;b = 0;c = 0; 22 #200; //延时200ns 23 a = 0;b = 0;c = 1; 24 #200; //延时200ns 25 a = 0;b = 1;c = 0; 26 #200; //延时200ns 27 a = 0;b = 1;c = 1; 28 #200; //延时200ns 29 a = 1;b = 0;c = 0; 30 #200; //延时200ns 31 a = 1;b = 0;c = 1; 32 #200; //延时200ns 33 a = 1;b = 1;c = 0; 34 #200; //延时200ns 35 a = 1;b = 1;c = 1; 36 #200; //延时200ns 37 $stop; //停止仿真 38 end 39 endmodule

后模拟仿真,电路级变换,存在的可能电路波动错误

4-16译码器