一.寄存器的含义、分类及其逻辑结构

注:本文所有的内容皆是在8086CPU结构下。

寄存器的含义:寄存器是在CPU中进行信息存储区域。它是CPU中的主要部件。是程序猿可以用指令读写的部分。

寄存器的分类:8086CPU总共有14个寄存器,分别是AX、BX、CX、DX、SI、DI、SP、BP、IP、CS、SS、DS、ES、PSW。其中AX、BX、CX、DX这四个寄存器通常用来存放一般性的数据,被称为通用寄存器。

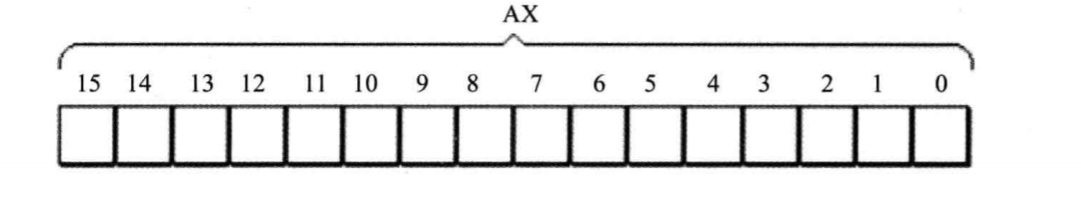

寄存器的逻辑结构:8086CPU的所有寄存器都是16位的,以AX为例,寄存器的逻辑结构图如下图所示

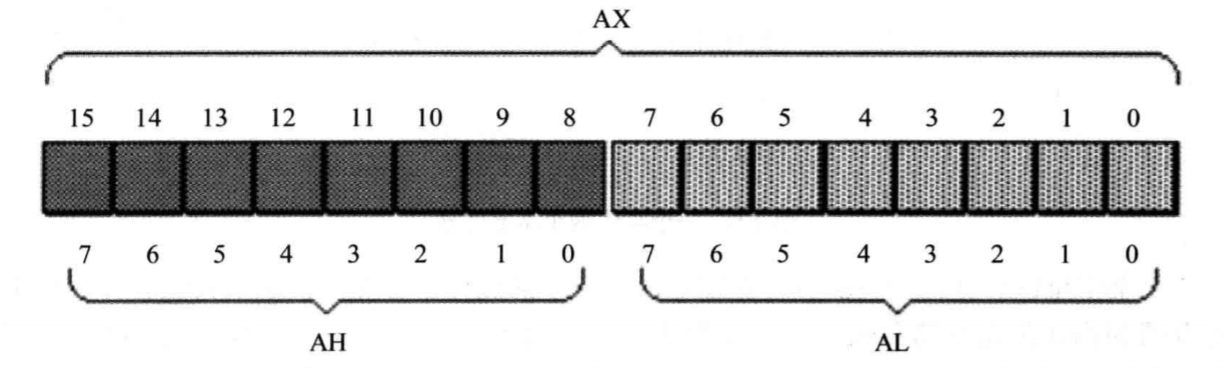

但是8086CPU的上一代的寄存器是8位的,所有为了保证兼容,使原来的基于上代CPU编写的程序稍加修改就能运行在8086之上,所有8086的CPU的AX、BX、CX、DX这四个寄存器都可以分为两个独立使用的8位寄存器。

- AX可以分为AH和AL;

- BX可以分为BH和BL;

- CX可以分为CH和CL;

- DX可以分为DH和DL;

以AX为例,8086CPU的16位寄存器分为两个8位寄存器的情况如下图所示。

二.几条汇编指令

通过汇编指令控制CPU进行工作,看一下如下图的几条指令。

注:在写一条汇编语言或一个寄存器的名称时不区分大小写,并且在进行数据传输时,要注意指令的两个操作对象的位数应当是一致的。

三.CPU如何在内部形成物理地址?

- 物理地址:CPU访问内存单元时,要给出内存单元地址。所有的内存单元地址构成的存储空间是一个一维的线性空间,每一个内存单元在这个空间中都有唯一的地址,我们将这个 地址称为物理地址。

- 16位结构的CPU:概括地讲,16位结构(16位机,字长为16等等常见的说法,与16位结构的含义相同)描述了一个CPU具有以下几方面的结构特性

- 运算器一次最多可以处理16位数据

- 寄存器的最大宽度为16位

- 寄存器和运算器之间的通路为16位

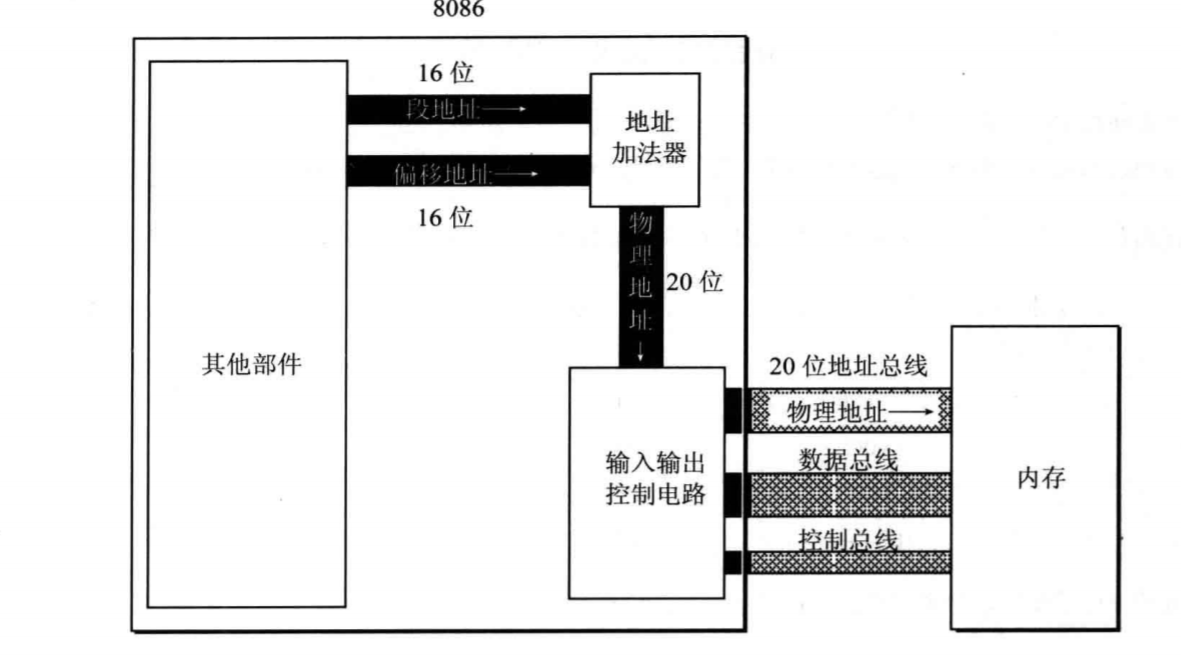

- CPU给出物理地址的方法:由于8086CPU有20位地址总线,可以传送20位地址,但是16位CPU只能一次性处理,传输,存储16位地址,所以8086CPU采用一种在内部用两个16位地址合成的方法来形成一个20位的物理地址。其逻辑结构如下图所示。

- 当8086CPU要读写内存时:- CPU中相关的部件提供两个16位的地址,一个称为段地址,另一个称为偏移地址;

- 段地址和偏移地址通过内部的总线送入一个称为地址加法器的部件;

- 地址加法器将两个16位地址合成为一个20位的物理地址;

- 地址加法器通过内部总线将20位物理地址送入输入输出控制电路;

- 输入输出控制电路将20位物理地址送上地址总线;

- 20位物理地址被地址总线传送到存储器。

- 地址加法器:地址加法器采用物理地址=段地址X16(即对于16位地址,向左移一位,对于二进制地址,向左移四位,即乘以2的四次方)+偏移地址的方法合成物理地址。

四.如何用CPU读取和执行指令并且修改CS、IP指令?

- 段寄存器:上文我们已经说到,段地址。而段地址存储的部件称为段地址。8086CPU有四个段寄存器:CS、DS、SS、ES。

- CS和IP:CS和IP是8086CPU最关键的寄存器。他们指示了CPU当前要读取指令的地址。CS为代码段寄存器,IP为指令指针寄存器。

- 8086CPU读取、执行指令的原理:在8086机中,任意时刻,设CS中的内容为M,IP中的内容为N,8086CPU将从MX16+N单元开始,读取一条指令并执行。其工作过程可以简要如下:

- (1)从CS:IP指向的内存单元读取指令,读取的指令进入指令缓冲器;

- (2)IP=IP+所读取的指令长度,从而指向下一个指令

- (3)执行指令,转到步骤(1),重复这个过程。

注:在内存中数据和指令没有任何区别。CPU将CS:IP指向的内存单元的内容看作指令。

- 修改CS、IP指令:可以用jmp指令修改CS:IP指令内容。其格式如下:"jmp 段地址:偏移地址",若仅仅想修改IP的内容,可用"jmp 某一合法寄存器"的指令完成,如下图所示。

注:无法用mov指令去修改CS:IP地址内容。