做数字IC工程师可不能只在RTL级打转,电路级很多知识也要掌握。但是因为知识比较零散,所以发一博来做个随记好了。

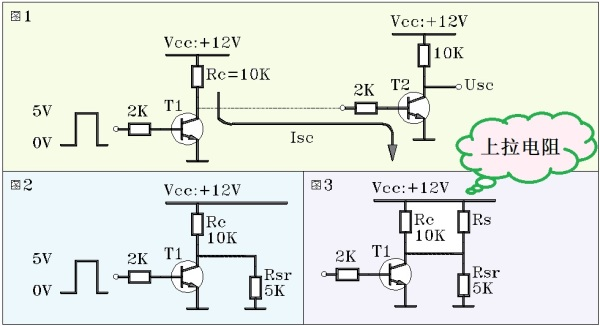

上拉电阻

上拉电阻与下拉电阻用在什么场合?

答:用在数字电路中,存在高低电平的场合。

上拉电阻与下拉电阻怎么接线?

上拉电阻:电阻一端接VCC,一端接逻辑电平接入引脚(如单片机引脚)

下拉电阻:电阻一端接GND,一端接逻辑电平接入引脚(如单片机引脚)

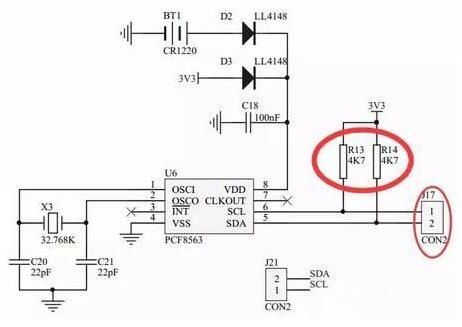

如上图,R13和R14,一端接到了3.3V,一端通过J17连接到单片机引脚,这两个电阻就是上拉电阻。

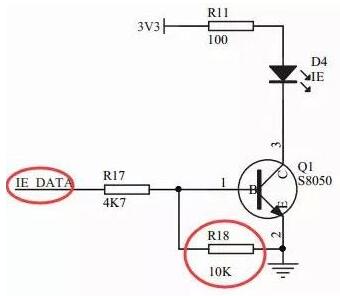

如上图,R18的一端连接到了GND,一端连接到了单片机的引脚(只不过是串了一个电阻后连接到了单片机引脚)。所以这个就是下拉电阻。

上拉电阻和下拉电阻有什么用?

提高驱动能力:

例如,用单片机输出高电平,但由于后续电路的影响,输出的高电平不高,就是达不到VCC,影响电路工作。所以要接上拉电阻。下拉电阻情况相反,让单片机引脚输出低电平,结果由于后续电路影响输出的低电平达不到GND,所以接个下拉电阻。

在单片机引脚电平不定的时候,让后面有一个稳定的电平:

例如上面接下拉电阻的情况下,在单片机刚上电的时候,电平是不定的,还有就是如果你连接的单片机在上电以后,单片机引脚是输入引脚而不是输出引脚,那这时候的单片机电平也是不定的,R18的作用就是如果前面的单片机引脚电平不定的话,强制让电平保持在低电平。

再这么解释一下吧,如果IE_DATA那个地方,不连接任何引脚,那么由于R18的下拉作用,IE_DATA就是低电平,所以三极管就不会导通。

另外一种更加简单的理解方法:

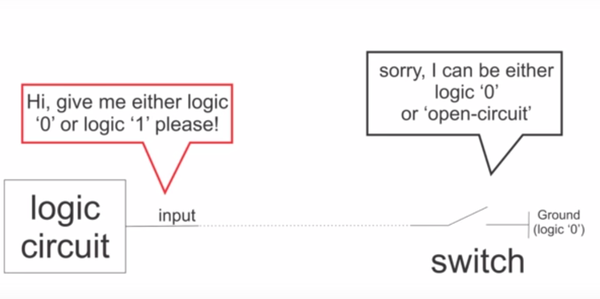

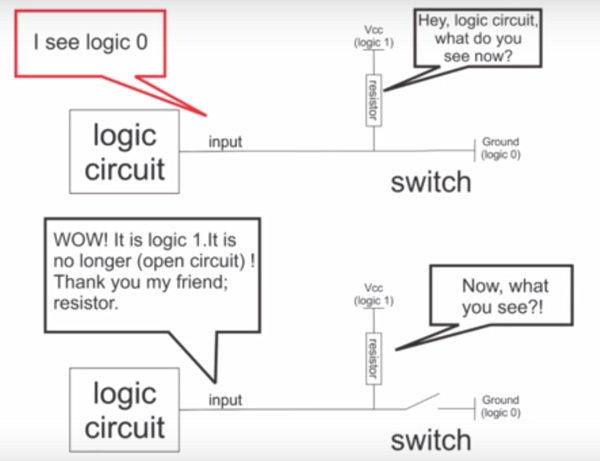

CPU期待pin脚的输入是0 or 1.但是如果pin脚连到的是一个短路开关,那么pin脚的电压状态是0 or open。至于这个open状态,设备启动时CPU读到的是啥很可能飘忽不定。

因此给pin脚到短路开关之间接入一个很大的电阻,电阻另一端接电源。这时,当短路开关短路时,pin脚读到的是0,当open时,电阻就变成了通路,pin脚读到的是1.

------------------------------------------------------

------------------------------------------------------ ------------------------------------------------------------

------------------------------------------------------------

下拉电阻类推

官方说明中,对于上拉电阻的作用是这么讲的:

1、当TTL电路驱动CMOS电路时,如果电路输出的高电平低于CMOS电路的最低高电平(一般为3.5V), 这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

2、OC门电路必须使用上拉电阻,以提高输出的高电平值。

3、为增强输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

4、在CMOS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻以降低输入阻抗, 提供泄荷通路。

5、芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限,增强抗干扰能力。

6、提高总线的抗电磁干扰能力,管脚悬空就比较容易接受外界的电磁干扰。

7、长线传输中电阻不匹配容易引起反射波干扰,加上、下拉电阻是电阻匹配,有效的抑制反射波干扰。

一种简洁的理解方式:

上拉电阻是用来解决总线驱动能力不足时提供电流的问题的。一般说法是上拉增大电流,下拉电阻是用来吸收电流。

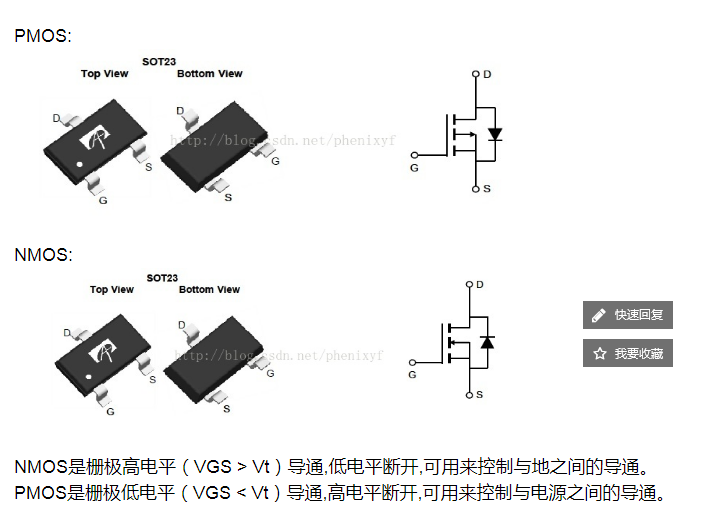

PMOS,NMOS,CMOS

MOS管包括PMOS,NMOS

CMOS是互补金属氧化物半导体,是由PMOS和NMOS互补共同构成的MOS集成电路

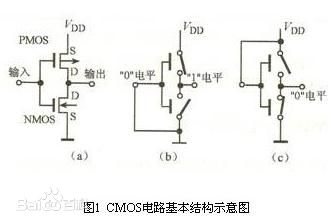

由于两管栅极工作电压极性相反,故将两管栅极相连作为输入端,两个漏极相连作为输出端,如图1(a)所示,则两管正好互为负载,处于互补工作状态。

当输入低电平(Vi=Vss)时,PMOS管导通,NMOS管截止,输出高电平,如图1(b)所示。

当输入高电平(Vi=VDD)时,PMOS管截止,NMOS管导通,输出为低电平,如图1(c)所示。

两管如单刀双掷开关一样交替工作,构成反相器(互补工作状态)

而与非门和或非门还有非门则是由CMOS来构造的。详见《数字设计原理与实践》P62

CMOS和TTL

一:TTL

TTL集成电路的主要型式为晶体管-晶体管逻辑门(Transistor-Transistor Logic gate),TTL采用5V电源。- 输出高电平Uoh和输出低电平Uol

Uoh≥2.4V, Uol≤0.4V

在室温下,一般输出高电平为3.5V - 输出高电平Uih和输出低电平Uil

Uih≥2.0V, Uol≤0.8V - 噪声容限0.4V

噪声容限计算:噪声容限=min{高电平噪声容限,低电平噪声容限}

高电平噪声容限=最小输出高电平电压-最小输入高电平电压

低电平噪声容限=最大输入低电平电压-最大输出低电平电压

二: CMOS

CMOS电路是电压控制器件,输入电阻极大,对于干扰信号十分敏感,因此不用的输入端不应开路,接到地或者电源上。CMOS电路的优点是噪声容限较宽,静态功耗很小。CMOS采用5~15V电源, 另外, 只有 4000 系列的 CMOS 器件可以工作在15V电源下, 74HC, 74HCT 等都只能工作在 5V电源下, 现在已经有工作在 3V和 2.5V电源下的 CMOS 逻辑电路芯片了.

- 输出高电平Uoh和输出低电平Uol

Uoh≈VCC, Uol≈GND - 输出高电平Uih和输出低电平Uil

Uih≥0.7VCC, Uol≤0.2VCC (VCC为电源电压,GND为地)

从上面可以看出:

在同样5V电源电压情况下,COMS电路可以直接驱动TTL,因为CMOS的输出高电平VCC=5V大于2.0V,输出低电平GND=0V小于0.8V;而TTL电路则不能直接驱动CMOS电路,TTL的输出高电平为大于2.4V,如果落在2.4V~3.5V之间,则CMOS电路就不能检测到高电平,低电平小于0.4V满足要求,所以在TTL电路驱动COMS电路时需要加上拉电阻。如果出现不同电压电源的情况,也可以通过上面的方法进行判断

三:TTL和COMS电路比较:

-

TTL电路是电流控制器件,而CMOS电路是电压控制器件。

-

TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。COMS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。COMS电路本身的功耗与输入信号的脉冲频率有关,频率越高,芯片集越热,这是正常现象。

- COMS电路的使用注意事项

1) COMS电路时电压控制器件,它的输入总抗很大,对干扰信号的捕捉能力很强。所以,不用的管脚不要悬空,要接上拉电阻或者下拉电阻,给它一个恒定的电平。

2) 输入端接低内阻的信号源时,要在输入端和信号源之间要串联限流电阻,使输入的电流限制在1mA之内。

3) 当接长信号传输线时,在COMS电路端接匹配电阻。

4) 当输入端接大电容时,应该在输入端和电容间接保护电阻。电阻值为R=V0/1mA.V0是外界电容上的电压。

5) COMS的输入电流超过1mA,就有可能烧坏COMS。 - TTL门电路中输入端负载特性(输入端带电阻特殊情况的处理):

1)悬空时相当于输入端接高电平。因为这时可以看作是输入端接一个无穷大的电阻。

2)在门电路输入端串联10K电阻后再输入低电平,输入端出呈现的是高电平而不是低电平。因为由TTL门电路的输入端负载特性可知,只有在输入端接的串联电阻小于910欧 时,它输入来的低电平信号才能被门电路识别出来,串联电阻再大的话输入端就一直呈现高电平。这个一定要注意。COMS门电路就不用考虑这些了。

四:OC门与OD门

-

OC(Open Collector)门,即集电极开路门电路(Open Collector),OD(Open Drain)门,即漏极开路门电路,必须外界上拉电阻和电源才能将开关电平作为高低电平用。

-

TTL电路有集电极开路OC门,MOS管也有和集电极对应的漏极开路的OD门,它的输出就叫做开漏输出。OC门在截止时有漏电流输出,那就是漏电流,为什么有漏电流呢?那是因为当三极管截止的时候,它的基极电流约等于0,但是并不是真正的为0,经过三极管的集电极的电流也就不是真正的 0,而是约0。而这个就是漏电流。

-

开漏输出:OC门的输出就是开漏输出;OD门的输出也是开漏输出。它可以吸收很大的电流,但是不能向外输出的电流。所以,为了能输入和输出电流,它使用的时候要跟电源和上拉电阻一齐用。OD门一般作为输出缓冲/驱动器、电平转换器以及满足吸收大负载电流的需要。

-

为什么引入OC门?

实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态电平)用同一条导线输送出去。因此,需要一种新的与非门电路–OC门来实现“线与逻辑”。

五:有关逻辑电平的一些概念

要了解逻辑电平的内容,首先要知道以下几个概念的含义:

- 输入高电平(Vih):保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于Vih时,则认为输入电平为高电平。

- 输入低电平(Vil):保证逻辑门的输入为低电平时所允许的最大输入低电平,当输入电平低于Vil时,则认为输入电平为低电平。

- 输出高电平(Voh):保证逻辑门的输出为高电平时的输出电平的最小值,逻辑门的输出为高电平时的电平值都必须大于此Voh。

- 输出低电平(Vol):保证逻辑门的输出为低电平时的输出电平的最大值,逻辑门的输出为低电平时的电平值都必须小于此Vol。

- 阀值电平(Vt):数字电路芯片都存在一个阈值电平,就是电路刚刚勉强能翻转动作时的电平。它是一个界于Vil、Vih之间的电压值,对于CMOS电路的阈值电平,基本上是二分之一的电源电压值,但要保证稳定的输 出,则必须要求输入高电平> Vih,输入低电平

对于一般的逻辑电平,以上参数的关系如下:Voh > Vih > Vt > Vil > Vol