#===============================================================

#Analysi&Synthesis

execute_module -tool map

#===============================================================

#Fitter(Place&Route)

execute_module -tool fit

#===============================================================

#Assembler(Generate programming files)

execute_module -tool asm

set make_assignments 0

if { $make_assignments } {

set_global_assignment -name FAMILY "Cyclone V"

set_global_assignment -name DEVICE 5CEFA5F23I7

set_global_assignment -name TOP_LEVEL_ENTITY altera_wireless_top

set_global_assignment -name RESERVE_ALL_UNUSED_PINS_WEAK_PULLUP "AS INPUT TRI-STATED"

set_global_assignment -name EDA_SIMULATION_TOOL "ModelSim (Verilog)"

#添加verilog文件

set_global_assignment -name VERILOG_FILE hb_i2_5m_4ch_16x.v

set_global_assignment -name QIP_FILE fir_23p04_4x_linux_ipv2/fir_23p04_4x_linux_ip.qip

set_global_assignment -name SIGNALTAP_FILE ad_test0806v2.stp

set_global_assignment -name TEXT_FILE output_files/stp1_auto_signaltap_0.txt

##===============SYSCLK=============================================================================

set_location_assignment PIN_M8 -to clk_n

set_location_assignment PIN_M9 -to clk_p

set_instance_assignment -name IO_STANDARD "DIFFERENTIAL 2.5-V SSTL CLASS II" -to clk_n

set_instance_assignment -name IO_STANDARD "DIFFERENTIAL 2.5-V SSTL CLASS II" -to clk_p

}

感觉TCL中if else语句在用的时候是注意空格间隔等问题的,如果执行过程报错,就严格按下面的写法来用。

set broken 0

if { $broken } {

puts "failure -- exit status $broken"

exit -code $broken

} else {

puts "success"

}

/*********************************************************************************/

1、设置路径

cd命令用于更改modelsim的路径,如果仿真正在执行cd命令无效;如果找开了一个工程,那cd命令会关闭当前的工程

语法:cd <dir>

eg:cd e:/fpga

/*********************************************************************************/

2、alias 显示和建立用户定义的别名,有点相当于c语言中的“宏定义”

Syntax

alias [<name> ["<cmds>"]]

当cmds为多组命令时用”;“分开,并且用双引号

eg: alias ld "dev_com;com;elab"

eg2:

alias dev_com {

if [ string match "*ModelSim*" [ vsim -version ] ] {

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_primitives.v" -work altera_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/220model.v" -work lpm_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/sgate.v" -work sgate_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_mf.v" -work altera_mf_ver

vlog -sv "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/altera_lnsim_for_vhdl.sv" -work altera_lnsim_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_atoms_ncrypt.v" -work cyclonev_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_hmi_atoms_ncrypt.v" -work cyclonev_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_atoms_for_vhdl.v" -work cyclonev_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_hssi_atoms_ncrypt.v" -work cyclonev_hssi_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_hssi_atoms_for_vhdl.v" -work cyclonev_hssi_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_pcie_hip_atoms_ncrypt.v" -work cyclonev_pcie_hip_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_pcie_hip_atoms_for_vhdl.v" -work cyclonev_pcie_hip_ver

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_syn_attributes.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_standard_functions.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/alt_dspbuilder_package.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_europa_support_lib.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_primitives_components.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_primitives.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/220pack.vhd" -work lpm

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/220model.vhd" -work lpm

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/sgate_pack.vhd" -work sgate

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/sgate.vhd" -work sgate

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_mf_components.vhd" -work altera_mf

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_mf.vhd" -work altera_mf

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_lnsim_components.vhd" -work altera_lnsim

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/cyclonev_atoms.vhd" -work cyclonev

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/cyclonev_components.vhd" -work cyclonev

}

}

这样的话,在modelsim的命令窗输入dev_com,就会执行所有的编译文件命令。

/*********************************************************************************/

echo 在脚本框中输出指定的内容

Syntax

echo [<text_string>]

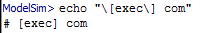

如上图,在modelsim的命令行中输入ech "exec] com" 就会输出 #[exec] com,其实就相关于matlab 中的output命令

/*********************************************************************************/

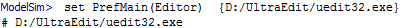

eidt

上面的命令用于设置modelsim的文件编辑器

Syntax

edit [<filename>]

[<filename>]用于指定要编辑文件的名字

在命令窗中输入help

可以看到哪些Tcl包已经下载,哪些还没有。Loaded表示已经下载,Not Loaded表示还没有下载

输入help –tcl

输入 help flow如下: