1. 概述

SPI = Serial Peripheral Interface,是串行外围设备接口,是一种高速,全双工,同步的通信总线。常规只占用四根线,节约了芯片管脚,PCB的布局省空间。现在越来越多的芯片集成了这种通信协议,常见的有EEPROM、FLASH、AD转换器等。

优点:

支持全双工,push-pull的驱动性能相比open-drain信号完整性更好;

支持高速(100MHz以上);

协议支持字长不限于8bits,可根据应用特点灵活选择消息字长;

硬件连接简单;

缺点:

相比IIC多两根线;

没有寻址机制,只能靠片选选择不同设备;

没有从设备接受ACK,主设备对于发送成功与否不得而知;

典型应用只支持单主控;

相比RS232 RS485和CAN总线,SPI传输距离短;

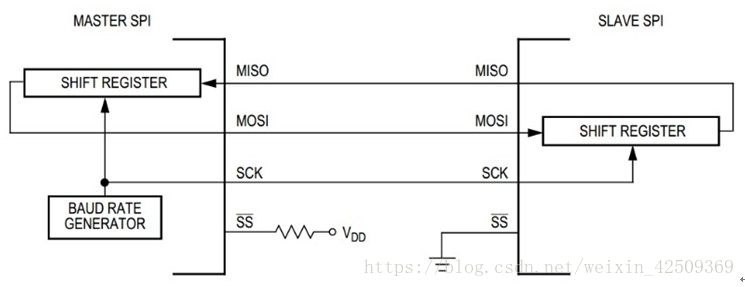

2. 硬件结构

SPI总线定义两个及以上设备间的数据通信,提供时钟的设备为主设备Master,接收时钟的设备为从设备Slave;

信号定义如下:

SCK : Serial Clock 串行时钟

MOSI : Master Output, Slave Input 主发从收信号

MISO : Master Input, Slave Output 主收从发信号

SS/CS : Slave Select 片选信号

电路连接如下:

单个主设备和单个从设备:

单个主设备和多个从设备,通过多个片选信号或者菊花链方式实现:

3. 寄存器类型

Motorola定义的SPI寄存器包括:

SPI Control Register 1 (SPICR1) 控制寄存器1

SPI Control Register 2 (SPICR2) 控制寄存器2

SPI Baud Rate Register (SPIBR) 波特率寄存器

SPI Status Register (SPISR) 状态寄存器 (只读 其余均可读可写)

SPI Data Register (SPIDR) 数据寄存器

通过往寄存器中写入不同的值,设置SPI模块的不同属性。

4. SPI传输模式

通过设置控制寄存器SPICR1中的CPOL和CPHA位,将SPI可以分成四种传输模式。

CPOL,即Clock Polarity,决定时钟空闲时的电平为高或低。对于SPI数据传输格式没有显著影响。

1 = 时钟低电平时有效,空闲时为高

0 = 时钟高电平时有效,空闲时为低

CPHA,即Clock Phase,定义SPI数据传输的两种基本模式。

1 = 数据采样发生在时钟(SCK)偶数(2,4,6,...,16)边沿(包括上下边沿)

0 = 数据采样发生在时钟(SCK)奇数(1,3,5,...,15)边沿(包括上下边沿)

四种模式如下图所示:

先看第一列两张图(CPHA = 0),采样发生在第一个时钟跳变沿,即数据采样发生在SCK奇数边沿;再看第二列(CPHA =1),采样发生在第二个时钟跳变沿,即数据采样发生在SCK偶数边沿。

第一行两张图,第二行两张图(CPOL = 1),SCK空闲状态为高电平。

主从设备进行SPI通讯时,要确保它们的传输模式设置相同。

其中mode0和mode3最为常见,SPI接口的flash中均会有标注。

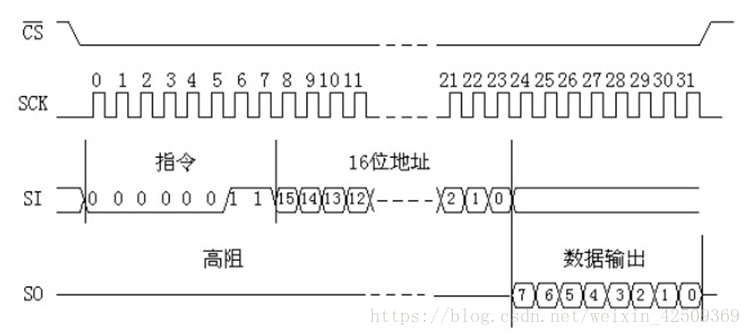

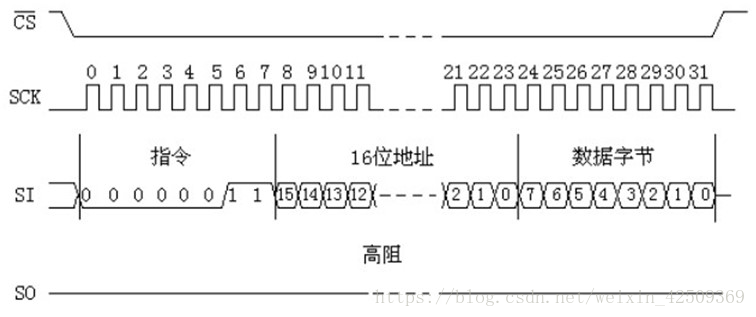

5. 读写操作

标准SPI读写为例

片选---读指令---地址---数据读出

片选---写指令---地址---数据写入

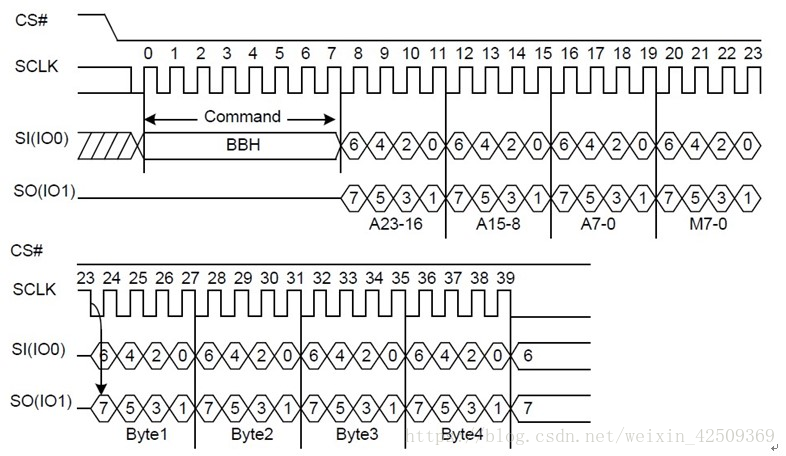

Dual I/O Fast Read Sequence Diagram 双路IO

Quad I/O Fast Read Sequence Diagram 四路IO

与IIC一样,是一种最常见的板内芯片间的串行接口。

————————————————

版权声明:本文为CSDN博主「千里沽山」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/weixin_42509369/article/details/83096349