最近在群里又受教育了,很开心。多谢awey和缥缈九哥指教。

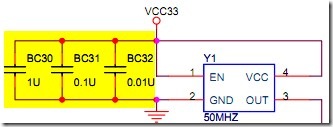

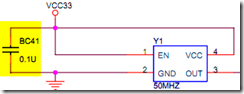

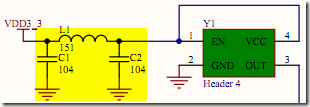

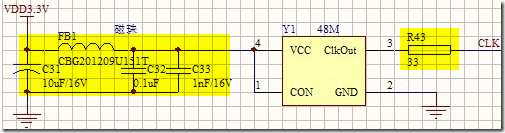

下面几个是FPGA开发板使用的晶振。加滤波,是为了防止振荡器干扰电源。电源稳定,振荡器的频率较高,用一个104电容去耦就够了,如图2所示。图3使用的π型滤波器,由一个电感器两个电容器构成,它的输入端和输出端都呈低阻抗性,因为元件比L或C型多,故抑制性能要好的多。

图1 Cyclone III Start Kit 时钟电路

图2 DE1 时钟电路

图3 艾米电子EP2C8 FPGA开发板 时钟电路

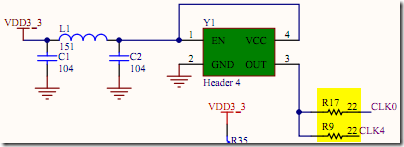

再看下面的有源晶振的输出端,串电阻。芯片的输入端有输入电容,走线也有分布电容,没这个电阻,振荡器输出的上下沿有冲击电流,产生辐射。特别是阻抗不匹配时,高频信号会反射回来干扰信号源。串上电阻,能消除反射波的影响。

图4

图5