本节内容:为什么使用随机化,随机化选项,随机化的object等等

一:随机化的目的

1:随机测试与直接测试

激励产生是验证中很重要的一个组成部分,激励产生有下面几种可选方法。

1)直接测试

2)直接随机测试

3)随机测试

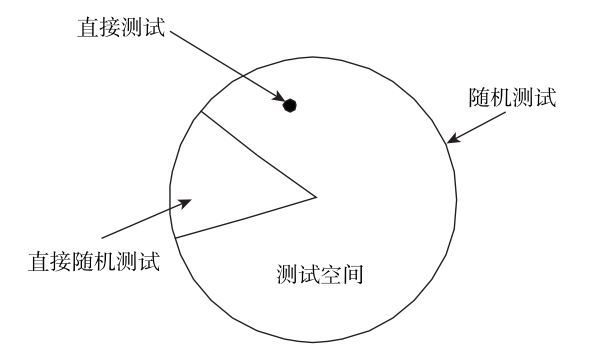

每种激励产生策略所覆盖的测试空间的范围是不一样的。如下图所示:

直接测试比较适合简单的设计,因为其测试空间小,可以通过一定数目的测试即可覆盖到。直接测试也可以用来测试复杂设计中的简单功能点,特别是某些可能潜在缺陷的边界条件;可以单独采用直接测试或者其他测试混合在一起。例如:复杂设计中的奇偶错误检测功能可以通过用直接测试检验,可以独立测试或者混合在顶层的随机测试中。

随机测试可以应用在任何类型的设计中, 特别是在设计具有比较大的测试空间或者数量较多的交互情景。 通过采用随机测试可以击中一些期望的功能点是很重要的一个功能, 因为验证工程师未必都可以罗列出所有的功能点。 随机测试可以创建一些异常并发或者异步的事件, 从而测试设计中的某些独特、 复杂的行为 。

二:随机化

1:生成机制

1)采用sv内置的系统函数来产生随机数

2)randcase和randsequence结构来实现随机的分支选择

3)基于对象的随机生成,随机地初始化对象地数据成员的值

4)标准随机函数std:randomize()可以随时对任意变量进行随机化并添加约束

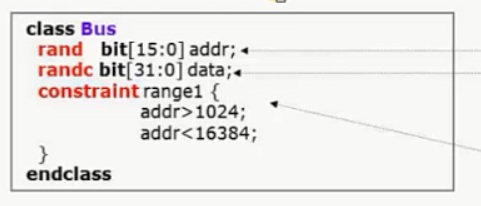

2:随机关键字

1)rand

rand bit[7:0] y; //随机产生一个8bit无符号数据,0-255

2)randc:循环随机给出

randc bit[1:0] y; //随机产生一个2bit的无符号数据,0-3循环

3:randomize()

检查随机是否成功函数,rand成功,返回1,不成功,返回0;

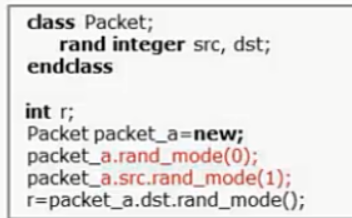

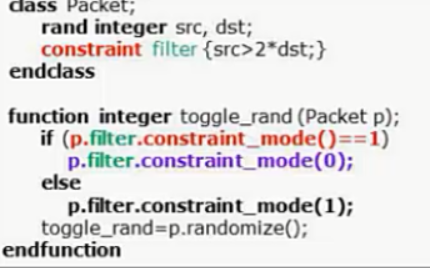

4:关闭随机:rand_mode

rand_mode(0) :关闭随机

rand_mode(1): 打开随机

三:对随机数据进行约束(constraint)

1:简单constraint块如下所示:约束的变量必须是randm的,没有顺序性

2:随机表达式

可以使用<,<=,==,>=,>符号,一句表达式里只能有一个操作符

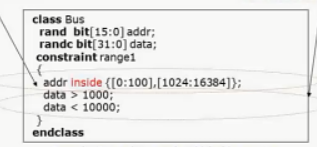

3:inside操作符

范围操作符,如下:

4:条件约束(->)

5:迭代约束

约束块里可以使用foreach循环

6:函数约束

约束里可添加函数;函数不能包含输出,ref;函数必须是automatic;

7:关闭约束: constraint_mode()

constraint_mode(0):关闭约束

constraint_mode(1):打开约束

四:随机的概率与分配权重

1:权重

默认权重相同,可以使用 := 或者:/来分配权重;

![]()

:=与:/之间的区别,如下图

2:概率

无约束时,随机值出现的概率是相同的;加上约束时,随机值出现的概率不同;条件约束时,条件与结果的不同,概率也是不同的(条件与结果既然有约束关系,则不独立);