推荐:NXP官方软件config tool,图形化界面可导出代码

K60芯片的时钟系统由振荡器(OSC)、实时振荡器(RTC OSC)、多功能时钟发生器(MCG)、系统集成模块(SIM)和电源管理器(PMC)等模块组成。

内核时钟(系统时钟)=外部时钟(50M晶振频率)/ (pll_prdiv+1)*(pll_vdiv+24); MCG=PLL, core = MCG, bus = MCG/2, FlexBus = MCG/3, Flash clock= MCG/8

https://blog.csdn.net/hcx25909/article/details/7164650

飞思卡尔K60时钟系统如上图所示,可以发现器件的源时钟源一共有4个:

①内部参考时钟源,包括 Fast IRC和 slow IRC (IRC--Internal Reference Clock)

②外部参考时钟源,只一个EXTAL管脚作为时钟输入,这个可以使用有源晶体振荡器来实现

③外部晶体谐振器,使用EXTAL和XTAL两个管脚来输入

④外部32K RTC 谐振器,用于实时时钟的时钟输入

在图中可以看到,要为系统提供时钟信号,关键是要最终生成 MCGOUTCLK 输出。MCGOUTCLK 再经过分频便可以提供Core/system clocks、Bus clock、FlexBus clock和Flash clock。MCGOUTCLK 的产生有3个途径:

①由内部参考时钟源 Fast IRC 直接提供,这个时钟源集成在芯片的内部(包括Slow IRC),频率是2M

②由 FLL 或者 PLL 模块来提供

③由外部时钟来直接提供,包括外部参考时钟源(1个管脚输入)、外部晶体谐振器经内部OSC logic产生的XTAL_CLK 和 RTC OSC logic 的时钟输出。

一般情况下,MCGOUTCLK 是由PLL或者FLL倍频来产生的,飞思卡尔官方的例程最终是由PLL模块来产生。图中可以看到PLL模块的时钟输入是OSCCLK或者RTC OSC logic。我的板子以外部参考时钟源提供PLL时钟,最终经PLL倍频产生MCGOUTCLK。即 EXTAL-->PLL模块-->MCGOUTCLK.

2.关于时钟模式

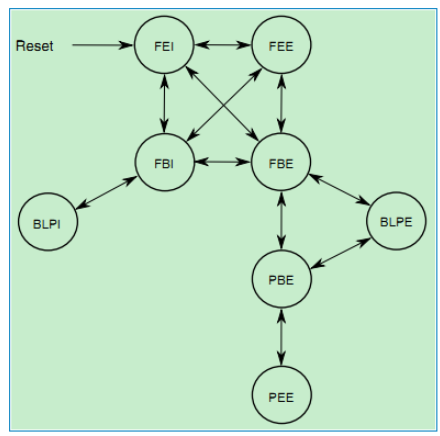

从图中可以看到,该芯片一共包含8种工作时钟模式,外加Stop模式。系统在RESET后直接进入默认的FEI模式。图中,F--FLL、P--PLL、E--Enable或者EXTAL(外部时钟)、B--Bypass(旁路)、I--Internal(内部参考时钟)、L--Low Power.

·FLL 启用、内部参考时钟(FEI), 内部参考时钟提供FLL的时钟,FLL驱动MCGOUT

·FLL 启用、外部参考时钟(FEE), 外部参考时钟提供FLL的时钟,FLL驱动MCGOUT

·FLL 旁路、内部参考时钟(FBI),FLL虽然在运作但由内部时钟参考源驱动MCGOUT

·FLL 旁路、外部参考时钟(FBE),FLL虽然在运作但由外部时钟参考源驱动MCGOUT

·PLL 旁路、外部参考时钟(PBE),PLL虽然在运作但由外部时钟参考源驱动MCGOUT

·PLL 启用、外部参考时钟(PEE),外部参考时钟提供PLL的时钟,PLL驱动MCGOUT

·BLPI FLL和PLL都禁用,内部时钟参考源驱动MCGOUT

·BLPE FLL和PLL都禁用,外部时钟参考源驱动MCGOUT

由于系统在重启后默认进入FEI模式,我们的目标是要跳到PEE模式,所以要涉及到模式的转化。图中由FEI到PEE是不能直接跳转的,必须经由其他模式来转换