https://mp.weixin.qq.com/s/H2UBmZa9fpM6_FM2_MucTQ

实现一个SoC作为顶层模块,包含Cpu、Mem两个子模块,并驱动运行。

参考链接

1.创建Soc.java, 并生成构造方法和logic()方法

略

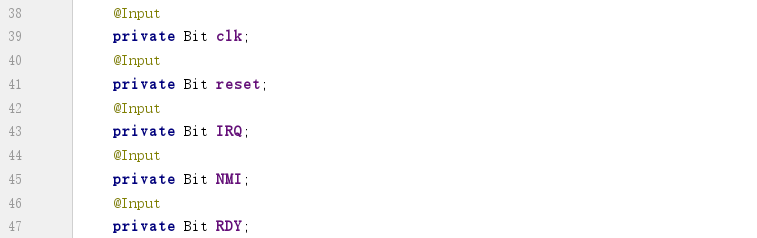

2. 根据逻辑原理,添加输入输出接口

输入输出线作为类成员存在。使用注解标明是input port还是output port。

内部模块和信号:

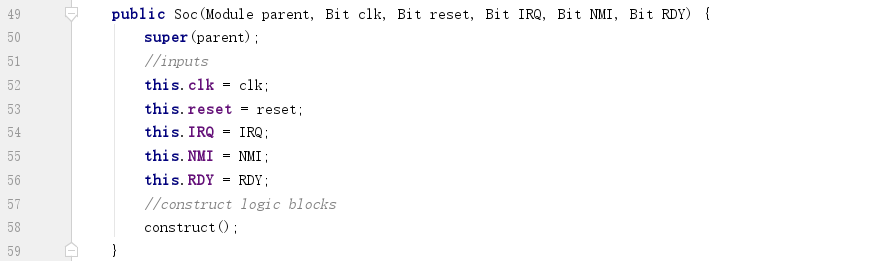

3. 在构造方法中搜集输入输出线并调用construct()方法

首先调用父类即Module类的构造方法,以构建模块hierarchy。

然后逐个把输入输出参数与input/output port对应上。

然后调用construct()方法构造模块(调用一次logic()方法,搜集模块的assign/always代码块、子模块)。

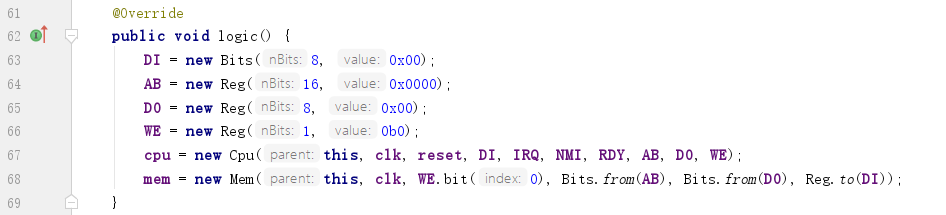

4. 在logic()方法中创建assign/always代码块,以及子模块

5. 创建inst静态方法方便后续使用

略

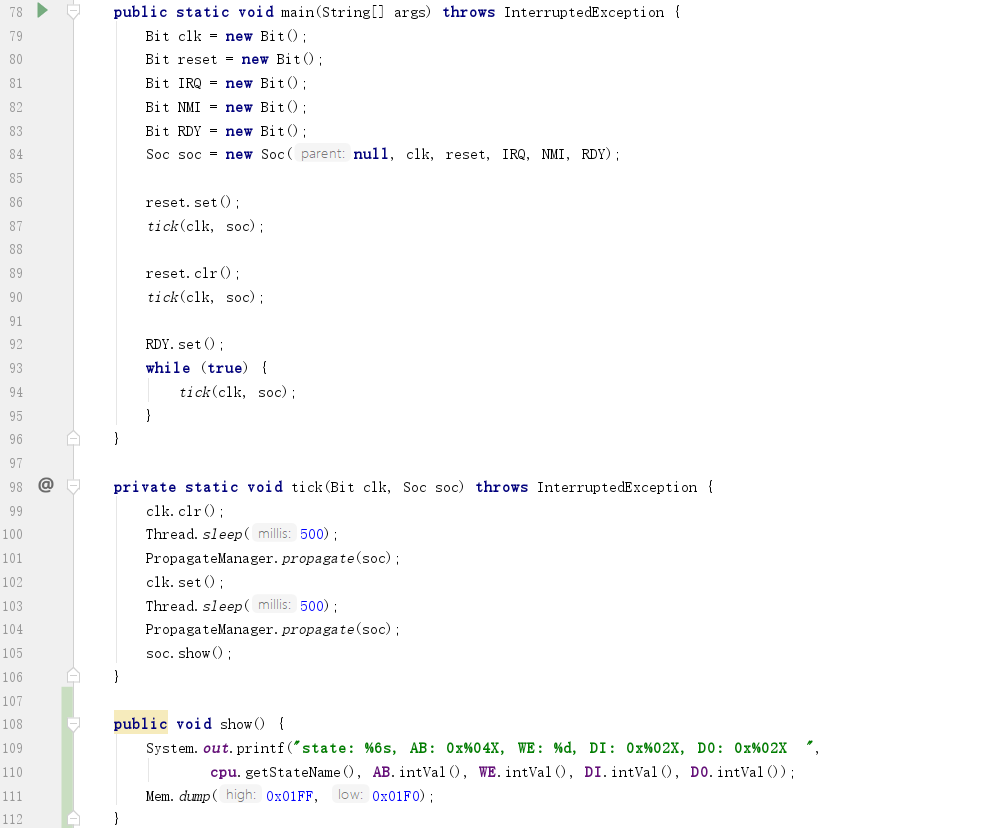

6. 创建main方法执行验证

SoC只需要复位后不停地驱动时钟跳动,CPU的状态机即可运行,从Mem中取得指令,并按照指令执行。

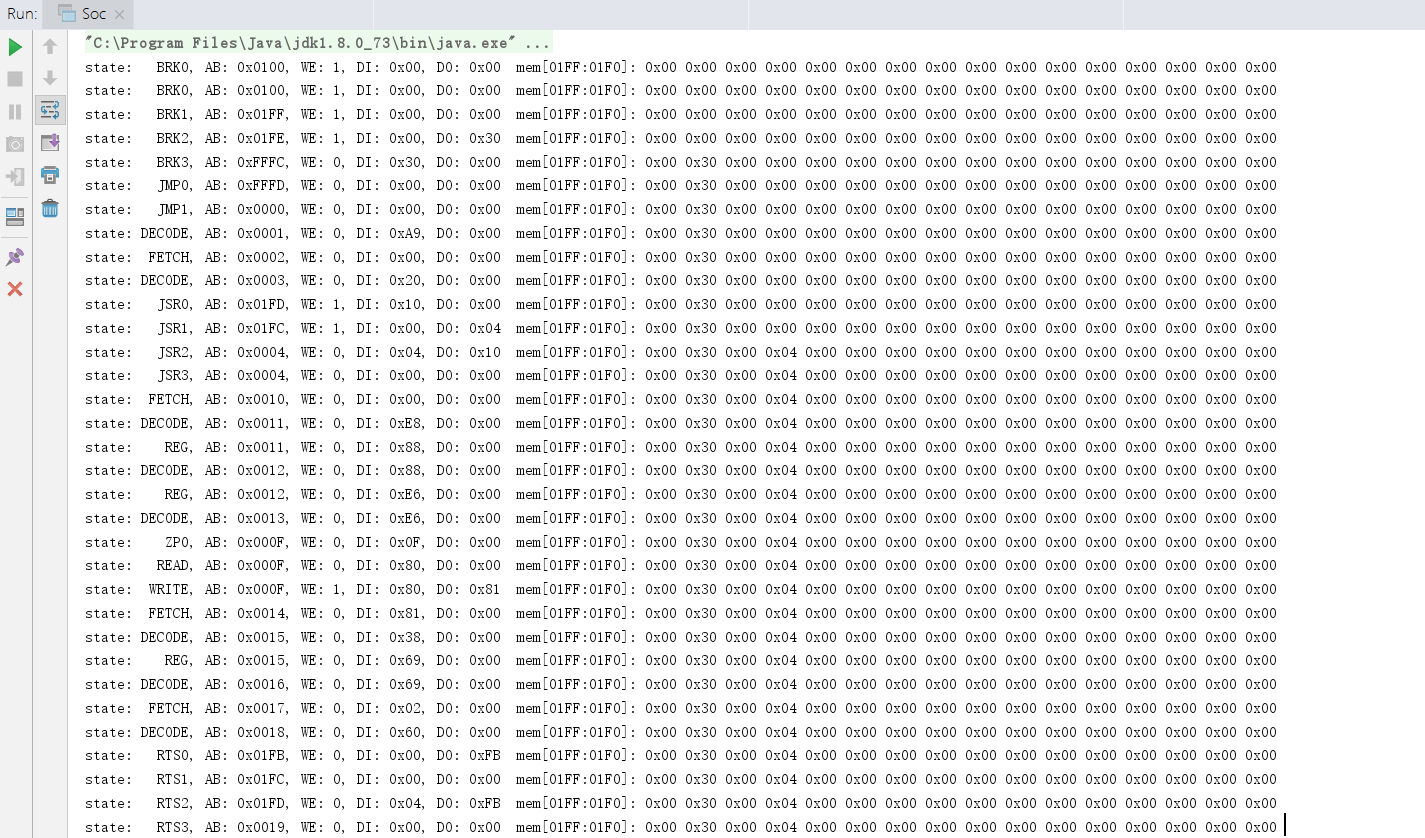

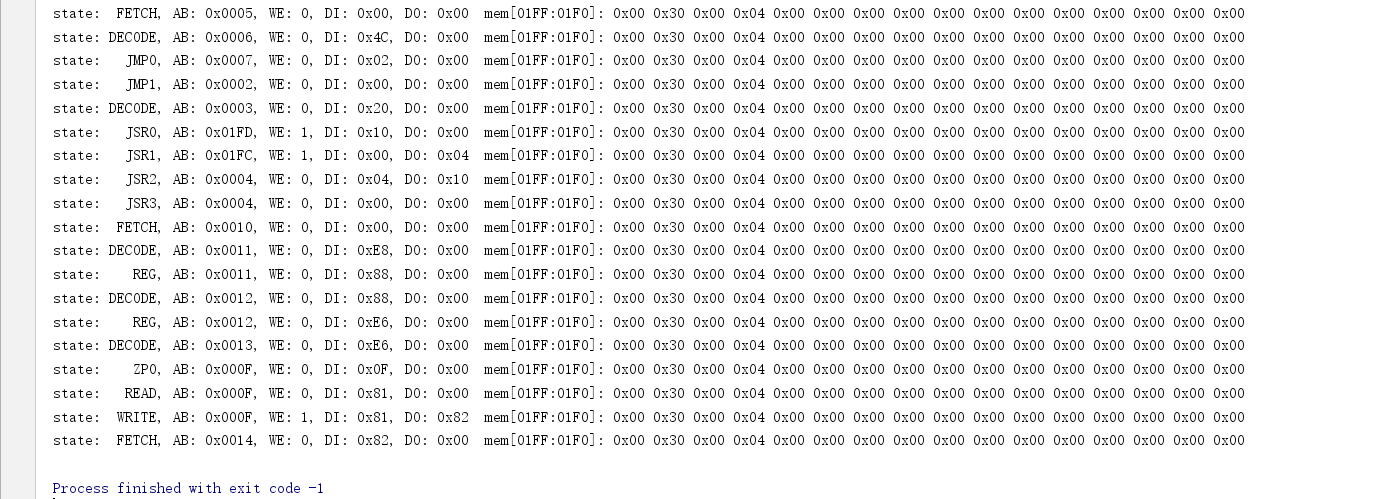

运行结果为:

这是定义在Mem中的一段代码运行时,CPU状态机的变化,以及部分内存值的变化。

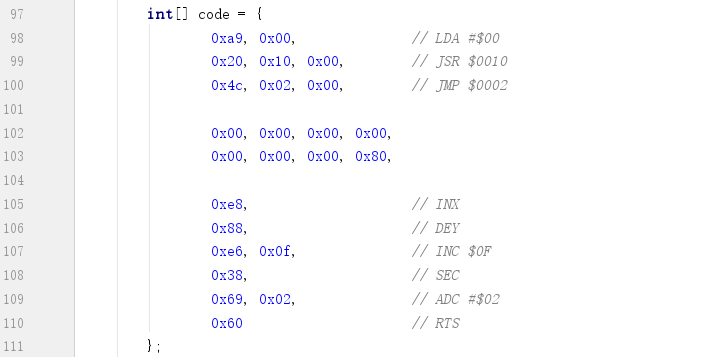

代码如下(可以参考Mem模块):

这段代码跳到一个子程序$0010(JSR $0010),执行几个指令,然后返回(RTS)。返回之后执行跳转指令(JMP $0002),再一次跳到子程序$0010,如此循环下去。

7. 生成Verilog

生成定制化模块名:

略

调用toVerilog()方法生成Verilog实现。

略

执行结果如下:

略