https://mp.weixin.qq.com/s/rI-CJM6GyI6EUHPZ3uYiFg

如同Verilog中的众多运算符,Chisel也针对自身的数据类型,提供了很多运算符。

Chisel语言内嵌于Scala。在Scala中,基本上所有的运算符都被当做一般的字符,可以作为命名符号(identifier)的一部分。并且Scala支持省略函数调用时,括在参数两边的括号。所以Scala中定义运算符重载很简单,可以很大的提高代码的可读性。

1. 运算符

参考链接:

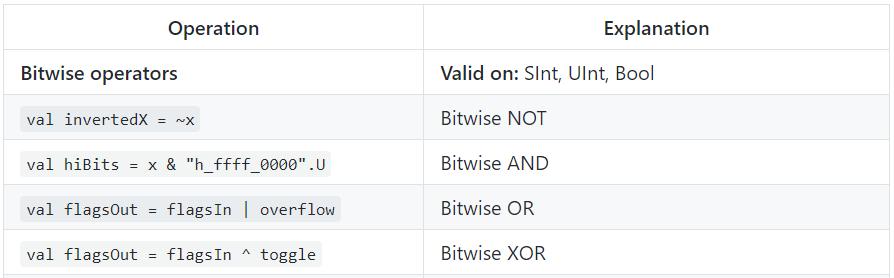

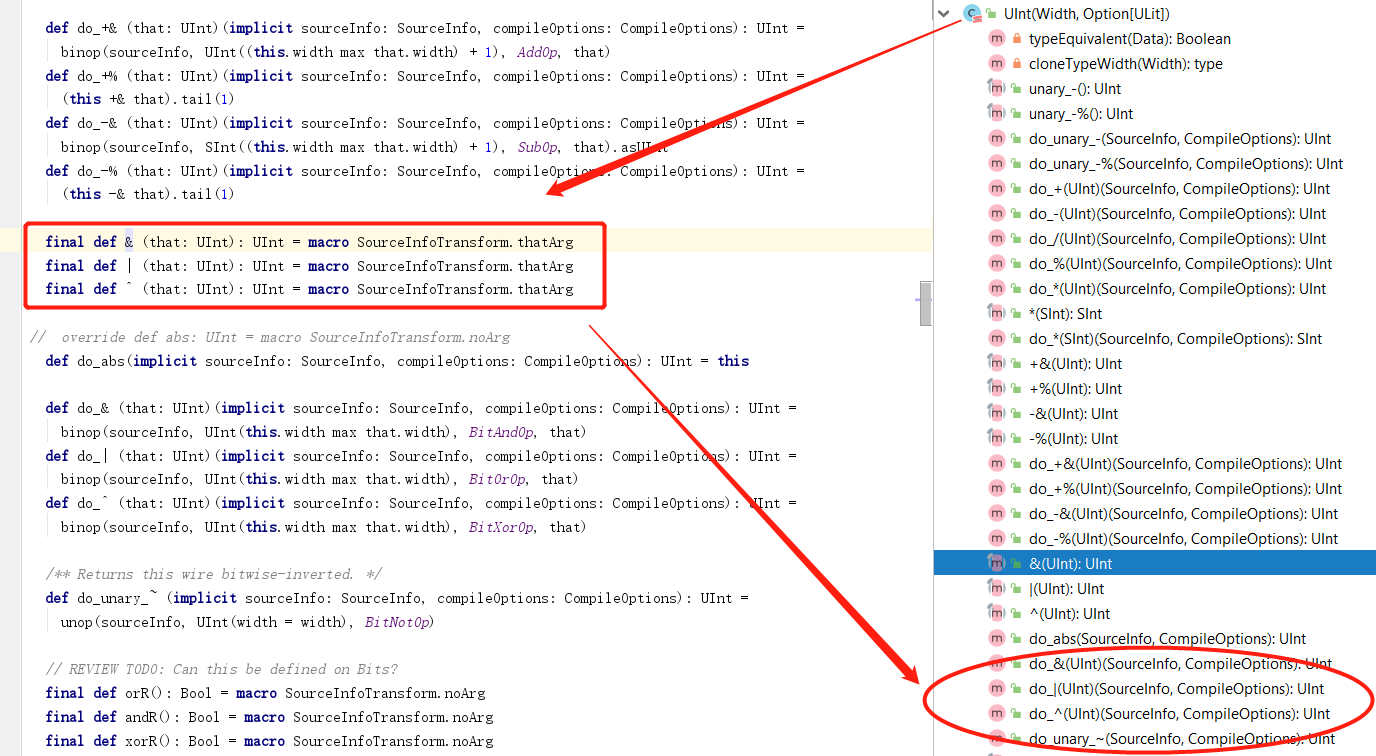

a. Bitwise operators

~ & | ^ 这些其实都是方法名,如:

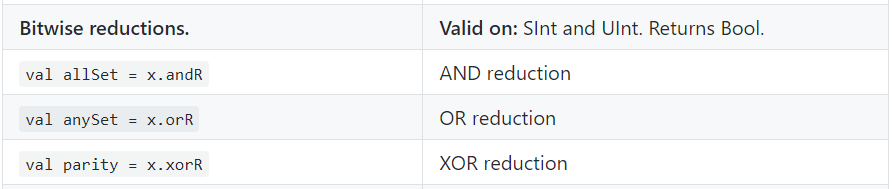

b. Bitwise reductions

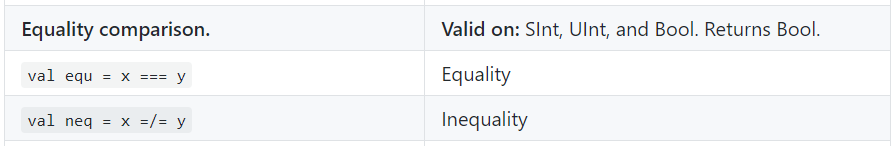

c. Equality comparison.

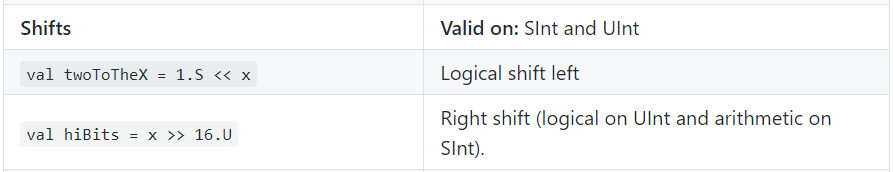

d. Shifts

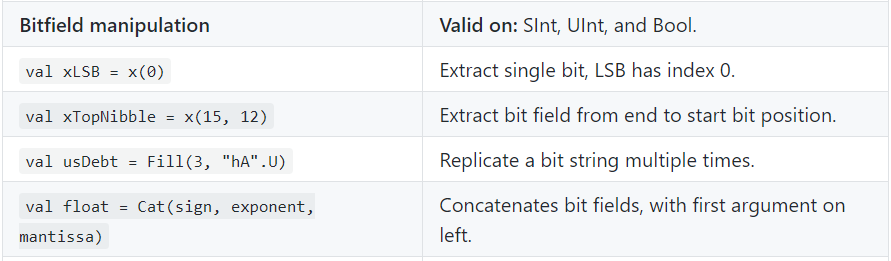

e. Bitfield manipulation

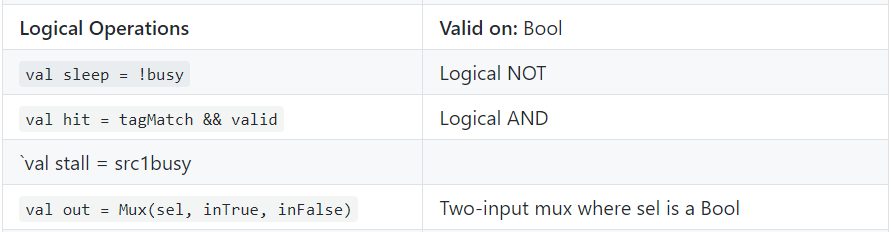

f. Logical Operations

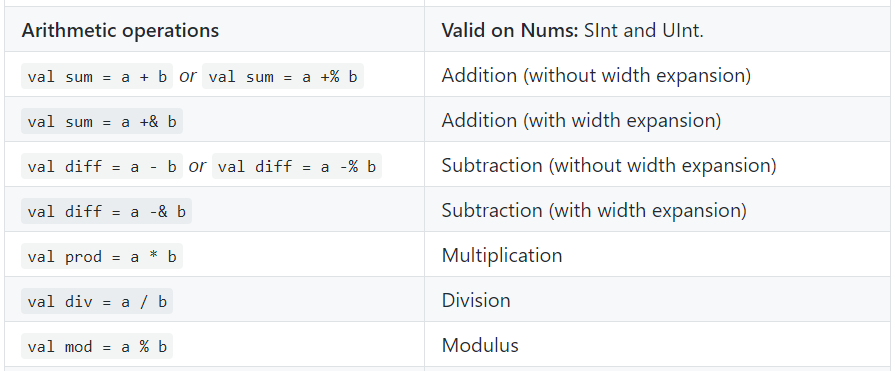

g. Arithmetic operations

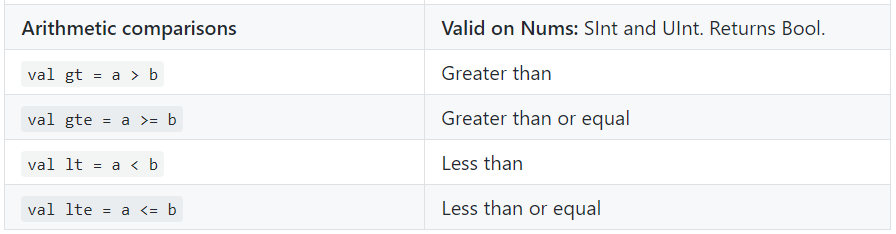

h. Arithmetic comparisons

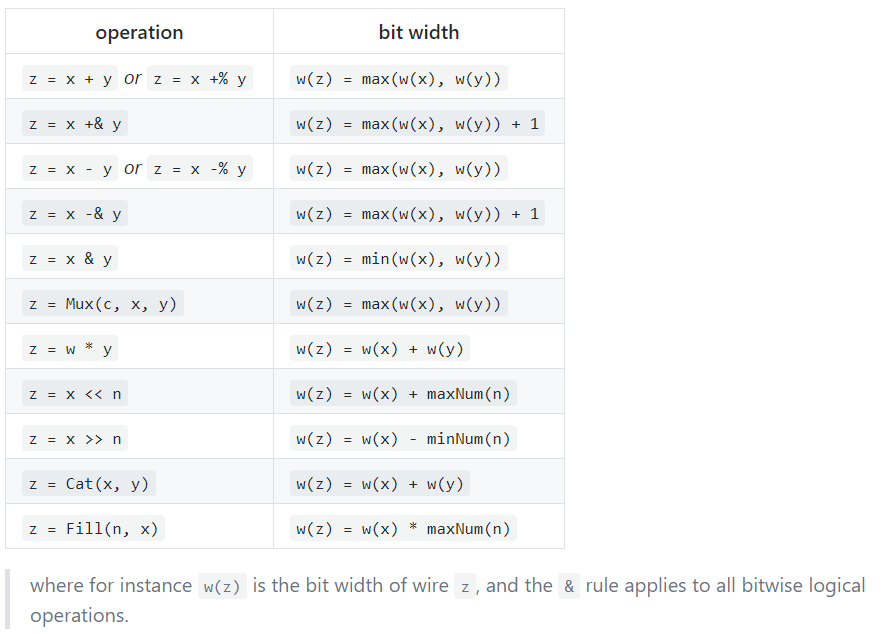

2. 位宽推断

两个相同类型但位宽不同的变量,也可以进行运算。运算参数以及运算结果的位宽会进行自动推断拓展。

参考链接:

Chisel provides bit width inference to reduce design effort. Users are encouraged to manually specify widths of ports and registers to prevent any surprises, but otherwise unspecified widths will be inferred by the Firrtl compiler.

For all circuit components declared with unspecified widths, the FIRRTL compiler will infer the minimum possible width that maintains the legality of all its incoming connections. Implicit here is that inference is done in a right to left fashion in the sense of an assignment statement in chisel, i.e. from the left hand side from the right hand side. If a component has no incoming connections, and the width is unspecified, then an error is thrown to indicate that the width could not be inferred.

For module input ports with unspecified widths, the inferred width is the minimum possible width that maintains the legality of all incoming connections to all instantiations of the module. The width of a ground-typed multiplexor expression is the maximum of its two corresponding input widths. For multiplexing aggregate-typed expressions, the resulting widths of each leaf subelement is the maximum of its corresponding two input leaf subelement widths. The width of a conditionally valid expression is the width of its input expression. For the full formal description see the Firrtl Spec.