整理下之前的笔记:简谈推挽电路

要理解推挽输出,首先要理解好三极管(晶体管)的原理。下面这种三极管有三个端口,分别是基极(Base)、集电极(Collector)和发射极(Emitter)。下图是NPN型晶体管。

![]()

这种三极管是电流控制型元器件,注意关键词电流控制。意思就是说,只要基极B有输入(或输出)电流就可以对这个晶体管进行控制了。

下面请允许我换一下概念,把基极B视为控制端,集电极C视为输入端,发射极E视为输出端。这里输入输出是指电流流动的方向。

![]()

当控制端有电流输入的时候,就会有电流从输入端进入并从输出端流出。

而PNP管正好相反,当有电流从控制端流出时,就会有电流从输入端流到输出端。

![]()

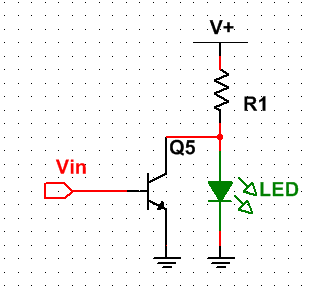

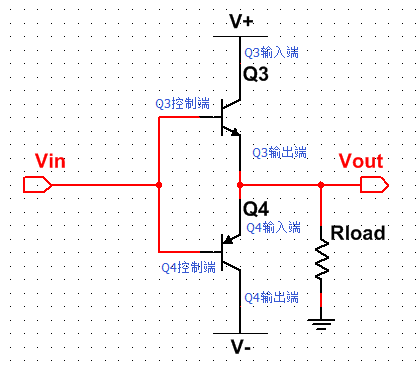

那么推挽电路:

上面的三极管是N型三极管,下面的三极管是P型三极管,请留意控制端、输入端和输出端。

当Vin电压为V+时,上面的N型三极管控制端有电流输入,Q3导通,于是电流从上往下通过,提供电流给负载。

经过上面的N型三极管提供电流给负载(Rload),这就叫「推」。

当Vin电压为V-时,下面的三极管有电流流出,Q4导通,有电流从上往下流过。

![]()

经过下面的P型三极管提供电流给负载(Rload),这就叫「挽」。

以上,这就是推挽(push-pull)电路。

那么什么是开漏呢?这个在我答案一开头给出的「网上资料」里讲得很详细了,我这里也简单写一下。

要理解开漏,可以先理解开集。

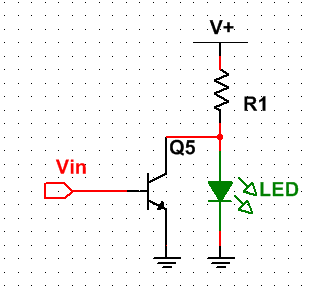

如图,开集的意思,就是集电极C一端什么都不接,直接作为输出端口。

如果要用这种电路带一个负载,比如一个LED,必须接一个上拉电阻,就像这样。

当Vin没有电流,Q5断开时,LED亮。当Vin流入电流,Q5导通时,LED灭。

开漏电路,就是把上图中的三极管换成场效应管(MOSFET)。

N型场效应管各个端口的名称:

场效应管是电压控制型元器件,只要对栅极施加电压,DS就会导通。

结型场效应管有一个特性就是它的输入阻抗非常大,这意味着:没有电流从控制电路流出,也没有电流进入控制电路。没有电流流入或流出,就不会烧坏控制电路。而双极型晶体管不同,是电流控制性元器件,如果使用开集电路,可能会烧坏控制电路。这大概就是我们总是听到开漏电路而很少听到开集电路的原因吧?因为开集电路被淘汰了。

组成开漏形式的电路有以下几个特点:

1. 利用外部电路的驱动能力,减少IC内部的驱动(或驱动比芯片电源电压高的负载)。当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。IC内部仅需很下的栅极驱动电流。如图1。

2. 可以将多个开漏输出的Pin,连接到一条线上。形成 “与逻辑” 关系。如图1,当PIN_A、PIN_B、PIN_C任意一个变低后,开漏线上的逻辑就为0了。这也是I2C,SMBus等总线判断总线占用状态的原理。如果作为输出必须接上拉电阻。接容性负载时,下降延是芯片内的晶体管,是有源驱动,速度较快;上升延是无源的外接电阻,速度慢。如果要求速度高电阻选择要小,功耗会大。所以负载电阻的选择要兼顾功耗和速度。

3. 可以利用改变上拉电源的电压,改变传输电平。如图2, IC的逻辑电平由电源Vcc1决定,而输出高电平则由Vcc2(上拉电阻的电源电压)决定。这样我们就可以用低电平逻辑控制输出高电平逻辑了(这样你就可以进行任意电平的转换)。(例如加上上拉电阻就可以提供TTL/CMOS电平输出等。)

4. 开漏Pin不连接外部的上拉电阻,则只能输出低电平(因此对于经典的51单片机的P0口而言,要想做输入输出功能必须加外部上拉电阻,否则无法输出高电平逻辑)。一般来说,开漏是用来连接不同电平的器件,匹配电平用的。

5. 标准的开漏脚一般只有输出的能力。添加其它的判断电路,才能具备双向输入、输出的能力。

6.正常的CMOS输出级是上、下两个管子,把上面的管子去掉就是OPEN-DRAIN了。这种输出的主要目的有两个:电平转换、线与。

7.线与功能主要用于有多个电路对同一信号进行拉低操作的场合,如果本电路不想拉低,就输出高电平,因为OPEN-DRAIN上面的管子被拿掉,高电平是靠外接的上拉电阻实现的。(而正常的CMOS输出级,如果出现一个输出为高另外一个为低时,等于电源短路。)

8.OPEN-DRAIN提供了灵活的输出方式,但是也有其弱点,就是带来上升沿的延时。因为上升沿是通过外接上拉无源电阻对负载充电,所以当电阻选择小时延时就小,但功耗大;反之延时大功耗小。所以如果对延时有要求,则建议用下降沿输出。

应用中需注意:

1. 开漏和开集的原理类似,在许多应用中我们利用开集电路代替开漏电路。例如,某输入Pin要求由开漏电路驱动。则我们常见的驱动方式是利用一个三极管组成开集电路来驱动它,即方便又节省成本。

2. 上拉电阻R pull-up的阻值决定了逻辑电平转换的沿的速度。阻值越大,速度越低功耗越小。反之亦然。

Push-Pull输出就是一般所说的推挽输出,在CMOS电路里面应该较CMOS输出更合适,因为在CMOS里面的push-pull输出能力不可能做得双极那么大。输出能力看IC内部输出极N管P管的面积。和开漏输出相比,push-pull的高低电平由IC的电源低定,不能简单的做逻辑操作等。push-pull是现在CMOS电路里面用得最多的输出级设计方式。

当然open drain也不是没有代价,这就是输出的驱动能力很差。输出的驱动能力很差的说法不准确,驱动能力取决于IC中的末级晶体管功率。OD只是带来上升沿的延时,因为上升沿是通过外接上拉无源电阻对负载充电的,当电阻选择小时延时就小、但功耗大,反之延时大功耗小。OPEN DRAIN提供了灵活的输出方式,但也是有代价的,如果对延时有要求,建议用下降沿输出。

电阻小延时小的前提条件是电阻选择的原则应在末级晶体管功耗允许范围内,有经验的设计者在使用逻辑芯片时,不会选择1欧姆的电阻作为上拉电阻。在脉冲的上升沿电源通过上拉无源电阻对负载充电,显然电阻越小上升时间越短,在脉冲的下降沿,除了负载通过有源晶体管放电外,电源也通过上拉电阻和导通的晶体管对地 形成通路,带来的问题是芯片的功耗和耗电问题。电阻影响上升沿,不影响下降沿。如果使用中不关心上升沿,上拉电阻就可选择尽可能的大点,以减少对地通路的 电流。如果对上升沿时间要求较高,电阻大小的选择应以芯片功耗为参考。