最新版的quartus (19以上)好像没有了直接调用modelsim仿真的功能,实际仿真需要手动建立工程执行:

关于rtl仿真,一般windows平台用modelsim(一般用于小型工程);而linux平台用synopsys: vcs(编译型仿真器)+dve+(verdi/debug工具),一般大型工程,芯片设计,速度快,企业级用。

--------------------------------

以quartus+modelsim为例:

1、modelsim新建一个仿真工程,添加设计文件:

工程设置:新版quartus的设置面板要最大化后才能看到下面的“ok”按钮,这个操作可能会带来一些不便,我一开始就怎么也找不到保存设置的方法,因为我看不到"ok"按钮。

生成仿真文件模板:

2、添加quartus生成的ip仿真文件:

3、添加altera仿真库:

D:intelFPGA_pro19.4quartusedasim_lib

一般verilog只要添加.v文件就行

4、保存指令到do文件,方便下次调用

-------------------------------------------------------

路径说明:

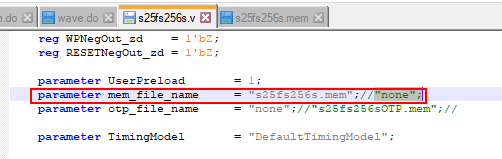

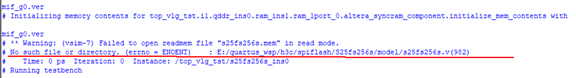

当使用一个第三方器件模型时:

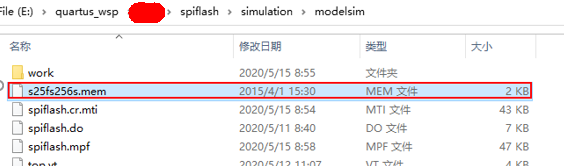

此问题: 默认路径为工程文件所在路径,可以将mem文件拷贝到工程路径下即可

--------------------------------

vivado(2019) 应该类似,但vivado里面现在在设置里面配置好modelsim路径是可以直接调用modelsim进行仿真的,而不需要手动建立工程