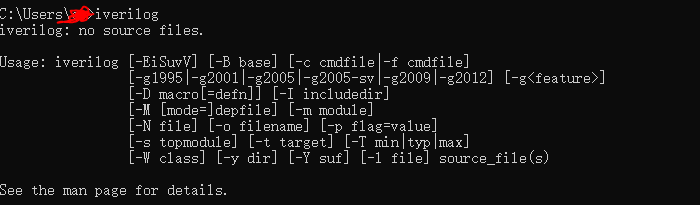

EDA设计软件都很大,读IC设计“研”时,一个软件要安装起来很久,但是巧合接触了Iverilog软件,感觉小巧很多,windows:http://bleyer.org/icarus/iverilog-v11-20190809-x64_setup.exe,安装后要配置系统变量,两个工具的bin目录加载到path里,GTKWave和Iverilog的bin目录,重新启动电脑后,打开CMD如图:

说明成功,安装路径下建立两个.v文件:

module encoder(binary_out,encoder_in,enable); output [3:0] binary_out; input enable; input [15:0] encoder_in; reg [3:0] binary_out; always @ (enable or encoder_in) begin binary_out = 0; if(enable) begin if(encoder_in == 16'h0002) begin binary_out = 1; end if(encoder_in == 16'h0004) begin binary_out = 2; end if(encoder_in == 16'h0008) begin binary_out = 3; end if(encoder_in == 16'h0010) begin binary_out = 4; end if(encoder_in == 16'h0020) begin binary_out = 5; end if(encoder_in == 16'h0040) begin binary_out = 6; end if(encoder_in == 16'h0080) begin binary_out = 7; end if(encoder_in == 16'h0100) begin binary_out = 8; end if(encoder_in == 16'h0200) begin binary_out = 9; end if(encoder_in == 16'h0400) begin binary_out = 10; end if(encoder_in == 16'h0800) begin binary_out = 11; end if(encoder_in == 16'h1000) begin binary_out = 12; end if(encoder_in == 16'h2000) begin binary_out = 13; end if(encoder_in == 16'h4000) begin binary_out = 14; end if(encoder_in == 16'h8000) begin binary_out = 15; end end end endmodule

需要执行上面的encoder.v文件,编写如下:encoder_te.v文件

module encoder_te(); reg enable; reg [15:0] encoder_in; wire [3:0] binary_out; initial begin $dumpfile("test.vcd"); //这两行主要是给gtkwave这个工具使用的... $dumpvars(0,encoder_te); $monitor("%g %b %b %b", $time,enable,encoder_in,binary_out); enable = 0; #5 enable = 1; #5 encoder_in = 16'h0004; #6 encoder_in = 16'h0040; #7 encoder_in = 16'h0400; #8 encoder_in = 16'h1000; #10 $finish; end encoder en(binary_out,encoder_in,enable); endmodule

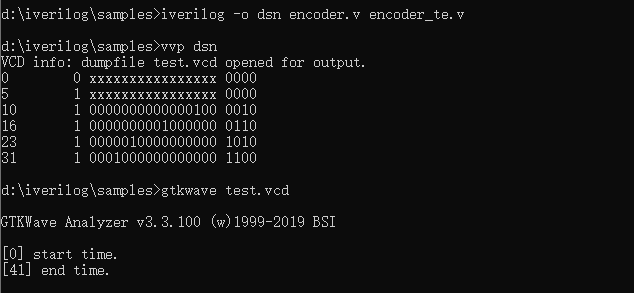

执行命令:iverilog -o dsn encoder.v encoder_te.v,生成dsn文件后,再用vvp dsn 得到test.vcd文件,最后用gtkwave打开 test.vcd文件 仿真

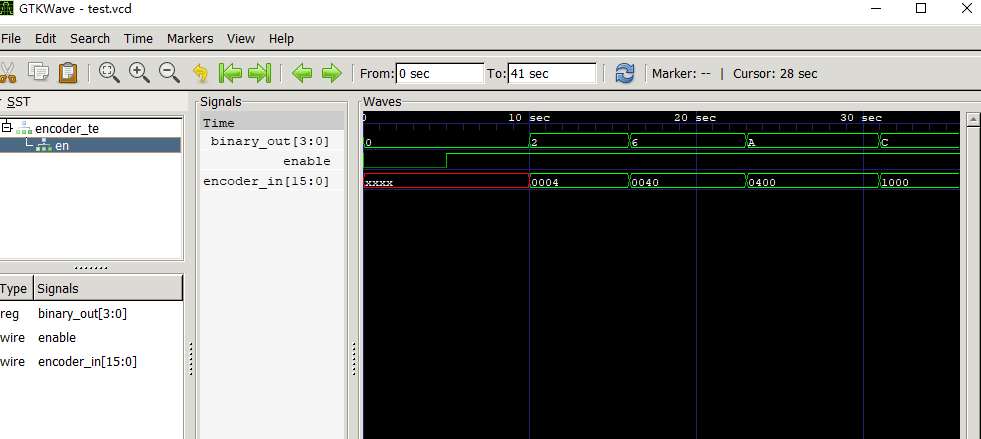

得到如下图:

很清晰的小软件,最新版10几兆才,看着还可以,继续使用 分享...