本章讨论处理器如何处理执行中的不连续性

程序执行的不连续性---------------------------一

体系结构的改进---------------------------------二

硬件的细节---------------------------------------三

一 :程序执行的不连续性

引入同步和异步:

同步,在规定好的时间内发生的事件,如第三章的各个微状态之间的转移。

异步,系统正在进行的,其他活动相关的,不可预料的时间发生的事情,如中断。

程序执行的不连续性:

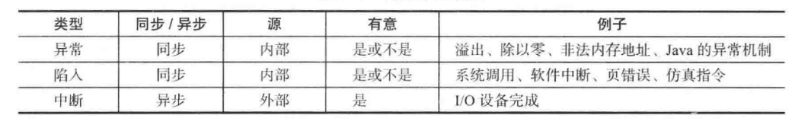

中断,设备引起处理器注意的机制,一般指外部设备引起的不连续性。

异常,内部产生的问题,执行非法指令,要打断原有指令序列的执行然后去处理。

陷入,当前运行的程序无法处理的一种内部情况,只能调用操作系统来处理。

不连续性是一种工具:

他允许计算机系统提供输入/输出

他允许计算机系统为相互竞争的活动管理资源。

他允许计算机系统帮助程序员开发正确的程序。

检测不连续性是处理器的责任,引导处理器处理不连续性代码是操作系统的责任。

处理不连续性要做的事:

硬件隐式完成的活动

操作系统显式完成的活动。

引入处理过程,处理器处理不连续时执行的过程。

处理器在处理不连续性上,与第二章的调用过程基本一样,但是有四个要注意:

1、不连续性可以在指令执行的任意位置发生。

2、不连续性是计划外的,硬件控制权给处理过程,要保存PC的值。

3、在检测到不连续性时,硬件需要确定处理过程的地址,以便转交控制权。

4、硬件隐式保存PC值,需要知道如何如恢复。

引入异常/陷入寄存器ETR,用来保存不连续性的编号。

操作系统和处理器体系结构合作解决:

1、体系结构定义一系列异常和他们对应的编号

2、操作体统定义一系列异常(中断,陷入)以及他们对应的编号。

3、在启动操作系统,建立中断向量表IVT,给出处理异常中断陷入的处理过程地址。

4、在普通程序执行时,硬件检测异常和陷入,将矢量表填入ETR

5、在普通程序执行时,硬件检测外部中断以及对应编号。

6、硬件使用矢量值索引IVT,找到处理过程,将控制权交给处理过程。

二:体系结构的改进

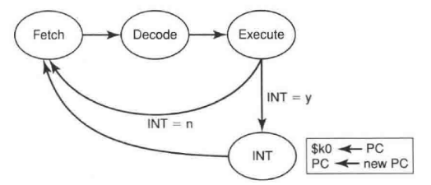

修改FSM:

在原来FSM基础上多一个宏状态

FSM在指令结束时检查,有中断则到INT宏状态,没有就返回Fetch。

把当前PC保存在某个寄存器$k0,接受处理过程的地址,装入PC。

之所以在最后一个检查,因为处理器的寄存器处于干净的状态。

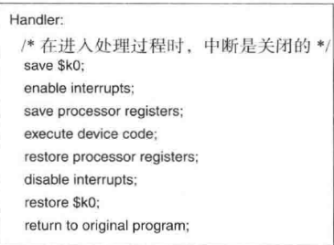

处理级联中断:

中断中又中断回事去原始程序的PC值。

为处理级联中断引入:

禁止中断指令

允许中断指令

处理方法:

关闭中断,原始程序的返回地址保存到$k0,

打开中断,保存寄存器堆,然后执行指令,

执行处理过程,

关闭中断,恢复寄存器$k0,返回原程序。

设备会有不同的优先级,如硬盘〉键盘,如果硬盘中断则忽视键盘。

从处理过程中返回:

引入新指令:Return from interrupt (RETI)

语义:Load PC from $k0;

Enable interrupts;

这是一条原子指令,执行完之前不会有新的中断。

三:硬件的细节

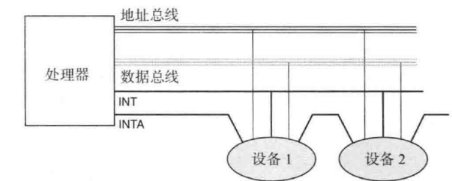

中断数据通路的细节

引入:

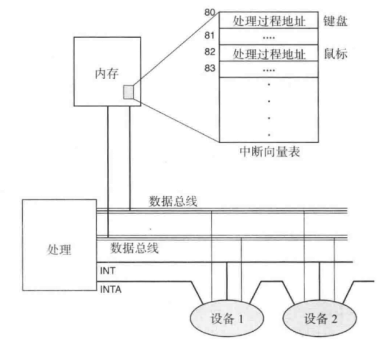

INT线,所有希望中断CPU的设备都断言该线。

INTA线,CPU断言该线,让一个设备得到确认。

所有设备通过“线或”(超出本书范围)先到INT线上

处理器发出的INTA线一次穿过所有设备(菊链),最接近处理器的优先处理。

推广:

多条INT和INTA线,每一对对应一个优先级

设备速度越快,丢失数据可能性越高,所以需要快速处理。

获得过程地址的细节:

在收到处理器发送的INTA信号时,将它的向量放到数据总线上,

与之前操作系统开机放在内存中的IVT对应。

总结:

1、无论何时,设备中断处理器都断言INT。

2、处理器完成EXCUTE宏后检查INT宏状态。

3、如果有中断请求,处理器进入INT宏状态并将INTA线断言。

4、设备收到INTA信号后,将自己的向量放到数据总线上。

5、处理器收到向量并在IVT中查找对应表项,记录处理过程的PC值。

6、处理器将PC保存在$k0中并将IVT中取出的值填入PC。

保存/恢复栈:

中断与当前运行的程序没有关系,取内存哪里为栈。

体系结构有栈指针寄存器来保存两个栈:

用户栈

系统栈

进入INT宏状态,FSM执行栈切换。

硬件改进:

1、复制栈指针,指派$sp为栈指针,复制一个给用户一个给系使用,

中断处理过程保存状态用系统$sp,不会弄乱用户栈。

2、特权模式,处理器引入一个模式位来判断时用户模式还是内核模式(FSM在INT宏状态中为“内核”),

之前允许中断的指令只可以由操作系统使用,也叫特权指令。

体系结构和硬件改进总结:

一个中断向量表IVT,由操作系统初始化为各处理过程的地址。

一个异常/陷入寄存器ETR,含有内部产生的异常和陷入的向量。

接受外部中断的向量的硬件机制。

用户/内核模式和与之相关的处理器模式位。

与模式位有关的用户/内核栈。

一个硬件机制,中断时隐式将当前PC保存到特殊寄存器$k0中。

加入只能由操作系统使用的特权指令用来打断。