1 Verilog

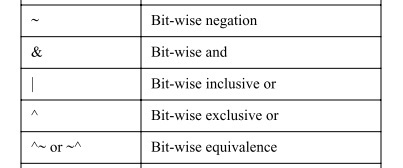

1.1 Bitwise operator

Bitwise operators perform a bit wise operation on two operands.

They take each bit in one operand and perform the operation with the corresponding bit in the other operand.

If one operand is shorter than the other, it will be extended on the left side with zeroes to match the length of the longer operand.

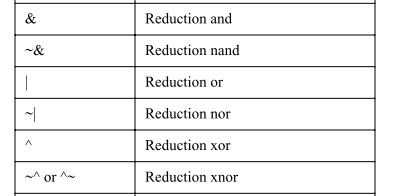

1.2 Reduction operator

Reduction operators are unary.

They perform a bit-wise operation on a single operand to produce a single bit result.

Reduction unary NAND and NOR operators operate as AND and OR respectively, but with their outputs negated.

2 VHDL

FUNCTION and_reduce (arg : STD_LOGIC_VECTOR) RETURN STD_LOGIC;

-- Result subtype: STD_LOGIC.

-- Result: Result of and'ing all of the bits of the vector.

function nand_reduce (arg : std_logic_vector )

return std_logic is

begin

return not and_reduce (arg);

end;

Others are nand_reduce, or_reduce, nor_reduce, xor_reduce, xnor_reduce