SDRAM和dcfifo的联合

设计原理

在"SDRAM突发读写页"实验中,留下了一个问题,就是从SDRAM读取数据的速度要与SDRAM的驱动时钟同步,这就造成了读出的数据的速率过快,我们很难通过在LED上观察其读出的结果。

在学习了dcfifo之后相信你已经了解了dcfifo的功能,没错这一节就是要用到dcfifo作为跨时域的桥梁,把100M的读时钟频率"降下来"。

通过测试模块往SDRAM写入一页的数据,当写如完成后便进入到延迟状态(当然这个延迟我们可以不要),延迟完成后接着进入到读数据状态,在读数据状态中分为两个部分:一个是写dcfifo,即在读出SDRAM的数据的同时将读出的数据写如dcfifo中,在读完SDRAM内部的256个数据之后也就是对dcfifo写完成了,这个过程读SDRAM和写dcfifo的时钟频率是100M。接着对dcfifo进行读操作,这里的读时钟是50M,在读完成后便接着再对SDRAM进行读操作,以此循环…………

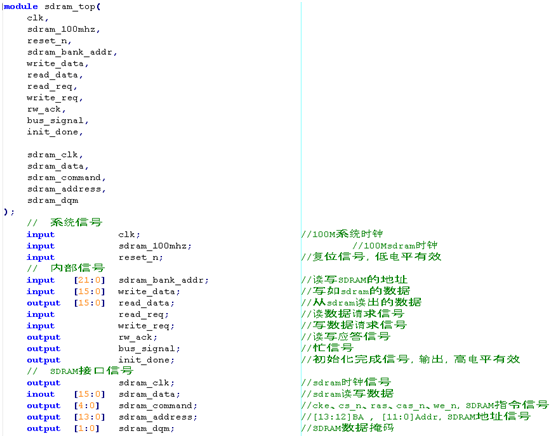

SDRAM突发读写一页的接口

在"SDRAM突发读写页"实验中,驱动SDRAM的顶层接口如下图所示,主要分为3个部分,分别为系统信号、内部信号、SDRAM接口信号。其中系统信号为时钟信号和复位信号,内部信号为读写数据信号和读写控制信号,SDRAM接口信号为FPGA与外部的SDRAM的接口。

该是实验中,系统信号、SDRAM接口信号都很简单,只需配置好其硬件所对应的引脚,当然这里的时钟来源于PLL的倍频时钟。而内部信号要与dcfifo、测试模块进行连接,这也是本节的重点内容。

由于dcfifo只负责接收从SDRAM读出的数据,所以SDRAM顶层模块中的:read_req和read_data需要和dcfifo的顶层模块相连接,read_req也就是dcfifo的写使能write_reg。

异步dcfifo读写的接口

fifo_top只负责接收SDRAM的读出数据,并将其写入到fifo内部,然后再用低的时钟频率将数据读出。

顶层接口信号中的write_reg连接SDRAM的读申请信号read_req,因为读SDRAM的同时对fifo进行写操作,所以SDRAM的数据输出read_data连接到dcfifo的数据输入data_in,read_over用于反馈dcfifo的读操作完成,可以再往fifo内部写入数据。

接口拼接

测试模块

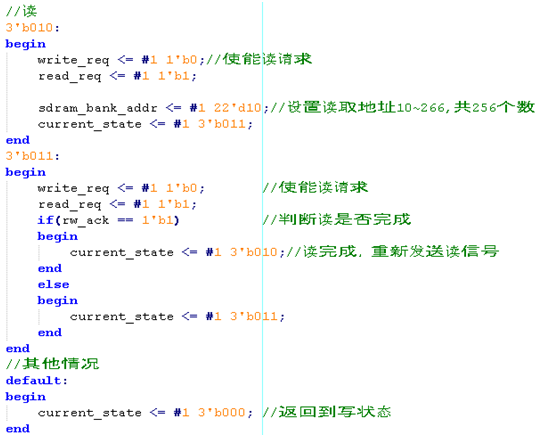

写操作

在判断SDRAM初始化完成后init_done有效,则对SDRAM进行写操作,发送写申请信号的同时发送写数据和写地址信号,在连续写入256个数据后判断rw_ack是否有效,有效则写入完成,将写申请信号清零,进入到延迟状态,延迟一定的时间。

读操作

在延迟一定的时间后便进入到读操作,这时读申请信号有效,并同时发送读地址信号,在下一个状态中判断读操作是否完成(rw_ack是否为1),记住此时也是在对dcfifo进行写操作,当rw_ack有效时,则停止对SDRAM进行读操作,也停止对dcfifo进行写操作,此时进入到对dcfifo进行读操作,当read_over为1时表明对dcfifo读完成,便转入到对SDRAM读操作中,以此循环。

实验效果

实验的工程文件为"sdram_rw_page_fifo",其源代码文件如下:

实验中采用signaltap对输出到LED的数据进行观察,结果如下:

大西瓜FPGA-->https://daxiguafpga.taobao.com

博客资料、代码、图片、文字等属大西瓜FPGA所有,切勿用于商业! 若引用资料、代码、图片、文字等等请注明出处,谢谢!

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号“科乎”。