(注:本文翻译自:http://www.edn.com/design/systems-design/4392195/Equations-and-Impacts-of-Setup-and-Hold-Time)

在深入了解建立时间保持时间方程及其影响之前,先让我们简单的了解一下什么事建立时间和保持时间。

建立时间:建立时间定义为为了使数据正确的锁存,其在时钟有效沿到来前必须稳定的最小时间。任何这一时间的违例将会导致数据捕获错误并产生建立时间违例。

保持时间:保持时间定义为时钟有效沿后数据必须保持稳定的最小时间。这一时间的违例将导致数据锁存错误,并产生保持时间违例。

建立时间保持时间方程

首先定义clock-to-Q延时(Tclock-to-Q),在一个上升沿触发的触发器中,输入信号在时钟的上升沿捕获,并在一小段延时之后(Tclock-to-Q)产生对应的输出。为了使触发器能正确的完成上述任务,其输入端的数据必须在时钟上升沿之前保持一段时间(Tsetup)及之后保持一段时间(Thold)。此外,时钟信号通过时钟树的微小差异称为时钟扭斜(Skew)。

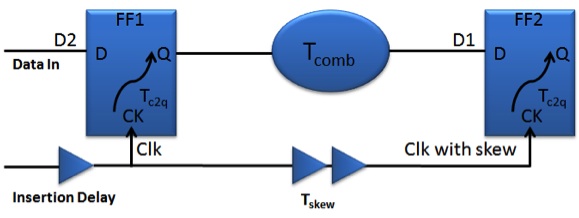

从图-1我们可以得到建立时间和保持时间的方程。

图-1 讨论2个触发器的情况

在上图中,在0时刻,FF1处理D2FF2处理D1。数据D2传播到FF2需要一段时间,从FF1的时钟端开始计时,很明显时间=Tc2q+Tcomb.为了让FF2正确的锁存数据,D2必须在时钟树的第2个上升沿到FF2之前在FF2的D端保持稳定一段时间(setup);因此,为了满足建立时间,方程如下:

Tc2q + Tcomb + Tsetup ≤ Tclk + Tskew ------- (1)

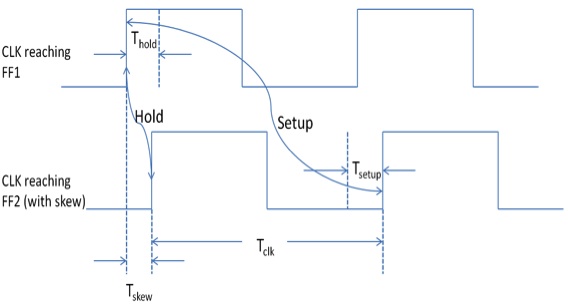

为了更好的理解建立时间和保持时间,可以看看下面的时序图:

图-2 建立时间保持时间时序图

为了避免保持时间违例,数据在时钟上升沿之后还需要保持一段时间(hold)。满足保持时间的方程如下:

Tc2q + Tcomb ≥ Thold + Tskew ------- (2)

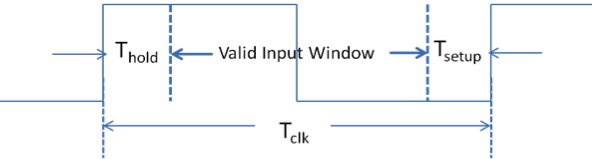

从上述两个方程可以很容易的看出,时钟的正扭斜对建立时间有好处对保持时间则反之。有效输入窗如下:

图-3 有效输入窗

建立时间保持时间例子分析

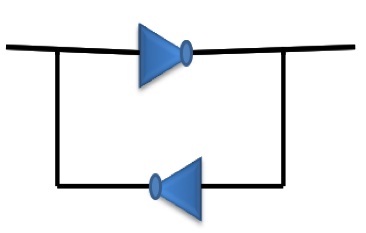

考虑图-4的两个D触发器,基于详细的时序信息,我们可以计算出没有时序违例情况下的电路的最大时钟频率。

图-4 两个D触发器的详细时序信息

时钟插入延时对每个D触发器都是相同的,它不会约束给定的最大时钟工作频率。从上图可看出,其不会违反保持时间约束。考察建立时间有:

(Time available for data to travel from FF1 to FF2) ≥ (Time needed for data to travel from FF1 to FF2)

Tclk + Tskew ≥ Tc2q + Tcomb + Ts2

Tclk + 0.25ns ≥ 0.1ns + 5ns + 3ns

Tclk ≥ 7.85ns

最小的时钟周期为7.85ns,最大的频率为127.4MHz.

从上面的例子可以看出,改善最大时钟频率可以采用如下3种方式:

1、减小组合逻辑延迟。

2、如果可以的话,增大时钟扭斜。

3、用更快的D触发器(更小的Tc2q和Tsetup)。

时钟到Q端延时对建立时间保持时间约束的影响

因为触发器内部的锁存电路是两个背靠背的反相器(图-5),其IO特性如图-6。

为了方便解释,假设0V对应逻辑0,5V对应逻辑1;从图-6可以看出,如果背靠背反向器的输入不是正确的0V,5V,它需要一定的锁存周期来产生稳定的反相器输出,这段延时称之为时钟到Q端延迟(Tclock-to-Q)。

图-5 锁存用背靠背反向器

图-6 反向器IO特性

如果上述延时在触发器之间累加的话,可能会发生数据信号在期望捕获的时钟沿miss掉。

(全文完)