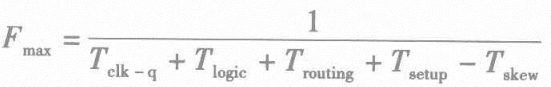

时序指的是一个设计的时钟速度。在设计中任何两个时序元件之间的最大延时将决定最大的时钟速度。最高速度或最大频率可以直接按照著名的最大频率方程定义(不考虑时钟到时钟的抖动):

最大频率

其中Fmax是时钟可允许的最大频率,Tclk-q是从时钟到达直至数据到达Q端的时间,Tlogic是逻辑通过触发器之间的传播延时,Trouting是触发器之间的布线延时,Tsetup是下一个时钟上升沿之前数据必须到达D端的最小时间(即建立时间),Tskew是启动触发器和捕捉触发器之间时钟的传播延时。

改善时序性能的一些方式:

- 添加寄存器层次

- 并行结构

- 展平逻辑结构

- 寄存器平衡

- 重新安排路径