在一个DFG的所有零延时路径中,具有最长运算时间的路径Tlong称为关键路径,这决定了系统时钟Tsys的最快速度。Tsys >Tlong.

一个架构的速度由任意两个锁存器间、或一个输入与锁存器间、或一个输出与一个锁存器间、或输入与输出之间的最长路径(关键是没有锁存器)决定。在这个存在的最长路径上插入锁存器就缩短了最长路径提高了速度。

流水线是是在在数据通路上引入流水线寄存器来缩短关键路径。如下图所示:

如果加法器的时延设为1ut.在图a中关键路径为输入到输出即2ut;在图b中间插入了一个锁存器,关键路径的时延为1ut.图c中将数据分为奇偶部分同时进行,速率又提高了一倍。

如果加法器的时延设为1ut.在图a中关键路径为输入到输出即2ut;在图b中间插入了一个锁存器,关键路径的时延为1ut.图c中将数据分为奇偶部分同时进行,速率又提高了一倍。

如何插入寄存器?流水线锁存器只能按照穿过图的前鐀割集的方式插入,不改变电路功能。(割集即去掉了这些边一个连通图不再连通的边的集合,前鐀割集即数据在割集的所有边上都没前进的方向移动)。如下:

图a中关键路径为A3—>A5---->A4---->A6,即3.若要提高速度,需要缩短这个关键路径,一个前馈割集如图中虚线经过的边包含关键路径,在其中插入锁存器即可。图b中改变了电路功能,未在 前馈割集的所有边上上插入锁存器,错误。正确如图c.

图a中关键路径为A3—>A5---->A4---->A6,即3.若要提高速度,需要缩短这个关键路径,一个前馈割集如图中虚线经过的边包含关键路径,在其中插入锁存器即可。图b中改变了电路功能,未在 前馈割集的所有边上上插入锁存器,错误。正确如图c.

转置定理:反转一个给定SFG(信号流图)的所有边的方向并且互换输入与输出端口,系统的功能不变。一个FIR滤波器的例子如下。一个直接型3阶FIR如图:

转置滤波器框图:

此时关键路径由一个乘法器加两个加法器变了一个乘法器和一个加法器,这个例子还不是非常明显,如果一个N阶的直接型结构的FIR,其关键路径是1个乘法器加N-1个加法器,转置后变了一个乘法器和一个加法器,减少了N-2个加法器的延时。

此时关键路径由一个乘法器加两个加法器变了一个乘法器和一个加法器,这个例子还不是非常明显,如果一个N阶的直接型结构的FIR,其关键路径是1个乘法器加N-1个加法器,转置后变了一个乘法器和一个加法器,减少了N-2个加法器的延时。

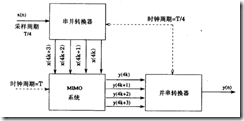

并行处理:即结构复制,输入分开同时进行处理从而提高了速度。

如 y(n)=ax(n)+bx(n-1)+cx(n-2) 可分解成三个部分:

y(3k)=ax(3k)+bx(3k-1)+cx(3k-2)

y(3k+1)=ax(3k+1)+bx(3k )+cx(3k-1)

y(3k+2)=ax(3k+2)+bx(3k+1)+cx(3k )

一个完整的结构如下: