转自知乎:

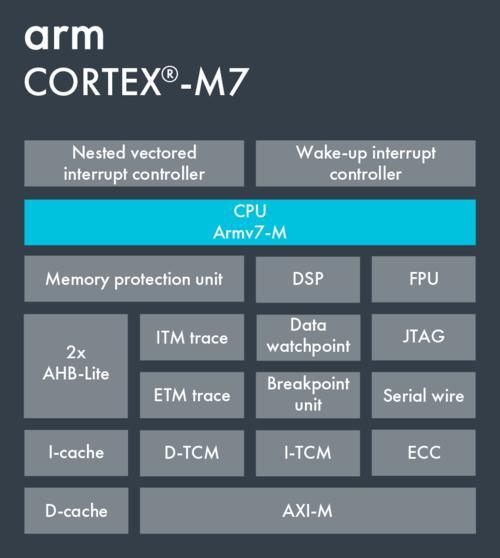

ARM Cortex-M7处理器体系结构简介

本文以ST公司的STM32F7为实例来介绍M7体系结构,主要涉及M7存储器模型以及缓冲机制、编程模型、异常模型、处理器两大工作模式以及特权级,对于核心寄存器、内核外设SysTick、MPU、FPU以及系统控制块SCB仅做简单介绍。适用于对MCU+RTOS感兴趣的读者;

参考手册:

- STM32F7 Series Cortex®-M7 processor programming manual

- ARM Cortex-M7 Processor Technical Reference Manual

- ARM Cortex-M7 Devices Generic User Guide

一、指令集类型简单介绍:

在计算机处理器发展史上形成了CISC(复杂指令集计算机)和RISC(精简指令集计算机)两大指令集阵营;CISC以x86体系结构为主,它拥有复杂且庞大的运算和控制指令,可以为桌面计算机和服务器提供强悍的计算能力;RISC主要以ARM体系结构为主,它克服了x86指令集中的二八原则,复杂指令分解为基本指令来处理;由于ARM指令集宽度一致,它可以采用超长流水线技术提升执行速度;由于ARM指令集规模较小,电路规模自然没有x86庞大,因此具备低功耗特点;ARM体系结构还有很多不同于x86的特点,例如存储加载型访问,采用大量寄存器;本文所述M7也是采用了RISC技术;

二、存储器模型以及缓存机制:

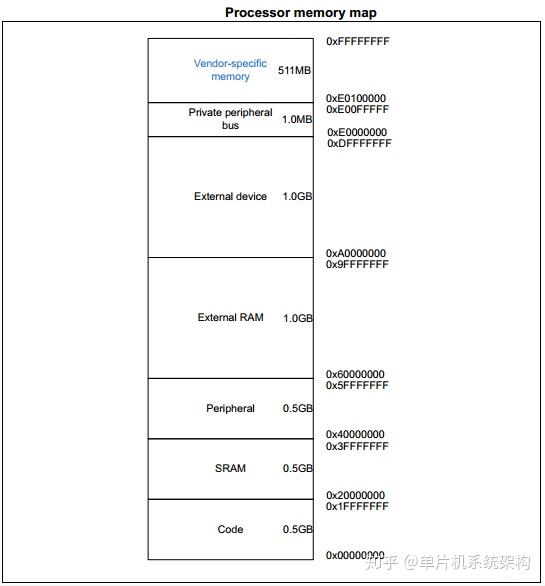

存储器地址映射示意图

存储器地址映射示意图

在M7上,将代码区,数据区,外设区,FSMC区和内核区统一组织在4GB的线性地址空间中。CPU只能通过LDR,STR等存储加载指令访问存储器,可以采用字节访问,半字访问和字访问三种访问类型;采用小端模式,即低字节存储在低地址;

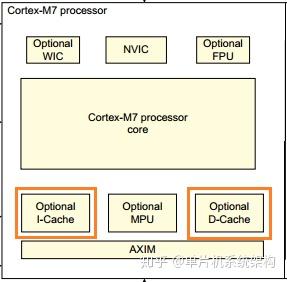

指令缓存,数据缓存

指令缓存,数据缓存

CPU和存储器之间有4KB指令缓存和4KB数据缓存,缓存可以加速CPU对存储区的访问;在某些场合开发者需要注意缓存和存储区一致性问题,例如如果开发者使能了缓存,然后将某一个代码区扇区擦除(未存储代码),则此时已经擦除扇区数据和已经缓存数据便不一致,导致出错;

三、编程模型:

在CPU执行程序过程中,可以分为Thread模式和Handler模式;在Thread模式下执行应用代码,属于处理器正常工作过程;在Handler模式下执行异常代码,例如不可屏蔽异常服务程序,硬件错误异常服务程序等;

特权级:程序有特权级和非特权级之分;特权级程序运行在特权级别上,可以访问系统所有资源,非特权级程序运行在非特权级别上,它的访问有限制,例如不能访问系统内核寄存器;Handler模式运行在特权级别上,Thread模式可以运行在特权或者非特权级上;

堆栈指针:它有主堆栈指针MSP和线程堆栈指针PSP之分,Handler模式下只能使用MSP,Thread模式可以使用MSP或者PSP;

模式,特权级别和堆栈指针

模式,特权级别和堆栈指针

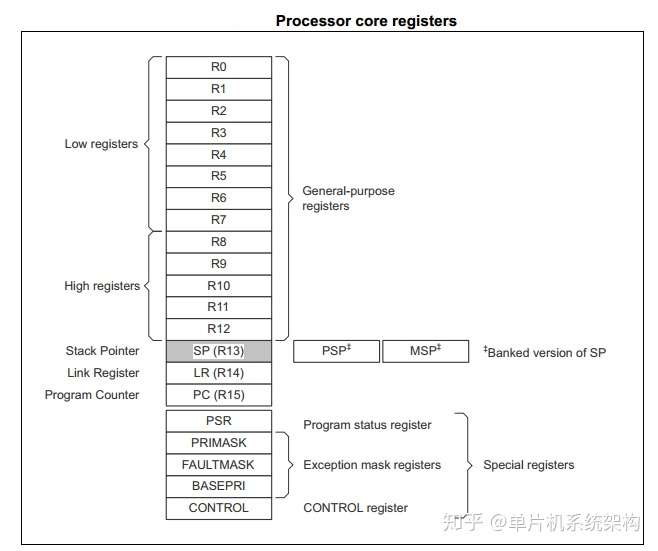

核心寄存器:

M7包含R0~R12,SP(MSP,PSP),LR,PC,APSR,IPSR,EPSR,PRIMASK,FAULTMASK,BASEPRI和CONTROL;

R0~R12作为通用寄存器用于数据处理;

SP(R13)用于存放栈地址,它有MSP和PSP之分,具体使用取决于CONTROL.bit1;在Handler模式下强制CONTROL.bit1为0,即使用MSP;

LR(R14)用于存放子程序返回,异常返回数据,例如模式,堆栈,FPU使用等;

PC(R15)用于存放当前指令地址;

PSR程序状态寄存器包含APSR应用程序状态寄存器,IPSR中断程序状态寄存器,EPSR异常程序状态寄存器;APSR记录程序计算状态条件,IPSR用来记录当前中断服务程序的异常类型编号,EPSR用于THUMB状态位,IT位,ICT位等;

PRIMASK:用于屏蔽可配置的优先级;

FAULTMASK:用于屏蔽除了NMI以外的所有可配置的优先级

BASEPRI:屏蔽所有数值上不小于它的优先级;

CONTROL:用于设置特权级,选择堆栈指针以及FPU上下文切换;

四、异常模型:

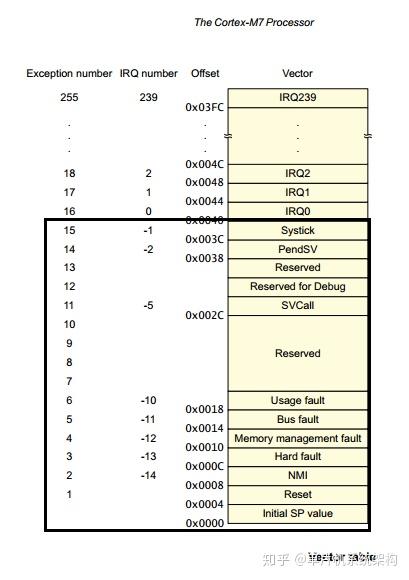

M7异常向量表,包含异常编号,中断请求编号,存储器分布

M7异常向量表,包含异常编号,中断请求编号,存储器分布

M7处理器一共有255个异常,异常编号为1~255;其中1~15属于内核异常,大于15属于外设中断;在程序开发中,使用-14~-1表示内核中断(异常)请求编号,大于-1表示外设中断请求编号;

异常分为非活跃且非挂起状态,挂起状态,活跃状态,活跃且挂起状态;

M7每个异常有一个8位寄存器表示其优先级,即支持0~255优先级,但是在STM32F7内部只是实现其高4位,即支持0~15优先级;通过配置优先级分组后,高优先级可以抢占低优先级异常;

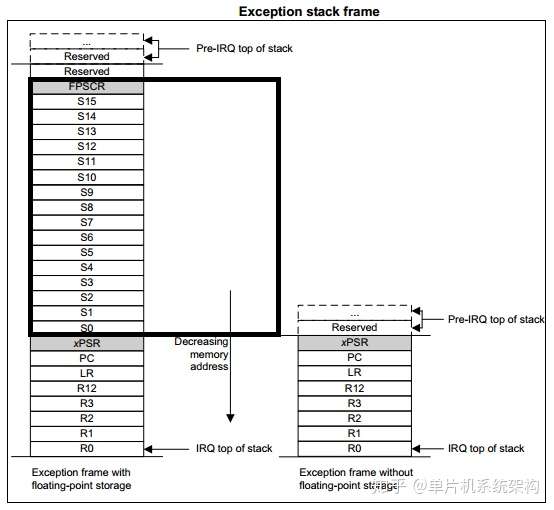

异常处理是保存现场和恢复现

异常处理是保存现场和恢复现

保存现场:考虑一种简单的情况,异常帧中没有FPU保存时,这时硬件会将xPSR, PC, LR, R12, R3, R2, R1, R0全部保存在SP指向的栈区,在RTOS中R4~R11由程序员入栈;

执行中断服务程序:用于处理外部事件;

恢复现场:采用以下其中一条指令进行返回:

- An LDM or POP instruction that loads the PC.

- An LDR instruction with PC as the destination.

- A BX instruction using any register.

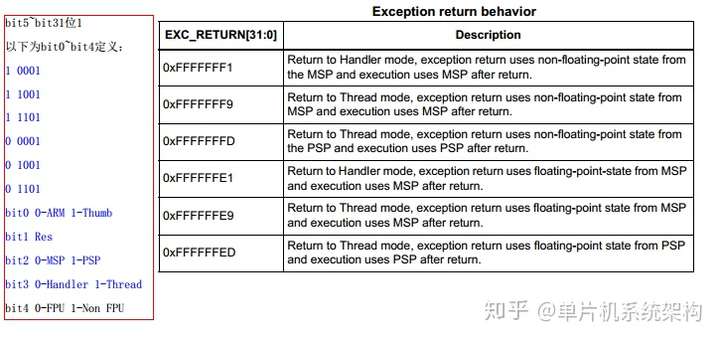

异常返回LR定义

异常返回LR定义

例如采用BX LR返回,执行指令后处理器根据LR最低5bit获取返回模式,堆栈指针使用以及FPU使用等;然后硬件将R0, R1, R2, R3, R12, LR, PC, xPSR出栈,在RTOS中R4~R11由程序员出栈,并且开始执行被中断程序的下一条指令;为了降低中断延时,M7还采用了咬尾中断,晚到中断等机制;

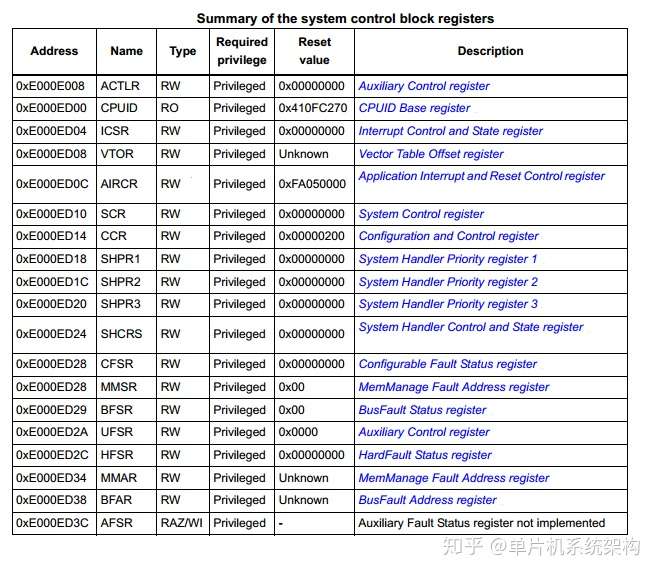

五、SCB:系统控制块

系统控制块

系统控制块

系统控制块主要实现系统状态和系统控制功能,例如1~15号异常控制,优先级分组配置,重定位中断表位置等;

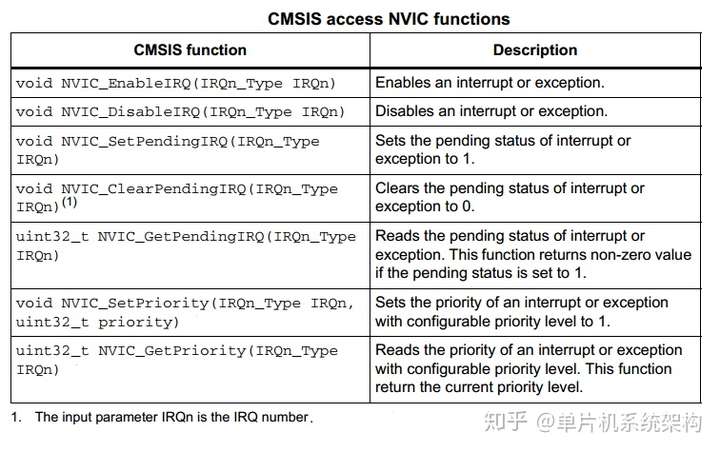

六、NVIC:嵌套向量中断控制器

主要用来管理IRQ0~IRQ239外设中断请求,并且CMSIS提供了一套函数用来访问NVIC寄存器;

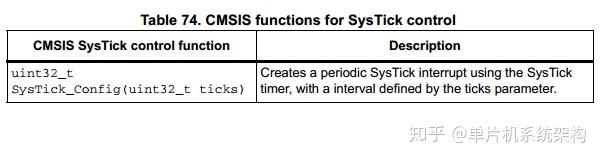

七、SysTick:系统滴答定时器

SysTick操作函数接口

SysTick操作函数接口

SysTick旨意提供MCU软件重用,用户在更换以M7为内核的其他MCU尤其在支持RTOS时,在移植内核时,可以不加修改地直接使用。

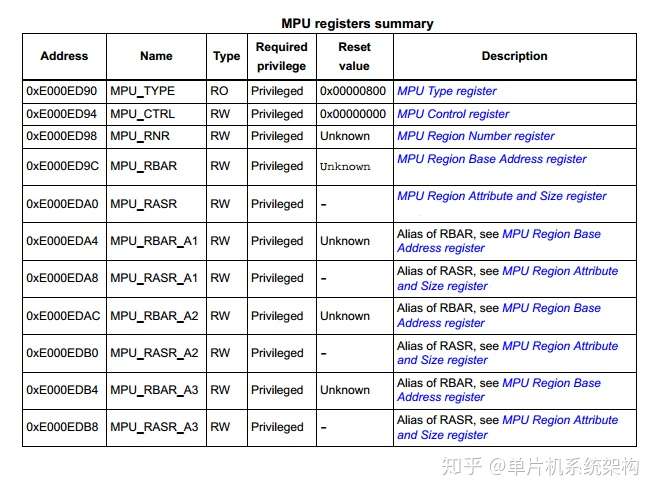

八、MPU:存储器保护单元

存储器保护单元寄存器

存储器保护单元寄存器

MPU将存储器空间划分为若干分区,定义每个分区的位置、大小、访问权限和属性等。

九、FPU:浮点数处理单元

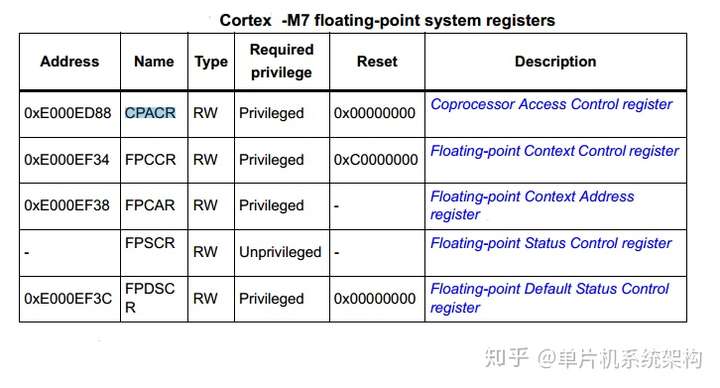

浮点处理单元寄存器

浮点处理单元寄存器

FPU支持单精度和双精度加、减、乘、除、乘加以及平方根运算;支持定点数和浮点数之间的格式转换以及浮点常量指令;支持IEEE754标准;

十、总线访问控制

指令数据紧密耦合存储器控制

AHB主总线控制

AHB从总线控制

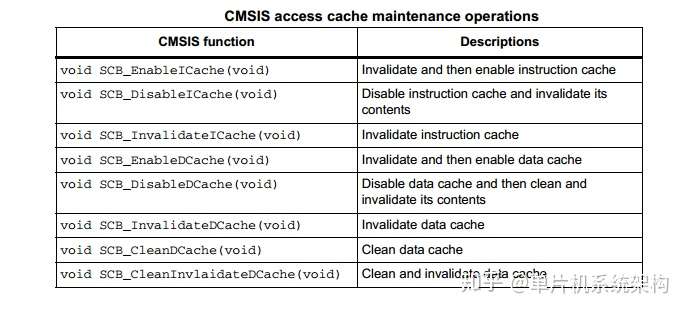

缓存控制

总线错误状态

十一、总结

内核寄存器映射和访问函数由CMSIS统一提供,提高了软件在以M7为内核的微控制器上的复用。使开发者在不同芯片厂商之间快速开发切换提供了可能。以上是对M7体系结构的简介,详介请参考手册;