Introduction

本文将一步步实现以下基本仿真流程:

- 创建设计工作库

- 编译设计单元

- 加载设计

- 运行仿真

本文用到的设计文件

本文的范例是一个8位的二进制加法计数器和相关的测试文件。保存路径:

Verilog-<install_dir>/examples/tutorials/verilog/basicSimulation/counter.v and tcounter.v

相关阅读

用户手册的章节:设计库、Verilog和SystemVerilog仿真。

参考命令:vlib,vmap,vlog,vcom,view,run.

创建设计工作库

在你仿真前,必须先创建一个库并编译源码到这个库。

- 创建一个新目录并复制本文的设计文件。

Copy counter.v 和tcounter.v

2. 启动modelsim。

a. windows下双击快捷方式启动,你将看到modelsim的欢迎对话框,单击Close.

b. 选择File > Change Directory 指定到第一步创建的目录。

3. 创建工作库。

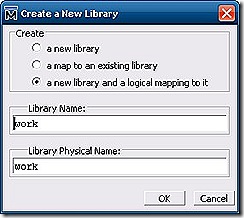

a. 选择File > New > Library.

弹出一个对话框,可以指定库名等选项。如图1。

图 1 创建一个新库

b. 在Library Name项输入work(如果它没有自动输入)。

c. 单击OK.

modelsim创建了一个目录work并写了一个名为_info的文件到这个目录。这个_info文件必须保持在 work文件夹以区分他是modelsim的库。不要从你的操作系统里修改这个文件夹里的内容;所有操作应该在modelsim里进行。

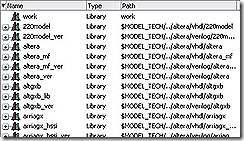

modelsim也把work库添加到库窗口(图2)并记录库映射作为未来参考(modelsim.ini)。

图 2

当你在第3步单击确定后,Transcript窗口显示以下内容:

vlib work

vmap work work

这两行命令等于你的菜单操作。

编译设计单元

创建工作库后,接着就准备编译你的源文件。

可以使用图形界面的菜单,也可以用命令行。

- 编译counter.v和tcounter.v.

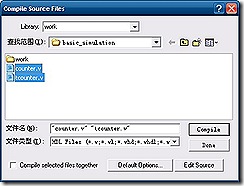

a. 选择Compile > Compile.打开编译源文件对话框(图3)。

如果编译菜单选项不可用,你可能已经打开了一个工程。如果这样,通过激活库窗口并选择File > Close 关闭工程。

b. 在编译源文件窗口选择counter.v和tcounter.v并单击Compile.文件被编译到work库。

c. 当编译完成,单击Done.

图 3

2. 查看编译的设计单元。

a. 在库窗口,单击work前的’+’,你将看到2个设计单元(图4)。可以看到它们的类型和相关源文件的路径。

图 4

加载设计

1. 加载test_counter模块到仿真器。

a. 在库窗口,单击work前的‘+’显示包含的文件。

b. 双击test_counter.

你也可以通过选择Simulate > Start Simulation加载设计。这将打开开始仿真对话框,选择Design标签,单击work前的‘+’,选择test_counter模块,然后单击OK(图5)。

图 5

c. 当设计加载后,打开一个结构窗口(标签为sim)。这个窗口显示设计的结构层次(图6)。你可以通过单击每行前的‘+’或‘-’浏览设计。

图 6

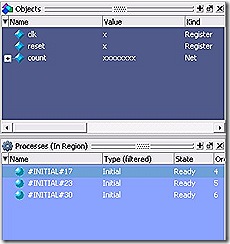

另外,打开Objects窗口和Processes窗口(图7)。Objects窗口显示在Structure(sim)窗口里选择的区域的数据对象的当前值和名称。数据对象包含信号、网络、寄存器、没有在进程里声明的常量和变量、种类、参数。

Processes窗口显示HDL进程列表:激活,区域内,设计和层次。设计查看模式是ESL(电子系统级)设计主要导航模式。这个窗口缺省显示你仿真的激活进程。

图 7

执行仿真

我们将要执行仿真。但在仿真之前,要打开波形窗口并添加信号。

1. 打开波形窗口。

a. 在命令行输入view wave.

在主窗口的右边将打开波形窗口。调整合适的大小。

你也可以用View > Wave菜单选项打开波形窗口。波形窗口只是View菜单下几个可用的调试窗口之一。

2. 在波形窗口添加信号。

a. 在Structure(sim)窗口,右击test_counter打开一个菜单。

b. 选择Add > To Wave > All items in region(图8)。

所有的信号被添加到波形窗口。

图 8

3. 执行仿真

仿真执行100ns(缺省仿真长度),波形将在波形窗口显示。

b. 输入run 500在 VSIM> 提示符后。

仿真将继续运行500ns(图9).

图 9

仿真将继续运行直到你执行中断命令或者代码里的语句(比如$stop)。

设置断点和单步执行

接下来,简要介绍modelsim环境的交互式调试特性。设置一个断点,执行仿真,单步执行和测试。断点设置在可执行行,导致红色的行号。

1. 在源文件窗口打开counter.v.

a. 选择View > Files打开文件窗口。

b. 单击sim前的+,查看vsim.wlf的内容。

c. 双击counter.v打开源文件。

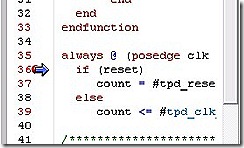

2. 在36行设置一个断点。

a. 滑动到36行,在行标的右侧单击。一个红色的球出现在行标的右边(图10)表示已经设置了一个断点。

图 10

3. 不使能、使能和删除断点

a. 单击红色的球不使能断点。它将变成黑色的球。

b. 单击黑色的球,使能断点。它将变成红色的球。

c. 右击红球,选择Remove Breakpoint 36。

d. 单击36行行标边重创建断点。

4. 重启仿真。

a. 单击Restart图标![]() ,重新加载设计并重置仿真时间到0。

,重新加载设计并重置仿真时间到0。

重启对话框提供选项以保留设置(图11)。

图 11

b. 单击重启对话框的Restart.

仿真将运行到断点。当执行到断点,仿真停止,高亮显示并有一个蓝色箭头(图12),在文本信息窗口有中断信息。

图 12

当到达一个断点,典型的查看信号值的方法有几种:

- 在Objects窗口查看(图 13)

图 13

- 把鼠标指向源文件窗口的变量,一个黄色的提示框出现,含有变量名和值。

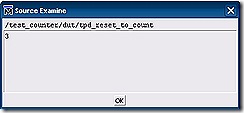

- 在源文件窗口高亮一个信号,参数,或者变量。右击,选择Examine,它的值将在Source Examine 窗口(图 14)。

图 14

- 使用examine命令。

5. 单步执行

试验:设置断点,使用Step , Step Over,和Continue Run 命令。

要点

在继续之前,需要结束当前仿真。

- 选择Simulate > End Simulation.

- 单击 Yes 退出仿真。

Conlusion

本文是quartus II 9.1 配套的modelsim 6.5b的指南之一。

See also

ModelSim Tutorial –Chapter 3 Basic Simulation