3. 状态机A/D采样控制电路

3.1 目标:用状态机控制ADC0809实现数据采集。

3.2 ADC0809简介

(1)ADC0809是8位A/D转换器,片内有8路模拟开关,可控制8个 模拟量中 的1个进入转换器中。完成一次转换的时间约100us。含锁存控制的8个

多路开关,输出有三态缓冲器控制,单5V供电。ADC0809的外部引脚,工作时序图详见其数据手册。start是转换启动信号,高电平有效。ale是

地址锁存信号。eoc是转换状态信号,约100us,上跳沿表示转换结束。oe是输出使能。

(2)ADC0809更详细的说明可参阅数据手册和数字电路基础里的模数转换部分,比如,康华光版数电书里有讲解逐次逼近的转换原理,用天平称重

选砝码的过程来类比对分法,高位为1,先跟1/2的vref比较,然后再更加或减一半的一半比较,循环下去,8位就比较8次,得到一组8位的数字编码

对应当前输入的模拟量的最接近的值。也用到了极限的思想。这样,模拟量的输入就转换成数字量的输出了。

3.3 这个实验要实现的就是用Verilog HDL来设计一个状态机控制逻辑,控制ADC0809的时序,完成一个数据采集的功能。

(1)设计思想:研究ADC的功能描述和引脚说明,时序图,把时序分成几个状态;然后把adc的输入信号和输出信号颠倒,作为控制逻辑的输入和输出。

(2)ADC0809采样控制电路的Verilog 代码:

1 // adc0809 control circuit 2 //2020-11-3 3 // by YongFengXie 4 module adc0809( 5 input clk, 6 input [7:0] d, //adc0809 output 7 input clr, 8 input eoc, 9 output reg ale, 10 output reg start, 11 output reg oe, 12 output adda, // LSB of the 3 input signal chanel 13 output lock0, // data lock signal 14 output [7:0] q); // output data 15 reg lock; 16 parameter s0='d0,s1='d1,s2='d2,s3='d3,s4='d4; 17 reg [2:0] current_state,next_state; 18 reg [7:0] rel; 19 20 assign adda = 0; 21 assign lock0=lock; 22 assign q=rel; 23 24 always @(posedge clk or posedge clr) 25 begin 26 if(clr) 27 current_state <= s0; 28 else 29 current_state <= next_state; 30 end 31 32 always @(posedge lock) 33 begin 34 rel <= d; 35 end 36 37 always @(current_state,eoc) 38 begin 39 case(current_state) 40 s0:begin 41 ale<=1'b0; 42 start<=1'b0; 43 lock<=1'b0; 44 oe<=1'b0; 45 next_state<=s1; 46 end 47 s1:begin 48 ale<=1'b1; 49 start<=1'b1; 50 lock<=1'b0; 51 oe<=1'b0; 52 next_state<=s2; 53 end 54 s2:begin 55 ale<=1'b0; 56 start<=1'b0; 57 lock<=1'b0; 58 oe<=1'b0; 59 if(eoc) 60 next_state<=s3; 61 else 62 next_state<=s2; 63 end 64 s3:begin 65 ale<=1'b0; 66 start<=1'b0; 67 lock<=1'b0; 68 oe<=1'b1; 69 next_state<=s4; 70 end 71 s4:begin 72 ale<=1'b0; 73 start<=1'b0; 74 lock<=1'b1; 75 oe<=1'b1; 76 next_state<=s0; 77 end 78 default:next_state<=s0; 79 endcase 80 end 81 82 endmodule 83 84

adc0809测试代码:

1 // adc0809 control circuit testbench 2 //2020-11-3 3 // by YongFengXie 4 `timescale 1us/1us 5 module adc0809_tb; 6 7 reg clk; 8 reg [7:0] d; //adc0809 output 9 reg clr; 10 reg eoc; 11 wire ale; 12 wire start; 13 wire oe; 14 wire adda; // LSB of the 3 input signal chanel 15 wire lock0; // data lock signal 16 wire [7:0] q; 17 18 adc0809 ub(clk,d,clr,eoc,ale,start,oe,adda,lock0,q); 19 20 initial begin 21 clk=1'b0; 22 clr=1'b1; 23 d=8'b1011_1010; 24 eoc=1'b1; 25 #20 clr=1'b0; 26 #100 eoc=1'b0; 27 #150 eoc=1'b1; 28 #10 d=8'b0001_0010; 29 #500 $stop; 30 end 31 32 always #5 clk=~clk; 33 34 endmodule

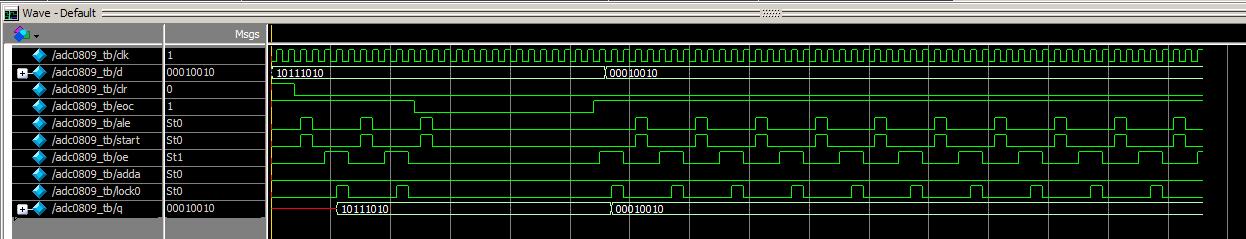

仿真结果: