主存储器

一、主存储器的相关

1.主存储器的地位

2.主存储器的分类

3.主存储器的技术指标

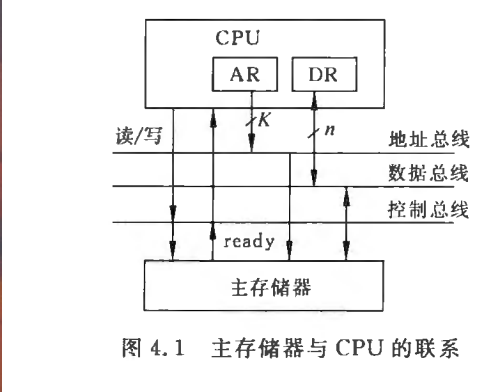

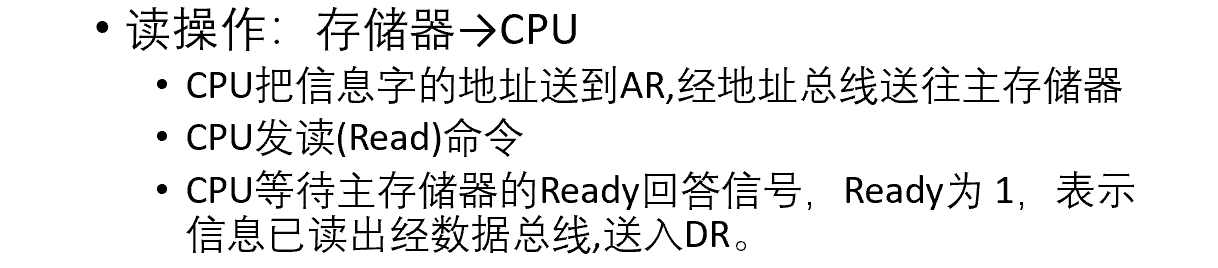

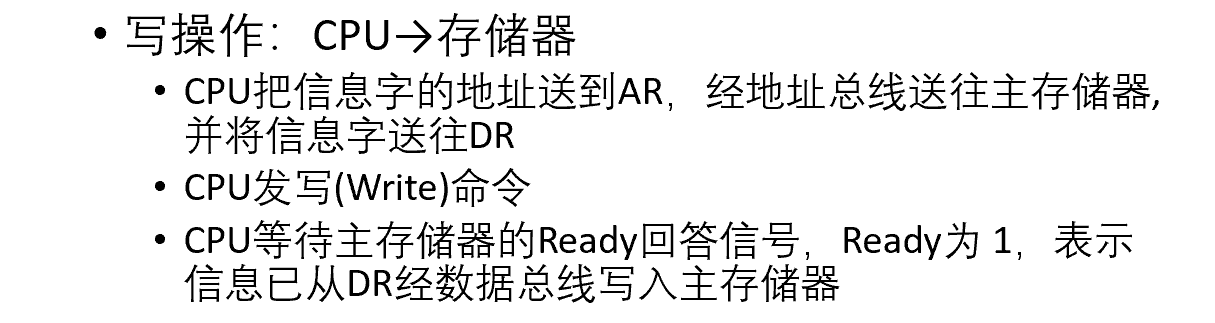

4.主存储器的基本操作

二、读/写存储器

DRAM和SRAM均为可任意读写的随机存储器,当停电时,所存储的内容立刻消失,所以是易失性存储器

DRAM和SRAM均为可任意读写的随机存储器,当停电时,所存储的内容立刻消失,所以是易失性存储器

1.静态存储器(SRAM)

-

定义:

-

特点:

-

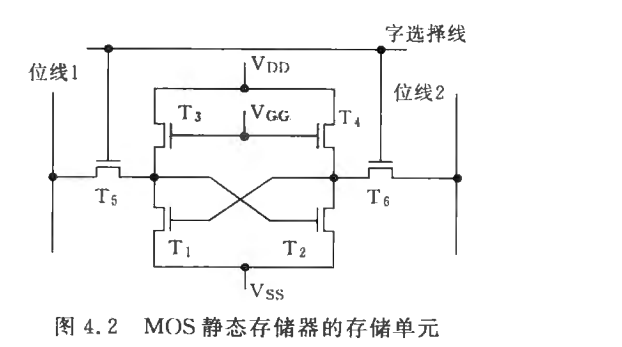

结构:

- 存储单元:静态存储器的存储单元由6个MOS管组成一个双稳态触发器

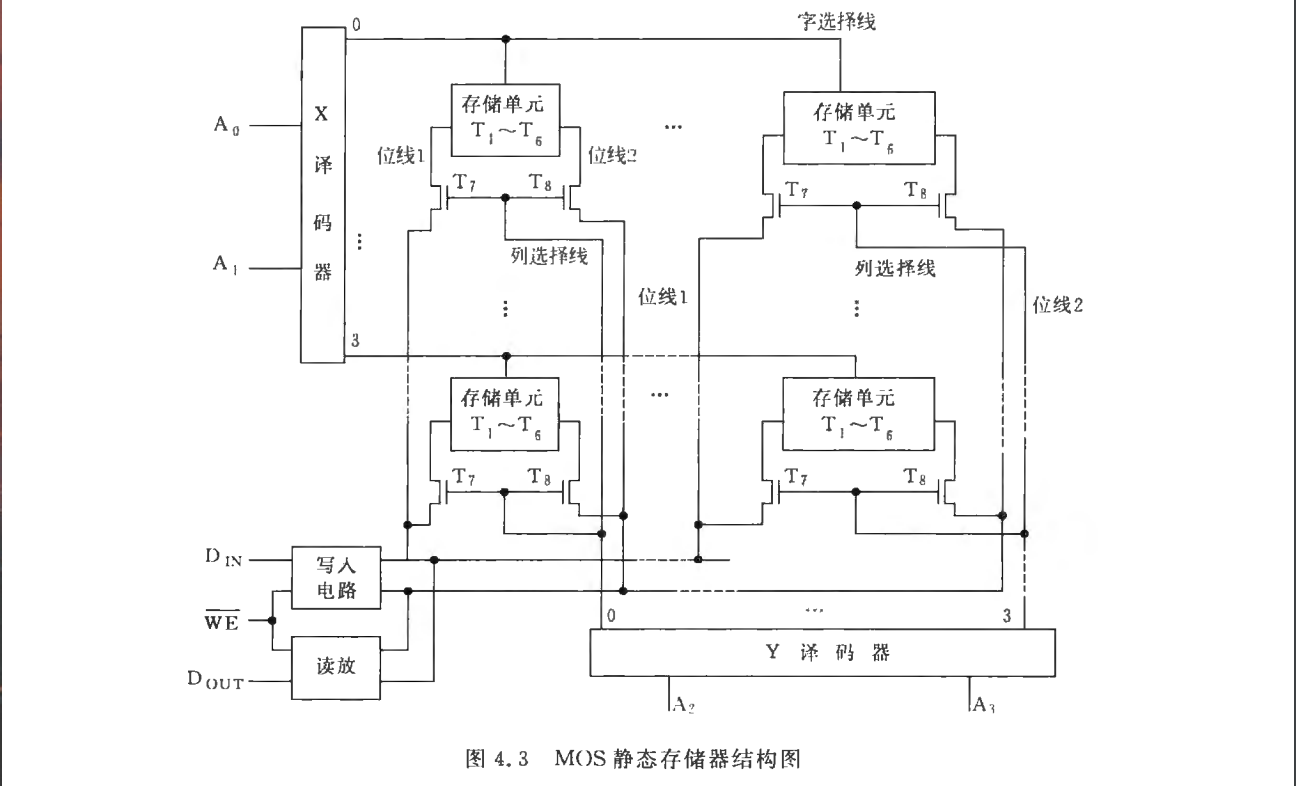

- 存储器:图4.3是用图4.2所示单元组成的16×1位静态存储器的结构图

- 存储单元:静态存储器的存储单元由6个MOS管组成一个双稳态触发器

-

读/写时序:

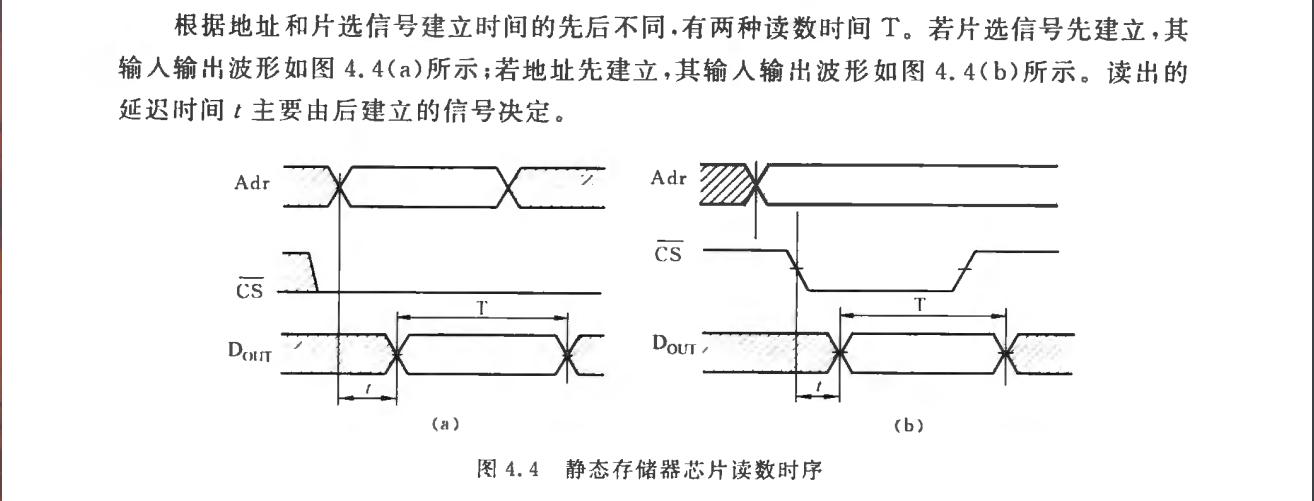

- 读时序:

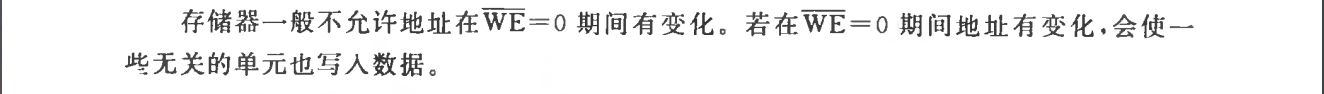

- 写时序:

- 读时序:

2.动态存储器(DRAM)

-

定义:

-

特点:

-

结构:

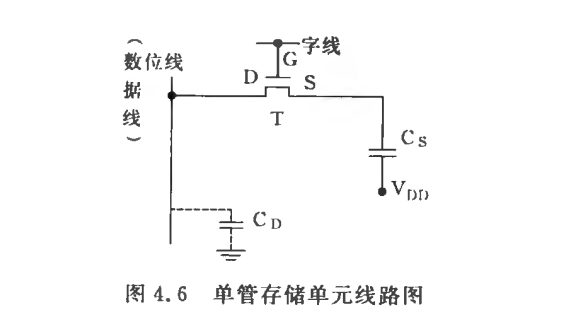

- 存储单元:单管存储单元由一个晶体管和一个与源极相连的电容组成

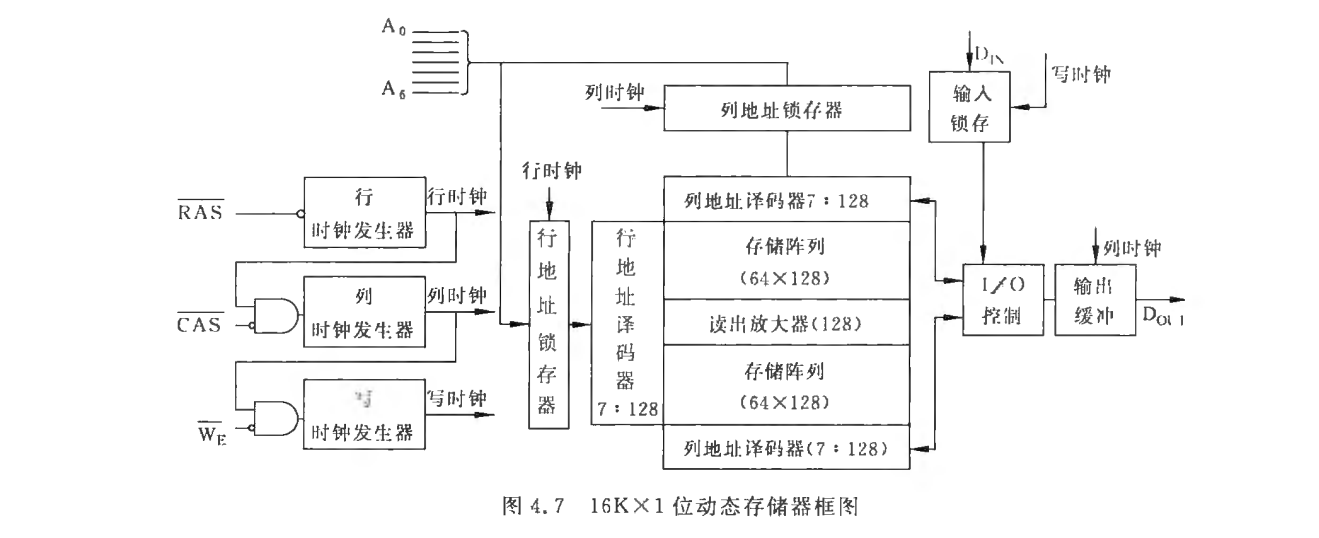

- 存储器:图4.7是16K×1位动态存储器的框图,其工作原理与大容量动态存储器相似,存储单元采用单管单元,16K字存储器需要14位地址码

- 存储器原理:

- 时序图:

- 读工作方式

- 写工作方式

- 页面工作方式

- 存储单元:单管存储单元由一个晶体管和一个与源极相连的电容组成

-

发展:

- 同步DRAM(Synchronous DRAM SDR AM)

- DDR(double data rate)SDRAM

- DDR2 SDRAM

- DDR3

- Rambus DRAM(RDRAM)

- 集成随机存储器(IRAM)

三、非易失性半导体存储器

对于非易失性半导体存储器,当停电时,所存储的内容不会丢失

1.分类

- 只读存储器(ROM):

- 掩膜式ROM,由芯片制造商在制造时写入内容

- 可编程的只读存储器(PROM):

- 有熔丝式PROM,刚出厂的产品熔丝是全部接通的,使用前,用户根据需要断开某些单元的熔丝(写入)

- 可擦可编程的只读存储器(EPROM):

- 产品出厂时,所有存储单元都不导通,当浮置栅注入电子后,存储单元将通导;当芯片用紫外线照射后,浮置栅上的电子将逸散,即整体擦除

- 可电擦可编程序只读存储器(E2PROM):

- 编程原理和EPROM同,但读写操作可按每个位或每字节进行(类似于SRAM),但每字节的写入周期要几毫秒,寿命为10万次

- 快擦除读写存储器(Flash Memory):

- 用电擦除,但只能整体擦除或分区擦除

四、存储器的组成与控制

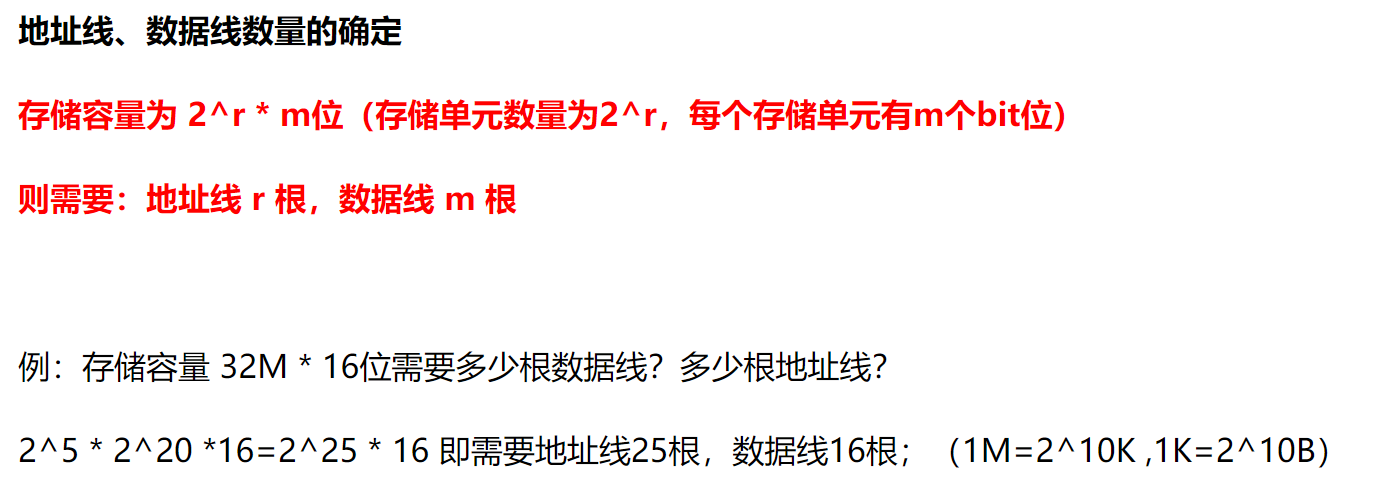

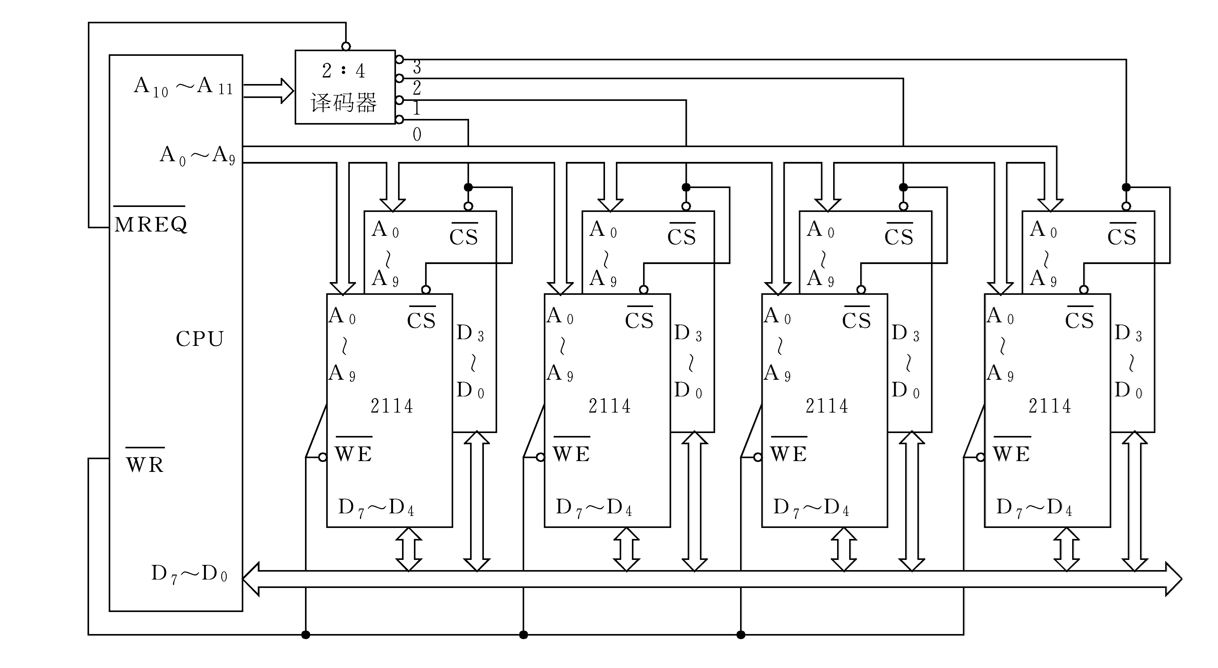

1.存储器容量扩展

-

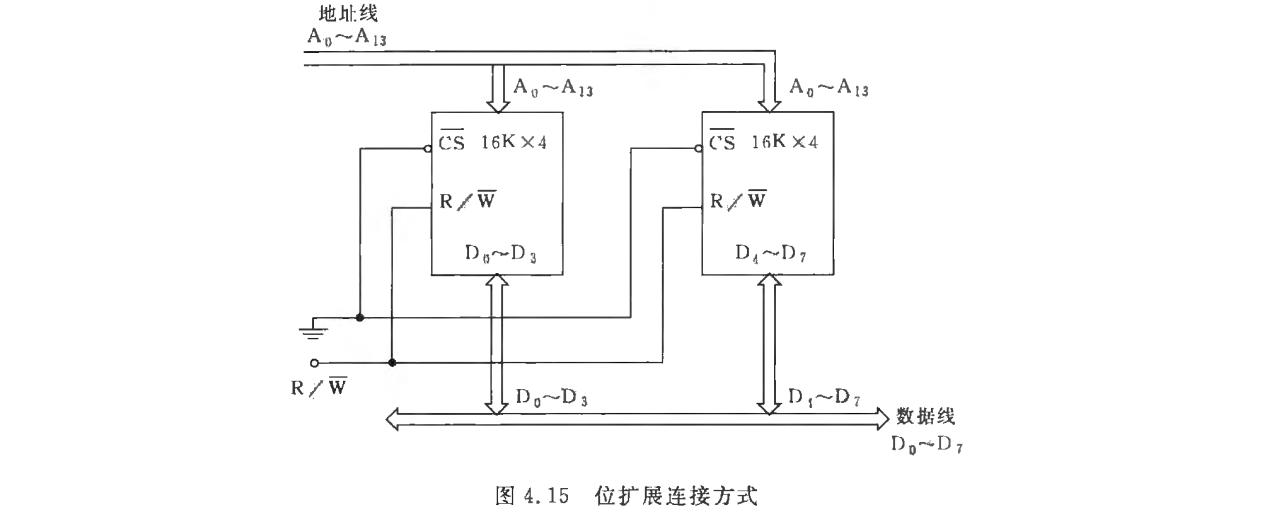

位扩展:位扩展指的是用多个存储器芯片对字长进行扩充,其连接方式是将多片存储器的地址、片选、读写控制端相应并联,数据端分别引出

-

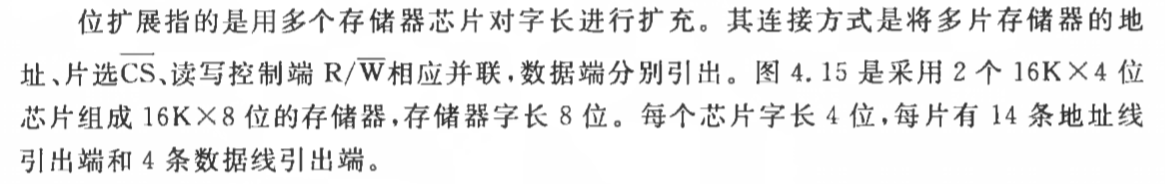

字扩展:字扩展指的是增加存储器中字的数量。静态存储器进行字扩展时,将各芯片的地址线、数据线和读写控制线相应并联,而由片选信号来区分各芯片的地址范围

-

字位扩展:实际存储器往往需要字向和位向同时扩充。一个存储器的容量为M×N位,若使用L×K位存储器芯片,那么这个存储器共需要(M/L)×(N/K)个存储器芯片

2.存储控制

- 存储器的附加电路:

- 多路地址转换

- 地址选通

- 读/写控制

- 刷新逻辑

- 通过定时刷新(读出)保证DRAM的信息不丢失

- 刷新周期:从上一次对整个存储器刷新结束到下一次依次对整个存储器全部刷新一遍为止所需要的时间。一般为2ms

- 分布式刷新:

- 假设存储器有1024行采取在2ms时间内分散地将1024行刷新一遍的方法

- 具体做法是将刷新周期除以行数,得到两次刷新操作的时间间隔t,利用逻辑电路每隔时间t产生一次刷新请求

3.存储校验线路

- 早期的计算机多采用奇偶校验电路,只有一位附加位,只能发现一位错而不能纠正

- 由于大规模集成电路的发展,主存储器的位数可以做得更多,使多数计算机的存储器有纠正错误代码的功能(ECC)

- 一般采用的海明码校验线路可以纠正一位错

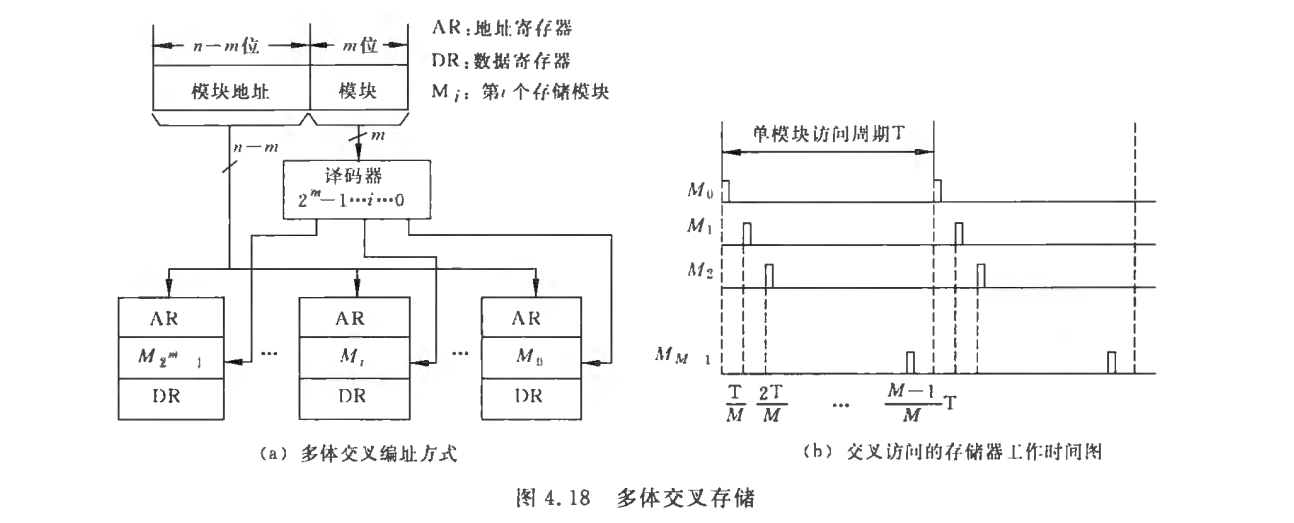

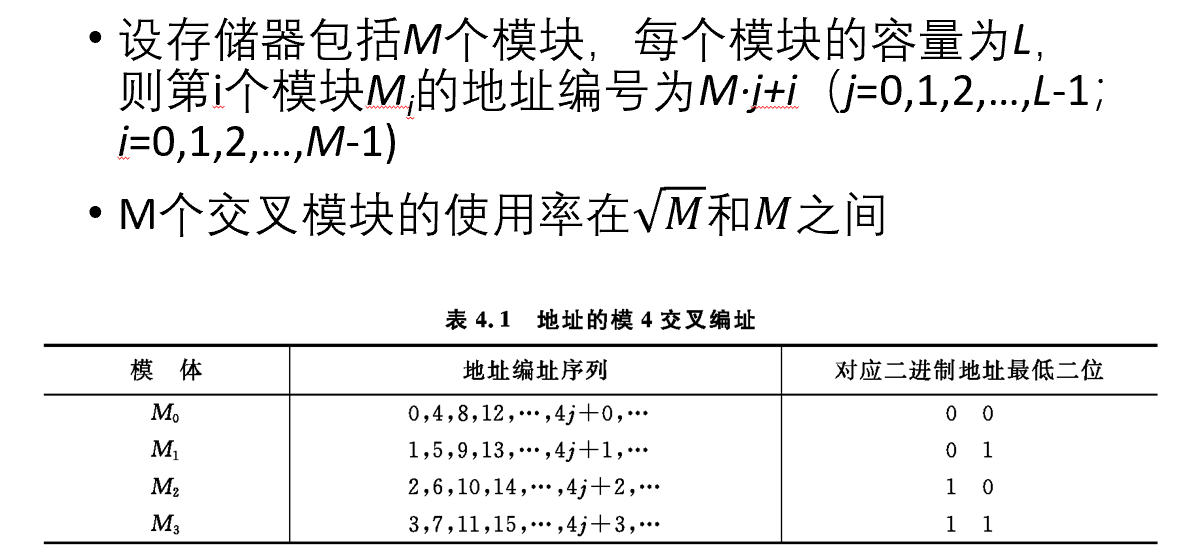

五、多体交叉存储器

- 存储体(存储模块)具有自己的读写线路、地址寄存器和数据寄存器

- 多模块存储器可以实现重叠与交叉存取

- 编码方式:

参考-《计算机组成于结构》-清华大学 王爱英