本文参考:

1. https://www.cnblogs.com/lkiller/p/4773235.html

2. AMBAAXI and ACE ProtocolSpecification

0.绪论

AXI是高级扩展接口,在AMBA3.0中提出,AMBA4.0将其修改升级为AXI4.0。AMBA4.0 包括AXI4.0、AXI4.0-lite、ACE4.0、AXI4.0-stream

AXI4.0-lite是AXI的简化版本,ACE4.0 是AXI缓存一致性扩展接口,AXI4.0-stream是ARM公司和Xilinx公司一起提出,主要用在FPGA进行以数据为主导的大量数据的传输应用。

1.简介

1.1 关于AXI协议

AMBA AXI协议支持支持高性能、高频率系统设计。

- 适合高带宽低延时设计

- 无需复杂的桥就能实现高频操作

- 能满足大部分器件的接口要求

- 适合高初始延时的存储控制器

- 提供互联架构的灵活性与独立性

- 向下兼容已有的AHB和APB接口

关键特点:

- 分离的地址/控制、数据相位

- 使用字节线来支持非对齐的数据传输

- 使用基于burst的传输,只需传输首地址

- 分离的读、写数据通道,能提供低功耗DMA

- 支持多种寻址方式

- 支持乱序传输

- 允许容易的添加寄存器级来进行时序收敛

- outstanding transactions (添加)

1.2 AXI架构

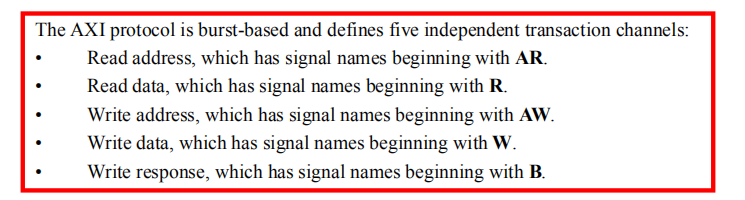

AXI协议是基于burst的传输,并且定义了以下5个独立的传输通道:读地址通道、读数据通道、写地址通道、写数据通道、写响应通道。

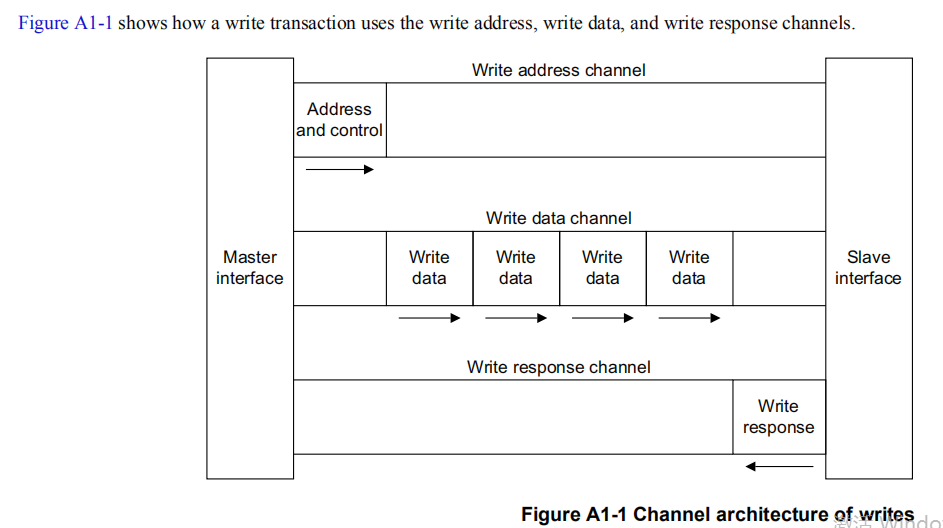

地址通道携带控制消息用于描述被传输的数据属性,数据传输使用写通道来实现“主”到“从”的传输,“从”使用写响应通道来完成一次写传输;读通道用来实现数据从“从”到“主”的传输。

AXI是基于VALID/READY的握手机制数据传输协议,传输源端使用VALID表明地址/控制信号、数据是有效的,目的端使用READY表明自己能够接受信息。

1.3 通道定义

Each of the five independent channels consists of a set of information signals and VALID and READY signals that provide a two-way handshake mechanism.

The information source uses the VALID signal to show when valid address, data, or control information is available on the channel. The destination uses the READY signal to show when it can accept the information. Both the read data channel and the write data channel also include a LAST signal to indicate the transfer of the final data item in a transaction.

读/写地址通道:读、写传输每个都有自己的地址通道,对应的地址通道承载着对应传输的地址控制信息。

读数据通道:读数据通道承载着读数据和读响应信号包括数据总线(8/16/32/64/128/256/512/1024bit) 和指示读传输完成的读响应信号。

写数据通道:写数据通道的数据信息被认为是缓冲(buffered)了的,“主”无需等待“从”对上次写传输的确认即可发起一次新的写传输。写通道包括数据总线(8/16...1024bit)和字节线(用于指示8bit 数据信号的有效性)。

写响应通道:“从”使用写响应通道对写传输进行响应。所有的写传输需要写响应通道的完成信号。

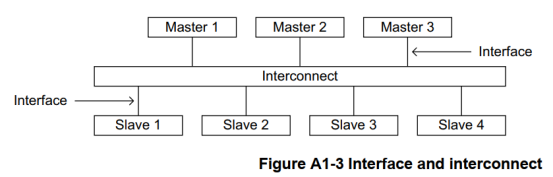

图 1-3 接口与互联

The AXI protocol provides a single interface definition, for the interfaces between:

- A master and the interconnect.

- A slave and the interconnect.

- A master and a slave

2. 信号

注意信号的来源和目的地。

2.1 全局信号

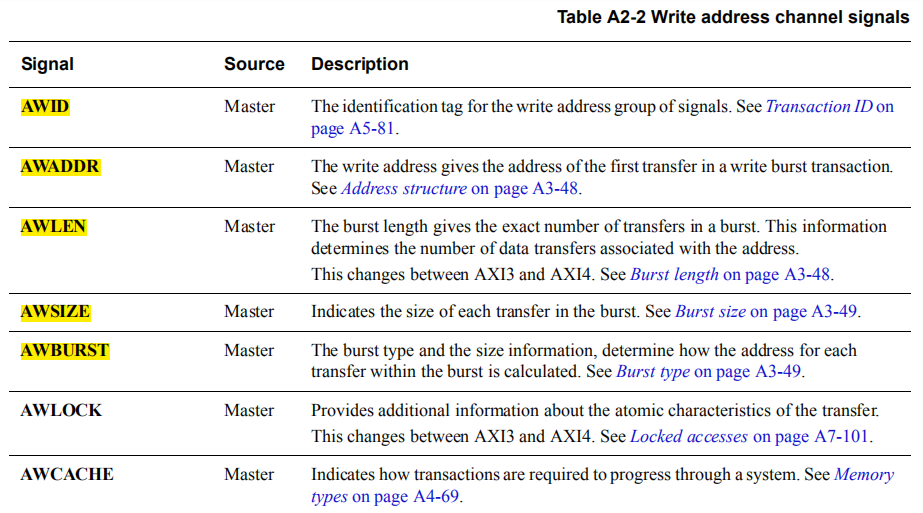

2.2 write address channel

自己这水平就关注AWID、AWADDR、AWLEN、AWSIZE、AWBURST、AWVALID、AWREADY这几个信号

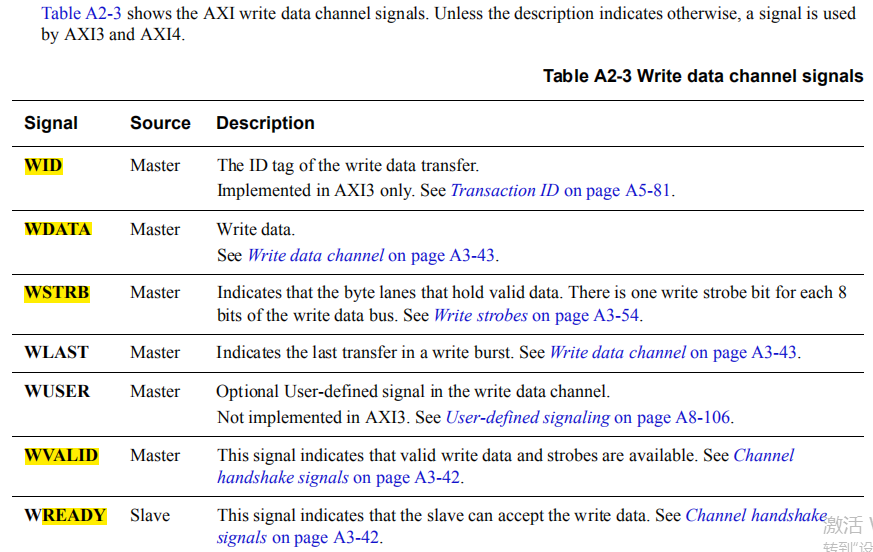

2.3 write data channel

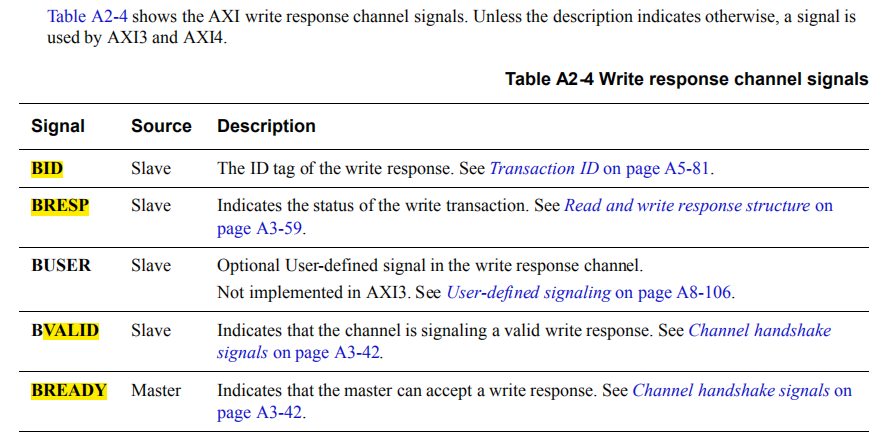

2.4 write response channel

2.5 read address

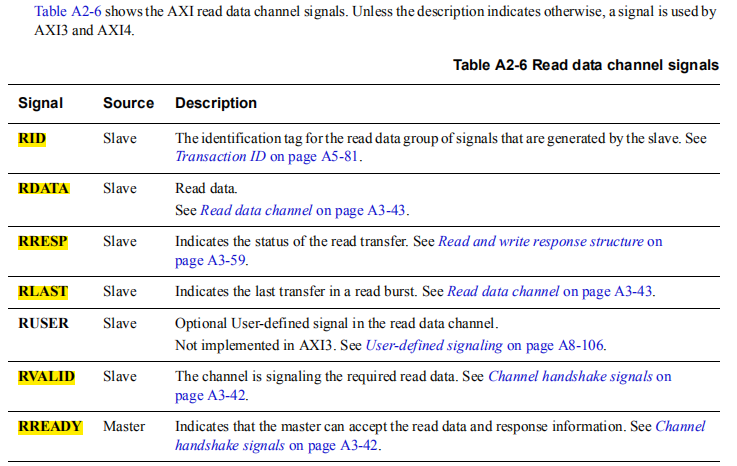

2.6 read data channel

(没在协议中看到低功耗接口)

3.信号接口要求

3.1时钟复位

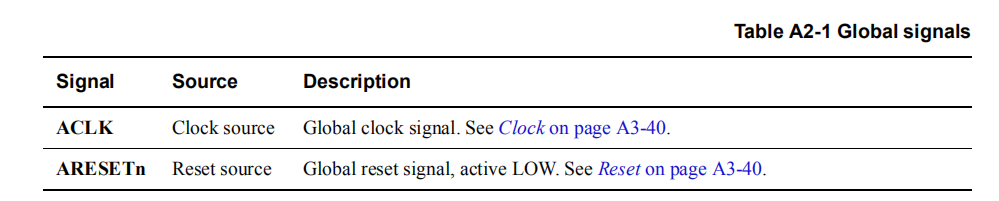

时钟

每个AXI组件使用一个时钟信号ACLK,所有输入信号在ACLK上升沿采样,所有输出信号必须在ACLK上升沿后发生。

复位

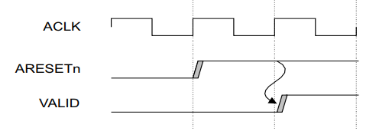

AXI使用一个低电平有效的复位信号ARESETn,复位信号可以异步断言,但必须和时钟上升沿同步去断言。

复位期间对接口有如下要求:①主机接口必须驱动ARVALID,AWVALID,WVALID为低电平;②从机接口必须驱动RVALID,BVALID为低电平;③所有其他信号可以被驱动到任意值。

在复位后,主机可以在时钟上升沿驱动ARVALID,AWVALID,WVALID为高电平。

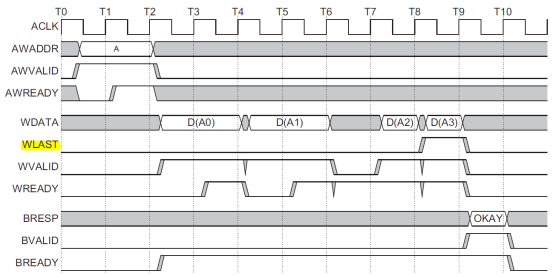

3.2基本读写传输

握手过程

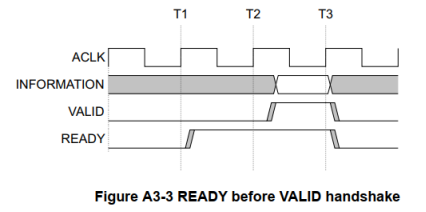

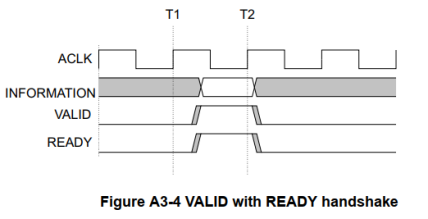

5个传输通道均使用VALID/READY信号对传输过程的地址、数据、控制信号进行握手。使用双向握手机制,传输仅仅发生在VALID、READY同时有效的时候。下图是几种握手机制:(看图,图中很清楚)

通道信号要求

通道握手信号:每个通道有自己的xVALID/xREADY握手信号对。

写地址通道:

当主机驱动有效的地址和控制信号时,主机可以断言AWVALID,一旦断言,需要保持AWVALID的断言状态,直到时钟上升沿采样到从机的AWREADY。AWREADY默认值可高可低,推荐为高(如果为低,一次传输至少需要两个周期,一个用来断言AWVALID,一个用来断言AWREADY);当AWREADY为高时,从机必须能够接受提供给它的有效地址。

写数据通道:

在写突发传输过程中,主机只能在它提供有效的写数据时断言WVALID,一旦断言,需要保持断言状态,直到时钟上升沿采样到从机的WREADY。WREADY默认值可以为高,这要求从机总能够在单个周期内接受写数据。主机在驱动最后一次写突发传输是需要断言WLAST信号。

写响应通道:

从机只能它在驱动有效的写响应时断言BVALID,一旦断言需要保持,直到时钟上升沿采样到主机的BREADY信号。当主机总能在一个周期内接受写响应信号时,可以将BREADY的默认值设为高。

读地址通道:

当主机驱动有效的地址和控制信号时,主机可以断言ARVALID,一旦断言,需要保持ARVALID的断言状态,直到时钟上升沿采样到从机的ARREADY。ARREADY默认值可高可低,推荐为高(如果为低,一次传输至少需要两个周期,一个用来断言ARVALID,一个用来断言ARREADY);当ARREADY为高时,从机必须能够接受提供给它的有效地址。

读数据通道:

只有当从机驱动有效的读数据时从机才可以断言RVALID,一旦断言需要保持直到时钟上升沿采样到主机的BREADY。BREADY默认值可以为高,此时需要主机任何时候一旦开始读传输就能立马接受读数据。当最后一次突发读传输时,从机需要断言RLAST。

3.3 通道间关系

AXI协议要求通道间满足如下关系:

- 写响应必须跟随最后一次burst的的写传输

- 读数据必须跟随数据对应的地址

- 通道握手信号需要确认一些依耐关系

通道握手信号的依耐关系

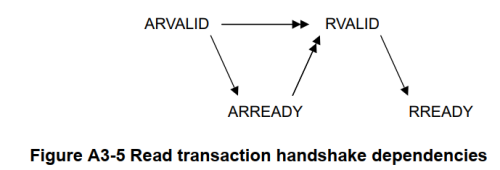

为防止死锁,通道握手信号需要遵循一定的依耐关系。①VALID信号不能依耐READY信号。②AXI接口可以等到检测到VALID才断言对应的READY,也可以检测到VALID之前就断言READY。下面有几个图表明依耐关系,单箭头指向的信号能在箭头起点信号之前或之后断言;双箭头指向的信号必须在箭头起点信号断言之后断言。

Read transaction dependencies

AXI3 write transaction dependencies

因为写的数据是被缓存的,M不需要等到S接受完数据就可以发送下一个数据,所以AW***信号和W***信号没有强制的先后关系

AXI4 and AXI5 write transaction dependencies

AXI4 and AXI5 define an additional slave write response dependency. The slave must wait for AWVALID, AWREADY, WVALID, and WREADY to be asserted before asserting BVALID.

The slave must also wait for WLAST to be asserted before asserting BVALID. This wait is because the writeresponse, BRESP, must be signaled only after the last data transfer of a write transaction

3.3 传输结构

3.3.1 地址结构

AXI协议是基于burst的,主机只给出突发传输的第一个字节的地址,从机必须计算突发传输后续的地址。突发传输不能跨4KB边界 (防止突发跨越两个从机的边界,也限制了从机所需支持的地址自增数)。

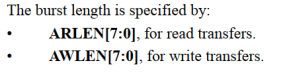

Burst Length

ARLEN[7:0]决定读传输的突发长度,AWLEN[7:0]决定写传输的突发长度。AXI3只支持1~16次的突发传输(Burst_length=AxLEN[3:0]+1),AXI4扩展突发长度支持INCR突发类型为1~256次传输,对于其他的传输类型依然保持1~16次突发传输(Burst_Length=AxLEN[7:0]+1)。

burst传输具有如下规则:

- wraping burst ,burst长度必须是2,4,8,16

- burst不能跨4KB边界

- 不支持提前终止burst传输

所有的组件都不能提前终止一次突发传输。然而,主机可以通过解断言所有的写的strobes来使非所有的写字节来减少写传输的数量。读burst中,主机可以忽略后续的读数据来减少读个数。也就是说,不管怎样,都必须完成所有的burst传输。

注:对于FIFO,忽略后续读数据可能导致数据丢失,必须保证突发传输长度和要求的数据传输大小匹配。

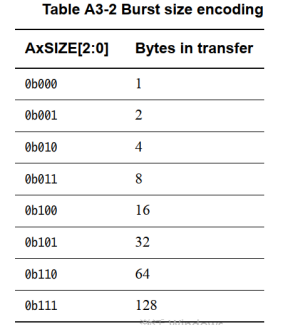

Burst Size

The maximum number of bytes to transfer in each data transfer, or beat, in a burst, is specified by:

• ARSIZE[2:0], for read transfers.

• AWSIZE[2:0], for write transfers.

Burst type

FIXED:突发传输过程中地址固定,用于FIFO访问

INCR:增量突发,传输过程中,地址递增。增加量取决AxSIZE的值。

WRAP:回环突发,和增量突发类似,但会在特定高地址的边界处回到低地址处。回环突发的长度只能是2,4,8,16次传输,传输首地址和每次传输的大小对齐。最低的地址整个传输的数据大小对齐。回环边界等于(AxSIZE*AxLEN)。

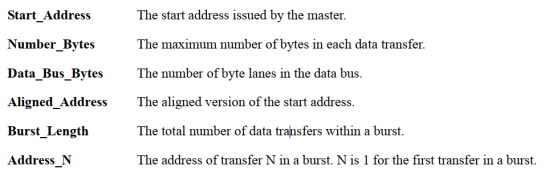

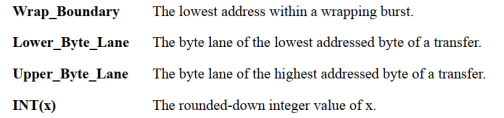

These equations determine addresses of transfers within a burst:

- Start_Address = AxADDR

- Number_Bytes = 2 ^ AxSIZE

- Burst_Length = AxLEN + 1

- Aligned_Address = (INT(Start_Address / Number_Bytes)) × Number_Bytes

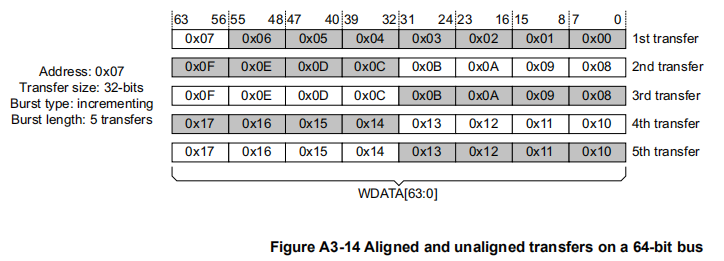

3.3.2 数据读写结构

Write strobe(写选通)

WSTRB[n:0]对应于对应的写字节,WSTRB[n]对应WDATA[8n+7:8n]。WVALID为低时,WSTRB可以为任意值,WVALID为高时,WSTRB为高的字节线必须指示有效的数据。

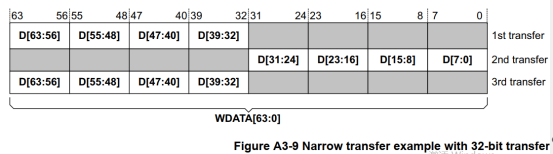

窄传输

当主机产生比它数据总线要窄的传输时,由地址和控制信号决定哪个字节被传输:

INCR和WRAP,不同的字节线决定每次burst传输的数据,FIXED,每次传输使用相同的字节线。

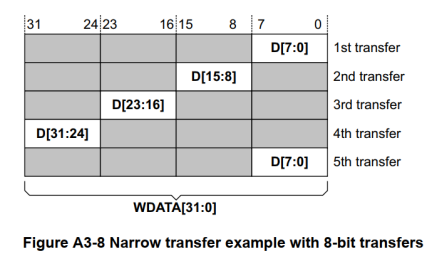

下图给出了5次突发传输,起始地址为0,每次传输为8bit,数据总线为32bit,突发类型为INCR。

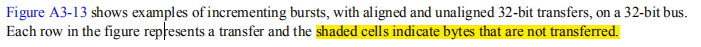

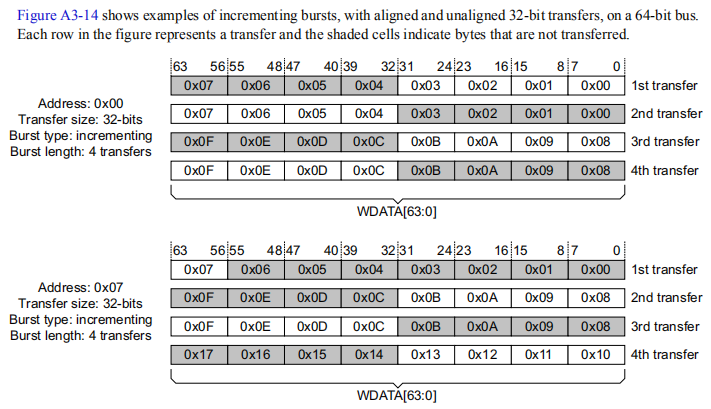

非对齐传输

主机可以

①使用低位地址线来表示非对齐的起始地址;

②提供对齐的起始地址,使用字节线来表示非对齐的起始地址。

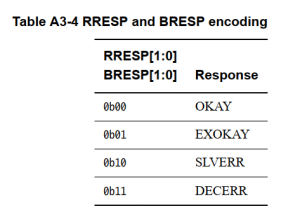

读写响应结构

读传输的响应信息是附加在读数据通道上的,写传输的响应在写响应通道。

RRESP[1:0],读传输

BRESP[1:0],写传输

OKAY('b00):正常访问成功

EXOKAY('b01):Exclusive 访问成功

SLVERR('b10):从机错误。表明访问已经成功到了从机,但从机希望返回一个错误的情况给主机。

DECERR('b11):译码错误。一般由互联组件给出,表明没有对应的从机地址。

OKAY, normal access success

An OKAY response indicates any one of the following:

• The success of a normal access.

• The failure of an exclusive access.

• An exclusive access to a slave that does not support exclusive access.

OKAY is the response for most transactions.

4. AXI transaction

AXI中有AXI ID作为transaction identifier,相同ID 的transaction需要in order,不同ID 的transaction可以out order。

By using AXI IDs, a master can issue transactions without waiting for earlier transactions to complete. This can improve system performance, because it enables parallel processing of transactions。这个就是Outstanding transactions,master不需要要等待slave READY。

4.1 Transactions ordering

master通过AWID或者ARID来表明它的ordering requirement,具体如下:

- 来自不同master的Transactions 可以任意order;

- 来自相同master但ID不同的Transactions ,可以任意order;

- 连续读操作有相同的ARID,需要按照master发出地址的顺序返回数据;

- 连续写操作有相同的AWID,需要按照master发出地址的顺序完成传输;

- 读写操作之间没有order requirement;

Read ordering

At a master interface, read data from transactions with the same ARID value must arrive in the order that the master issued the addresses. Data from read transactions with different ARID values can arrive in any order.

The slave must ensure that the RID value of any returned data matches the ARID value of the address to which it is responding.

Read and write interaction

A master can only consider the earlier transaction is complete when:

• For a read transaction, it receives the last of the read data.

• For a write transaction, it receives the write response.

Note

Typically, when writing to a peripheral, a master must wait between read and write transactions that must be ordered

Interconect using ID identifier

For read data, the interconnect uses the additional bits of the RID identifier to determine which master port the read data is destined for. The interconnect removes these bits of the RID identifier before passing the RID value to the correct master port