转自:http://m.blog.csdn.net/article/details?id=50405060

1. 64B/66B编码技术

64B/66B编码技术是IEEE 802.3工作组为10G以太网提出的,目的是减少编码开销,降低硬件的复杂性,并作为8B/10B编码的另一种选择,以支持新的程序和数据。当前,64B/66B编码主要应用于Fiber Channel 10GFC和16GFC、10G以太网、100G以太网、10G EPON、InfiniBand、Thunderbolt和Xilinx的Aurora协议。

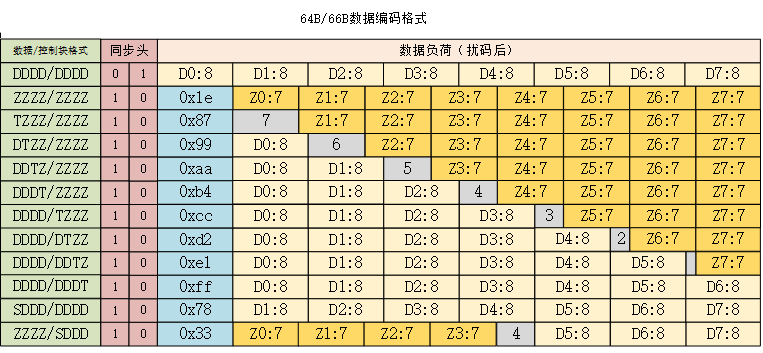

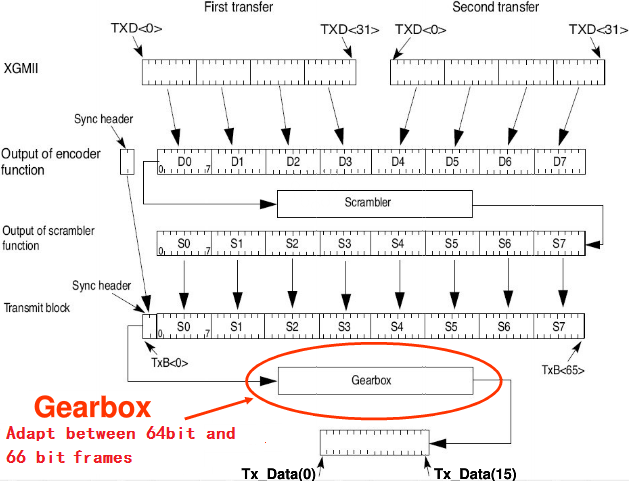

64B/66B编码将64bit数据或控制信息编码成66bit块传输,66bit块的前两位表示同步头,主要由于接收端的数据对齐和接收数据位流的同步。同步头有“01”和“10”两种,“01“表示后面的64bit都是数据,“10”表示后面的64bit是数据和控制信息的混合,其中紧挨着同步头的8b是类型域,后面的56bit是控制信息或者数据或者两者的混合。64B/66B编码格式图如下图所示,其中D表示数据编码,每个数据码8bit;Z表示控制码,每个控制码7bit;S表示包的开始,T表示包的结束。S只会出现在8字节中的第0和第4字节,T能够出现在任意的字节。除同步码外,64bit的数据必须经过扰码以后才能进行传输。64B/66B编码所使用的 扰码器为X58+X39+1.

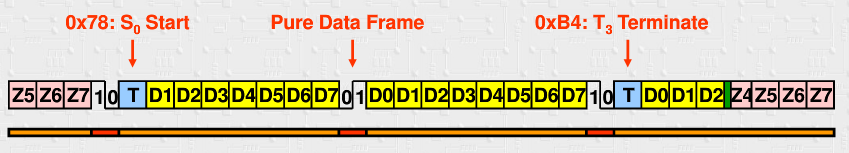

一个18 bytes的数据块的传输过程如下图所示:

2. 扰码传输技术

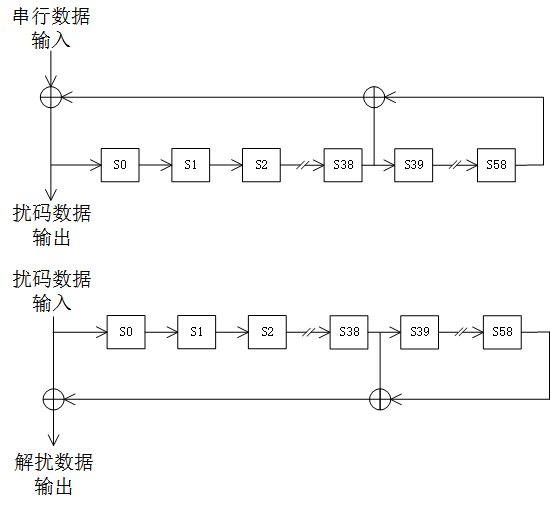

扰码是一种将数据重新排列或者进行编码以使其随机化的发布方法,主要作用是将数字通信中的"0"和"1"分布随机化,从而使比特信息模式被随机化,进一步减轻了抖动个码间串扰,提高了通信的可靠性。从本质上讲,扰码正是为了达到上述目的而在待传输数据进入信道传输之前,对其进行的比特层的随机化处理过程,与扰码过程相对应的解随机化过程称之为解扰。

扰码的数学原理使用了多项式,多项式的选择通常是基于扰码的特性,包括生成数据的随机度,以及打乱连0和连1的能力。一个简单的扰码器包含一组排列好的触发器,用于移位数据流。大部分的触发器只需要简单地输出下一个比特流即可,但是在某些复杂的扰码电路中,触发器需要与数据流中的历史比特进行逻辑运算(与和或运算)。基本的扰码电路如下所示:

64B/66B编码过程如下图所示: