FPGA 主时钟约束---primary clocks

个人的理解,FPGA做时钟约束的主要目的是给布局布线过程一个指导意义。

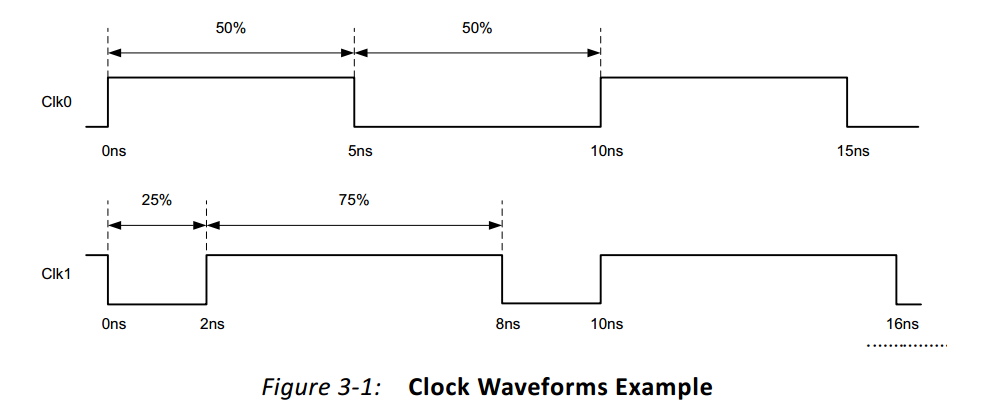

注:周期的参数值为ns

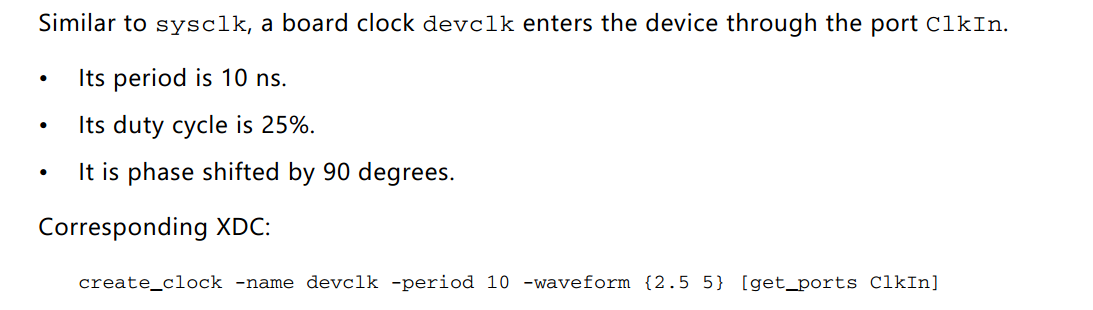

waveform 里面的第一个参数为波形第一个上升沿的时间,第二参数为低一个下降沿的时间。

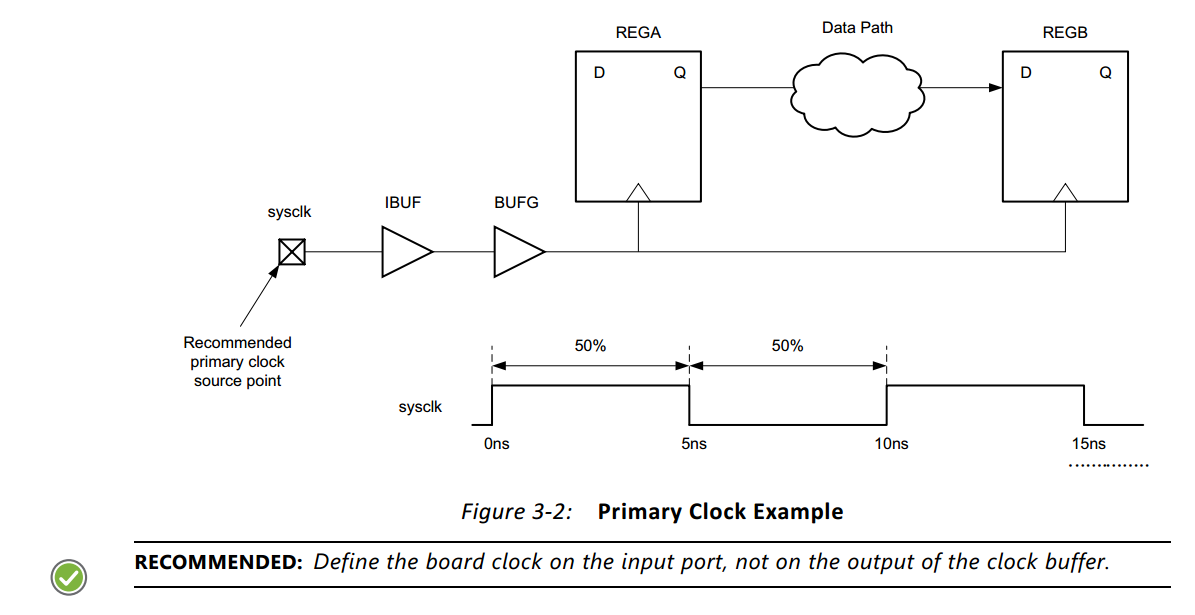

primary clock 具有时间零点的参考作用。

primary clock 必须最先被定义。

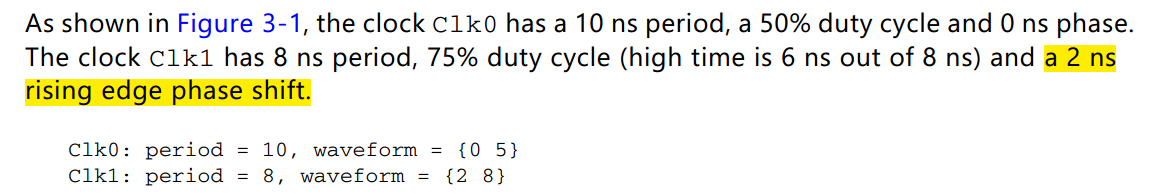

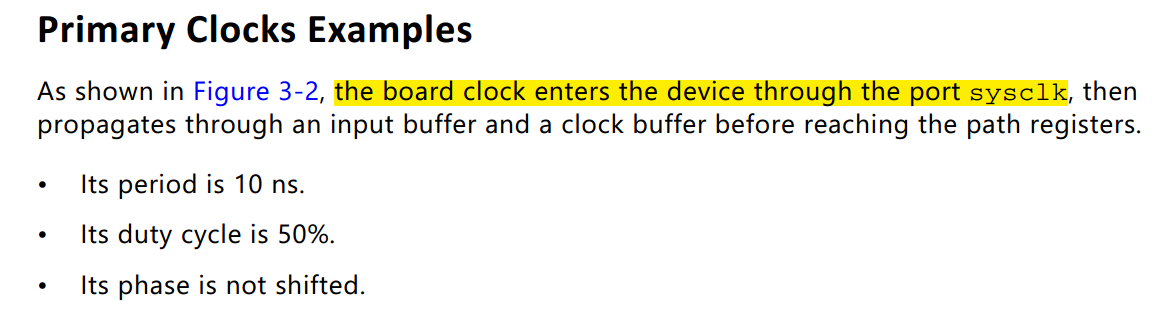

关于定义primary clock 的例子

其中,waveform中的两个信息就指出了占空比和相移。

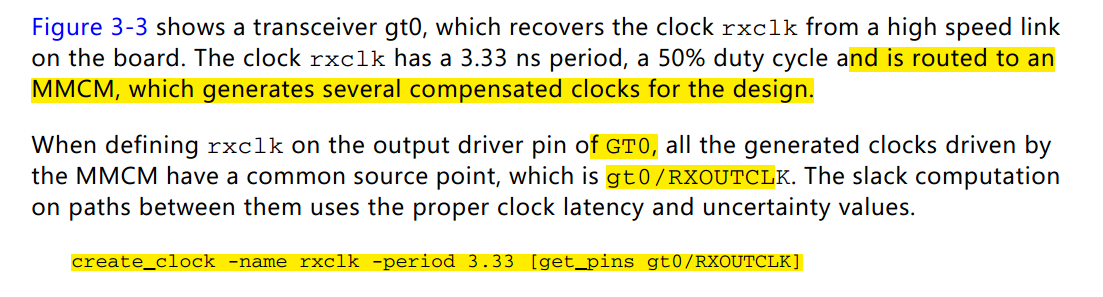

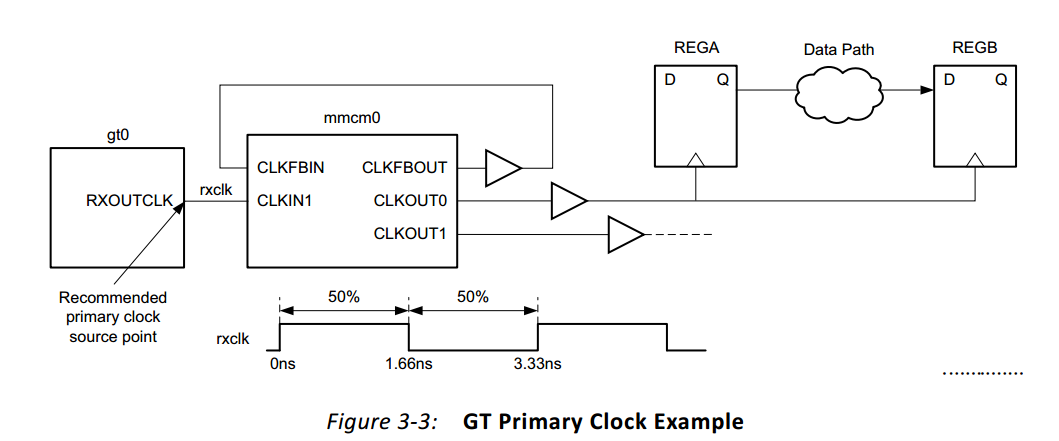

GT 高速恢复时钟的定义

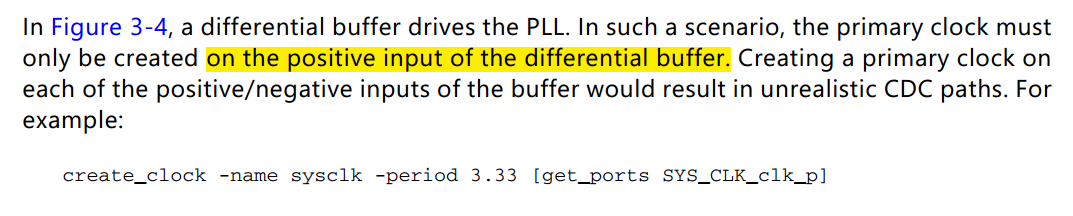

差分时钟的定义,只需要定义p_clock