前言

开发一款芯片,首先我们需要确定制造它想要实现的目的,也就是想要实现的功能,以及功能与功能间沟通的接口;这也就是我们常说的架构;

当架构确定好后,下一步就是确定这些功能与接口的实现执行方式;

这些功能与接口的具体实现流程就是芯片的核心,所以我们将这些具体实现流程称之为芯片的内核;

STM32系列芯片采用ARM架构下的cortex-M系列内核来具体执行和实现芯片的功能;

1 ARM架构

ARM(Advanced RISC Machine)高级 精简指令集 处理器,简称ARM架构;也是ARM公司起名的由来;为主流芯片架构之一;

| CPU架构 | 代表芯片 | 指令集架构 | 功能 |

| ARM | ARM | RISC指令集 | 主要用于移动,嵌入式领域;逻辑门少,发热低,so功耗低;搭配哈佛存储结构使用; |

| X86 | intel,AMD | CISC指令集 | 主要是用在电脑CPU上,性能高,速度快;搭配冯诺依曼存储结构使用; |

| MIPS | 龙芯 | RISC指令集 | 用于部分音频处理器和网络设备上,市场极小;后来 |

ARM公司作为IP核提供商,专注于ARM处理器的IP核出售业务;在推出ARM11内核之后,之后推出的内核分为三类,分别如下

1.1 cortex-A系列内核:application系列,专注于高端消费类电子,诸如高通,MTK等的手机芯片;

1.2 cortex-R系列内核:real-time系列,专注于要求实时性的领域,诸如航空航天之类的;

1.3 cortex-M系列内核:micro-controller系列,专注于中低端的嵌入式产品,也就是本文接下来要说的系列了;

2 CPU的存储结构

cortex-m3为cortex系列推出的第一个内核,发布于2005年;本文就以cortex-m3举例把;

cortex-m3为32位处理器内核,支持小端模式(常用)和大端模式(不建议);有些指令只使用小端模式且不可更改;

| endian模式 | 功能 | data[31:0]=0x87654321, 地址:0x10,0x11,0x12,0x13 |

| 小端模式 | 数据的低位存放在地址低位中 | data[7:0]存放在0x10中 |

| 大端模式 | 数据的高位存放在地址低位中 | data[31:24]存放在0x10中 |

cortex-m3的数据总线,指令总线,寄存器都是32位的,采用哈佛结构总线;

那么什么是哈佛总线结构呢?既然遇到了,就在这里补充一下温馨小提示把;

2.1 CPU的存储结构

2.1.1 哈佛结构:指令寄存器和数据寄存器存放在不同的内存里,需要分别寻址的CPU结构;

1)代码编译之后相当于指令,这些指令通常会固定存放在单片机的rom的寄存器里,使用指令总线来顺序寻址 指令寄存器;

相当于指令寄存器全部划分在一块固定的区域,指令总线和数据总线同时操作该区域的指令寄存器;

2)单片机执行过程中的数据存放在ram的寄存器里,使用地址总线对需要操作的数据寄存器进行寻址,然后使用数据总线传递数据;

相当于数据寄存器全部划分在一块固定的区域,地址总线和数据总线可以同时操作该区域的数据寄存器;

优势:代码安全性较高,效率较高;

2.1.2 冯诺依曼结构:指令寄存器和数据寄存器存放在相同的内存里,不需要分别寻址的CPU结构;

代码A编译之后存放在内存中,该代码A使用的数据A存放在代码A地址后;新的代码B继续放在数据A之后,然后再存放数据B...

指令寄存器的存储区域和数据寄存器的存储区域混在一块区域,也就是说指令总线和地址总线是相同的总线,需要分时复用;

冯诺依曼是早期的cpu结构,执行的速度受存储器速度的限制;优势的话。。。可能在存储器速度很快的情况下很快把。。。

2.2 ARM存储器地址映射

ARM的地址总线为32bits;所以存储器的寻址空间为4G;寻址内存单位约定俗成为byte;

CM3存储器地址映射在所有的cortex-m3内核的芯片上都是相同的,方便了不同芯片程序的裁剪和移植;

| 地址 | 大小 | 类型 | 功能 |

| 0x0000 0000-0x1fff ffff | 512M bytes | ROM | 代码存储区 |

| 0x2000 0000-0x3fff ffff | 512M bytes | SRAM | |

| 0x4000 0000-0x5fff ffff | 512M bytes | 用于存储片上外设 | |

| 0x6000 0000-0x9fff ffff | 1G bytes | 外部RAM | 扩展外部存储器的寻址 |

| 0xa000 0000-0xdfff ffff | 1G bytes | 扩展片外的外设 | |

| 0xe000 0000-0xffff ffff | 512M bytes | 内核相关寄存器,片上调试组件等,AHB总线,APB总线 |

AHB总线只用于CM3内部的AHB外设,如NVIC,FPB,DWT和ITM;

APB总线既用于CM3内部的APB外设,也用于片外扩展的外设;

3 cortex-M3内核

3.1 cortex框图

cortex-m3只使用thumb-2指令集;thumb-2指令集包含32bit指令和16bit指令;thumb指令集只包含16bit指令;

对于M3内核,橙色是内核主要的功能执行框图,紫色为调试组件,绿色为存储保护单元,蓝色为内部总线与外设的接口;

下面的框图应该有各种总线;I-code总线负责指令,D-code总线负责查表等操作;按最佳执行速度进行优化;

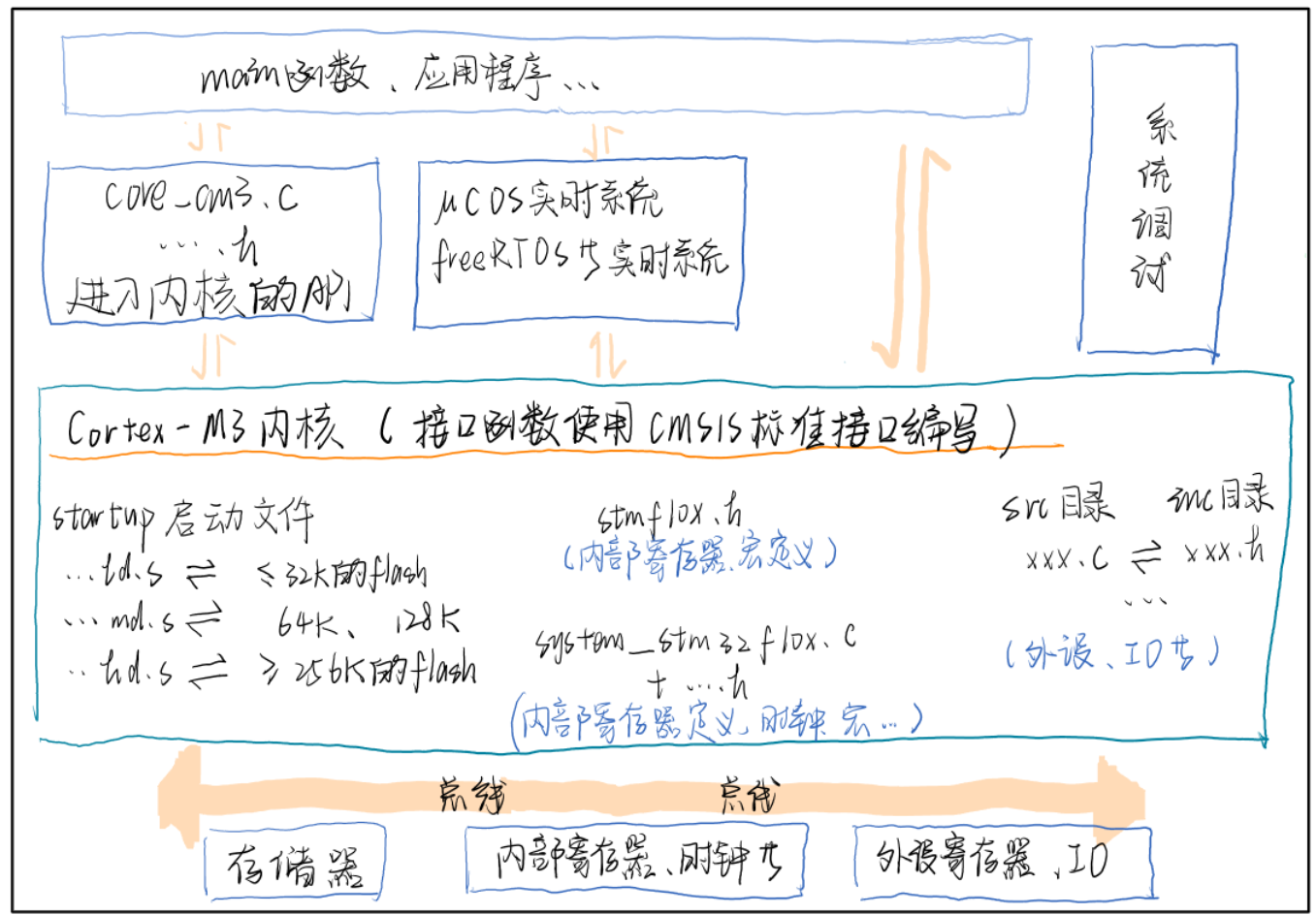

3.1.2 CMSIS 软件接口标准

CMSIS全称Cortex-Mx software interface standard,是API接口标准;以下为STM32芯片的core cm3内核的代码架构示意图;

Libraries目录下内核代码,将底层寄存器操作封装成API函数,函数格式符合CMSIS标准的格式;

3.2 register bank寄存器

CM3内核拥有一个寄存器组,该寄存器组内共有16个寄存器;以及一些特殊功能寄存器;

3.2.1 寄存器组

| 寄存器 | 寄存器名称 | 可访问指令 | 功能 |

| R0,...,R7 | 通用寄存器 | thumb, thumb-2 | 数据操作,Low registers复位后初始值不定 |

| R8,...,R12 | 通用寄存器 | thumb-2 | 数据操作,High registers复位后初始值不定 |

| R13 | 主堆栈指针 MSP | thumb-2 | main_SP,复位后缺省使用的堆栈指针,用于操作系统内核以及异常处理例程(包括中断服务例程); |

| 进程堆栈指针 PSP | thumb-2 | process_SP,由用户的应用程序代码使用(用户代码不处于中断时); | |

| R13寄存器的最低两位被硬件置0,所以内存的地址总是4字节对齐;堆栈指针的切换由硬件自动完成; | |||

| R14 | 连接寄存器 LR | thumb-2 | 调用子函数时,用来存储主调函数的地址;多级调用时会将主调函数的地址存到堆栈中; |

| R15 | 程序计数器 PC | thumb-2 | 存储当前程序运行到的程序地址。如果修改它的值,就能改变程序的执行流; |

3.2.2 特殊功能寄存器

特殊功能寄存器组没有存储器地址,只能使用MRS(读)和MSR(写)指令访问;

| 寄存器 | 寄存器名称 |

功能 |

|||

|

xPSR

|

程序状态字

寄存器组

|

APSR

|

APSR 应用程序状态寄存器:记录 ALU 标志,

IPSR 中断号状态寄存器:当前正服务的中断号,

EPSR 执行状态寄存器:程序执行状态

|

||

|

IPSR

|

|||||

| EPSR | |||||

|

PRIMASK

|

中断屏蔽

寄存器组

|

1bit |

除能所有中断,NMI和hard fault除外; 缺省为0,不除能; |

目的:让实时性要求高的任务能够顺利执行 |

|

|

FAULTMASK

|

1bit |

除能所有fault,NMI不可屏蔽中断除外; 缺省为0,不除能; |

|||

|

BASEPRI

|

9bit

|

除能所有优先级不高于某个阈值的所有中断

|

|||

|

CONTROL

|

控制

寄存器

|

CONTORL[1]

|

1bit |

为0时,都使用MSP堆栈指针;为缺省值;

为1时,thread使用PSP堆栈指针,

handler使用MSP指针;

|

handler模式时,为0,都是使用MSP堆栈, thread模式时,为0或1,分别复用为MSP/PSP堆栈; |

| CONTROL[0] |

1bit

|

0:thread模式处于privileged特权级权限; 1:thread模式处于user级权限 |

当模式处于thread时,使用CONTROL[0]来配置权限 | ||

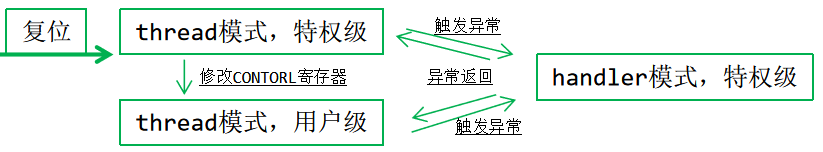

3.3内核模式

| 操作模式 | 操作权限 | 操作程序 | 使用的堆栈指针 | 操作配置 |

| thread 线程模式 | 特权级,用户级 | 普通应用程序的操作模式 | PSP/MSP |

根据操作模式和操作权限配置CONTROL[1:0]来修改状态 |

| handler 处理模式 | 特权级 | 异常服务程序的操作模式 | MSP |

| 编号 | 类型 | 优先级 | NVIC表偏移地址 | 功能 |

| 0 |

NA

|

NA

|

0x00

|

表示没有异常在运行,当前地址初始值为MSP复位后的初始值;

|

| 1 | Reset_Handler | -3(最高) | 0x04 | 上电复位 |

| 2 | NMI | -2 | 0x08 | 不可屏蔽中断(外部NMI引脚输入) |

| 3 | hard fault | -1 | 0x0C | 使能所有被除能的fault中断为hard fault |

| 4 | MemManage fault | 可编程 | 0x10 |

存储器管理fault,MPU 访问犯规以及访问非法位置

|

| 5 |

总线 fault

|

0x14 |

总线错误(预取流产(Abort)或数据流产)

|

|

| 6 |

用法(usage)

Fault

|

0x18 |

程序错误的异常 ,通常为指令无效或非法状态转换

|

|

| 7-10 |

保留

|

NA

|

0x1C-0x28

|

NA

|

| 11 |

SVCall

|

可编程

|

0x2C

|

系统服务调用

|

| 12 |

调试监视器

|

0x30 |

调试监视器 (断点,数据观察点,或者是外部调试请求)

|

|

| 13 |

保留

|

NA

|

0x34

|

NA

|

| 14 |

PendSV

|

可编程 | 0x38 |

为系统设备而设的“可悬挂请求”(pendable request)

用来实现中断嵌套时,应把PendSV的优先级编程为最低;

|

| 15 |

SysTick

|

0x3C |

系统滴答定时器

|

|

| 16 |

IRQ #0

|

0x40 |

外中断#0

|

|

| 17 |

IRQ #1

|

0x44 |

外中断#1

|

|

| ... | ... | ... | ... | ... |

| 255 |

IRQ #239

|

可编程 | 0x3FF |

外中断#239

|

| CM3支持11个系统异常中断,5个保留类型,240个外部中断;具体使用看芯片厂商的配置; | ||||

|

Cortex‐M3 在进入异常服务例程时,自动压栈了 R0‐R3, R12, LR, PSR 和 PC,并且在返回时自动弹出它们

|

||||