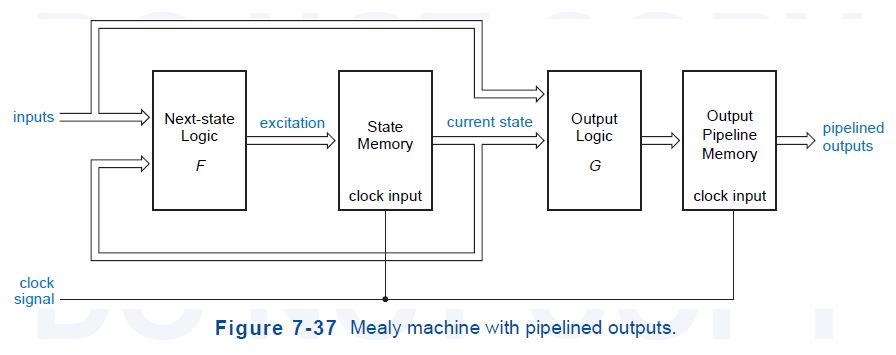

上图表示的就是数字电路设计中常用的时钟同步状态机的结构。其中共有四个部分产生下一状态的组合逻辑F、状态寄存器组、输出组合逻辑G、流水线输出寄存器组。如果状态寄存器组由n个寄存器组成,就可以记忆2^n个状态。并且所有的寄存器都连接在一个共同的时钟信号上,现代电路设计通常采用正跳变沿D触发器。

下一个状态=F(当前状态,输入信号)

输出信号=G(当前状态,输入信号)

通常的状态机是没有Pipeline output的,并且可以分为两类:

Mealy型:时序逻辑的输出不但取决于状态还取决于输入,输出信号=G(当前状态,输入信号)

Moore型:时序逻辑的输出只取决于当前状态,与输入无关,输出信号=G(当前状态)

这两种电路结构除了在输出电路有些不同外,其他地方都是相同的。在实际工作中,大部分状态机都是Mealy状态机。

1)在设计高速通路时,常常有必要使得状态机的输出和时钟几乎完全同步。有一个办法就是把状态寄存器组的状态变量直接用做输出,为此可能在状态编码时要多费些脑力,也有可能要多用几个寄存器。这种设计思路,在高速状态机电路常常使用,称为输出编码的状态指定。这种状态机就属于Moore类型,但是输出部分没有组合逻辑只有连线。

2)设计高速状态机还有另一种办法,如图所示,在逻辑输出后面加上一组与时钟同步的寄存器组作为流水线输出寄存器组,这样可以使得G的所有输出信号在下一个时钟跳变沿的同时存入寄存器组,即实现同步输出,将这种输出叫做流水线化的输出。