VHDL设计模型

数据流模型:直接使用基本门和扩展门描述

行为模型:通过输入输出响应描述

结构化模型:通过低级器件的内联实现

VHDL程序结构

Entity(实体)

Architecture(结构体)

Configuration(配置)

Package(包)、Library(库)

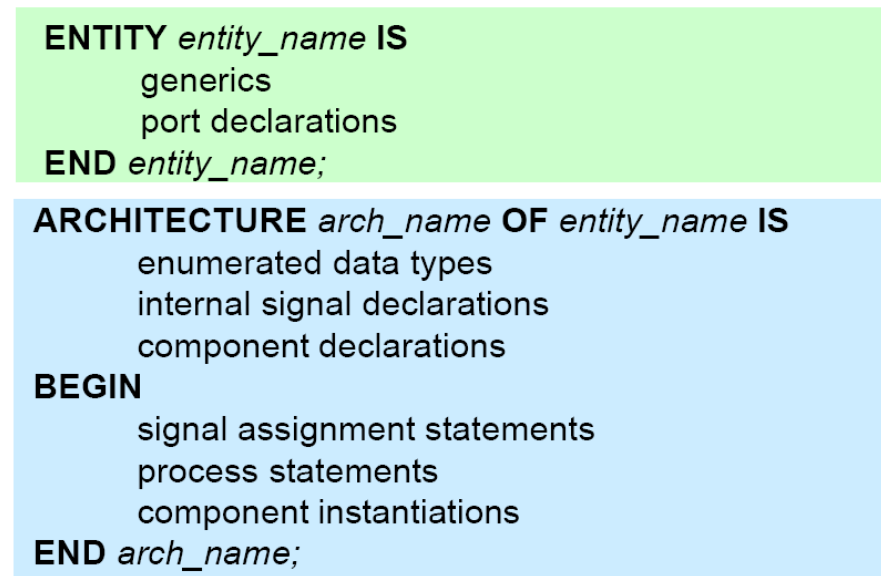

Entity(实体)

Entity实体定义格式:

Entity <entity name> is Generic Declarations Port Declarations End Entity <entity name>

Entity name :

字母为开头,其余可由字母、数字、下划线组成。

类属声明(Generic Declarations):

作用:用于模型传递信息。

类属里常量声明格式:

constant 常量名:数据类型 := 设定值;

数据类型:integer,time,string

Generic (N : integer := 16 )

端口声明(Port Declarations)

定义格式:

<Class> Object_name : <Mode> <Type>;

<Class> : Signal , (Constant , Variable)

<Mode> :输入方向,in(输入),out(输出),inout(双向),buffer(输出、可反馈)

<Type> :数据类型,如[ std_logic , std_logic_vector (7 downto 0) ]

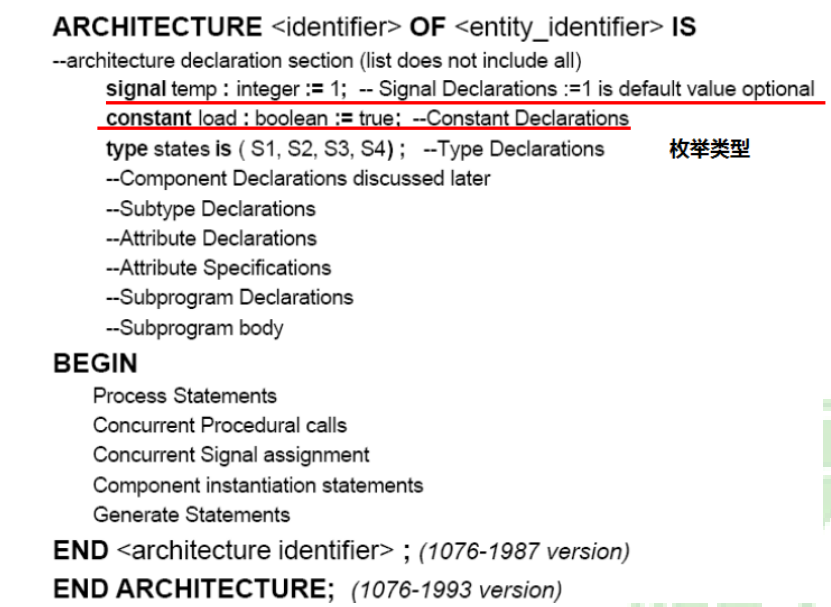

Architecture(结构体)