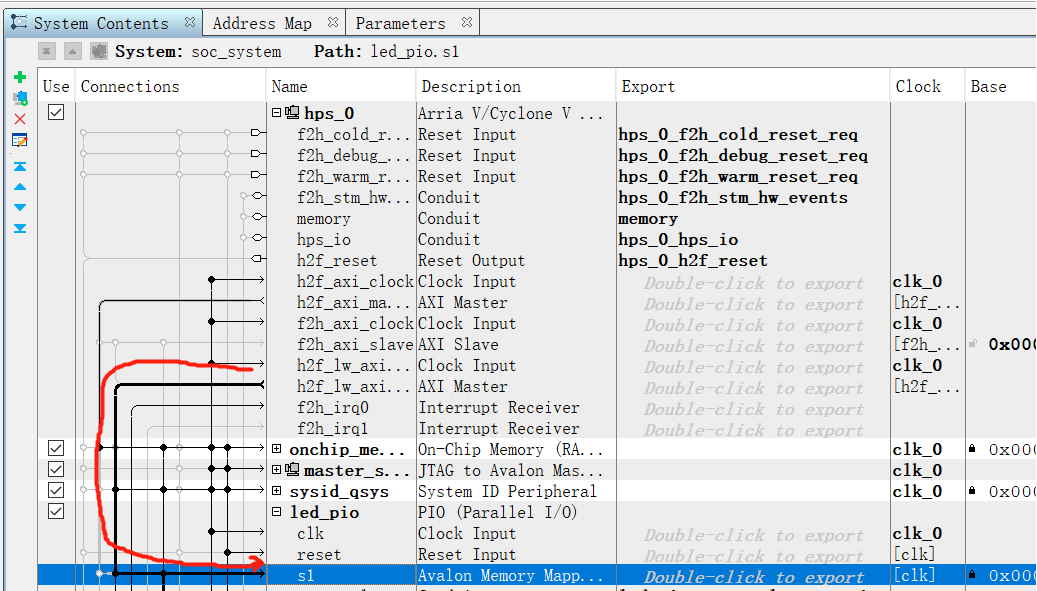

像以前的DE1-SOC 开发板 , PIO IP 等一些外设都是直接接 HPS IP 的 light weight AXI master 总线的:

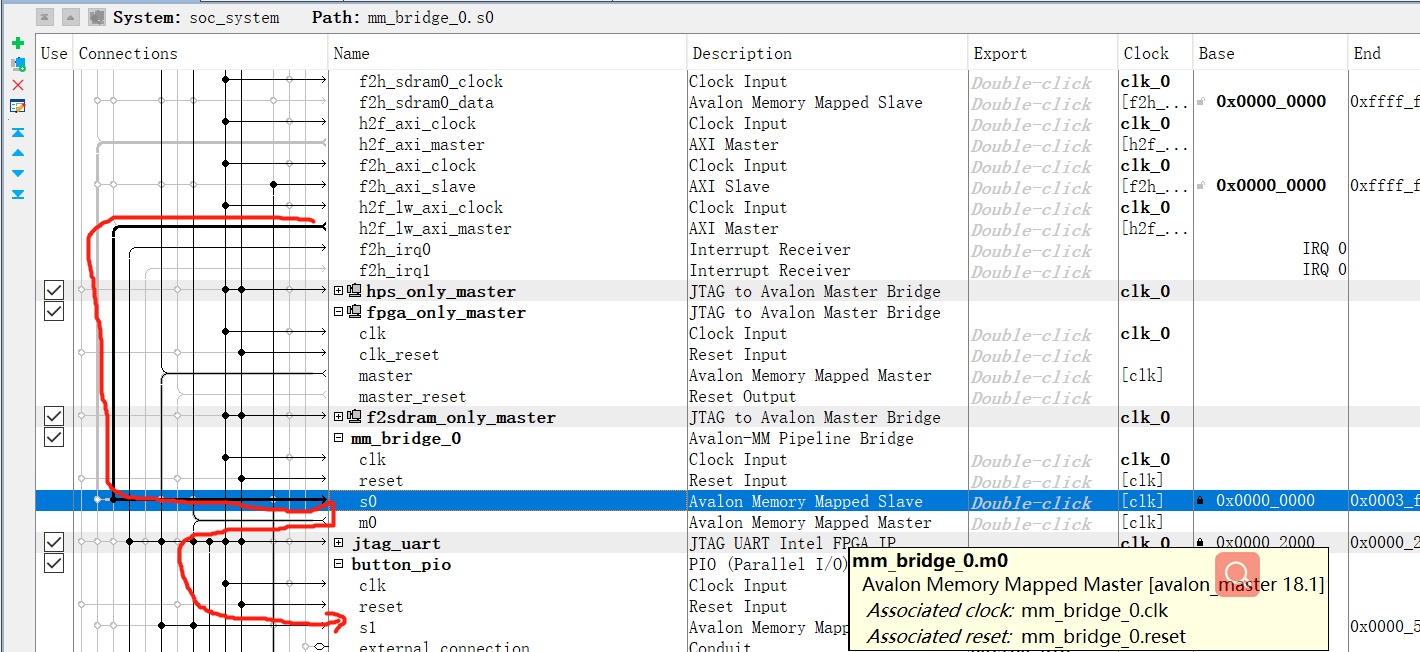

但是现在的DE10-Nano、 DE10-Standard 等开发板的官方发布的GHRD 工程里面,都会有个 Avalon-MM Pipeline Bridge IP 在 外设 IP 与 HPS IP 之间:

Avalon-MM Pipeline Bridge IP在这里起什么作用呢?其实Terasic这个GHRD是参考了Intel的 GHRD。

这个bridge会增加latency,一般工程师特别添加这个IP 的目的是为了改善时序。 例如简化连到同一个master的数量、类型, 用来当作pipeline。

很多不同类型的 外设, 也可以 分门别类的,用不止一个 bridge IP 来连接 LW 总线,就是 比如 PIO 的外设 归到一类, 然后 有其他的比如HDMI 的外设 我们又归到另一类,用另一个 bridge IP 。

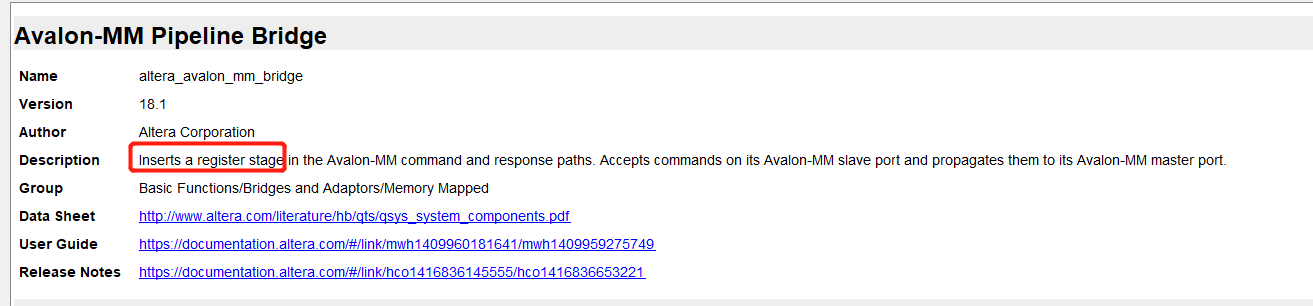

最后,大家可以来看看 bridge IP 的官方解释: Inserts a register stage in the Avalon-MM command and response paths. Accepts commands on its Avalon-MM slave port and propagates them to its Avalon-MM master port.