下面将创建一个核心板流水灯来演示工程文件的创建过程,假定您已经安装好了Xilinx ISE 12.4软件,ISE的安装请阅ISE的安装教程。

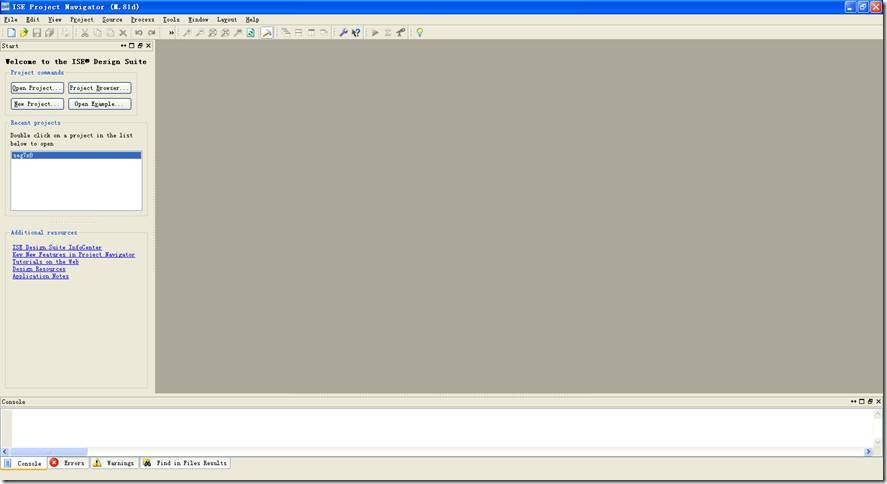

1、双击桌面Xilinx ISE图标,如下图所示,启动ISE软件。

2、打开软件界面如下图所示:

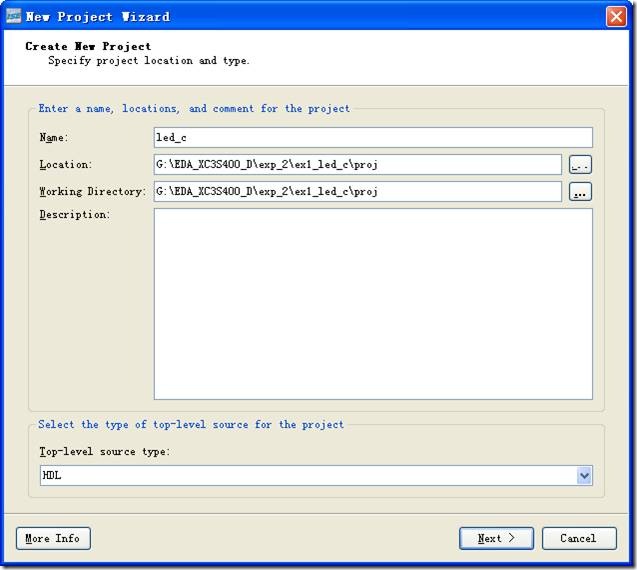

3、开始新建一个工程,点击【File—NewProject…】或【NewProject…】使用向导创建工程,如下图所示:

在该界面输入工程名、选择工程存放路径、选择顶层模块类型,其中顶层模块类型有硬件描述语言(HDL)、原理图(Schematic)、SynplifyPro默认生成的网表文件(EDIF)、Xilinx IP Core和XST生成的网表文件(NGC/NGO)这四种选项,这里我们使用Verilog模块作为顶层输入,所以选HDL。点击【Next】。

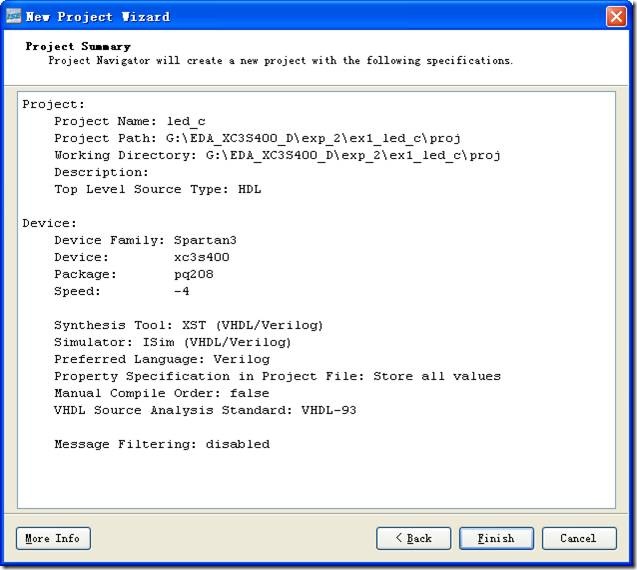

4、接下来是所选用芯片的一些属性设置,开发板用到的是Spartan3E系列的XC3S400-PQ208的芯片,请按如下图所示设置:

5、最后向导会将前面的选择以列表的方式显示出来,如果有选错或者设置不对的地方可以返回进行修改,修改好后点击【Finish】按钮结束向导

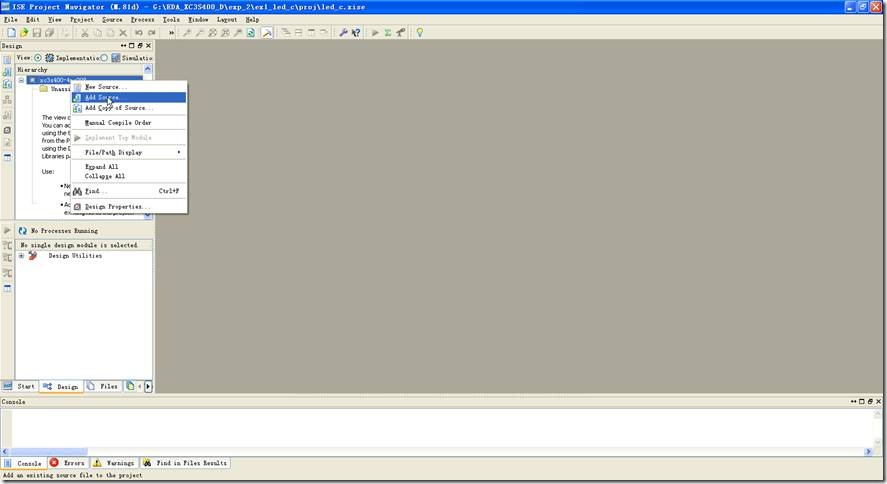

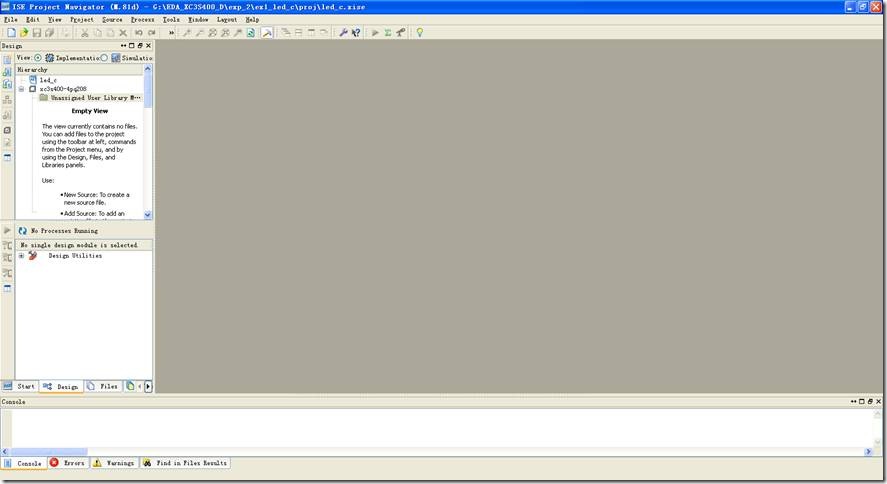

6、这里我们创建了一个空的工程,该工程尚不包含任何源文件和管脚约束,如下图所示,请保存该工程,下面我们将基于这个公的工程来进行学习和操作。

接下来,需要创建一个Verilog源码文件,可以用任何的文本编辑器来进行输入,输入完毕后保存为led_c.v,位置放在上面创建的工程路径下。

注意:也可以从配套光盘里面直接拷贝到工程路径下

7、 接下来,我们要把编好的led_c.v文件添加到前面创建的空的工程里面,回到从前创建的工程或者打开保存的led_c.xise工程,在工程主芯片的名称上右键选择【Add Source…】,如下图所示:

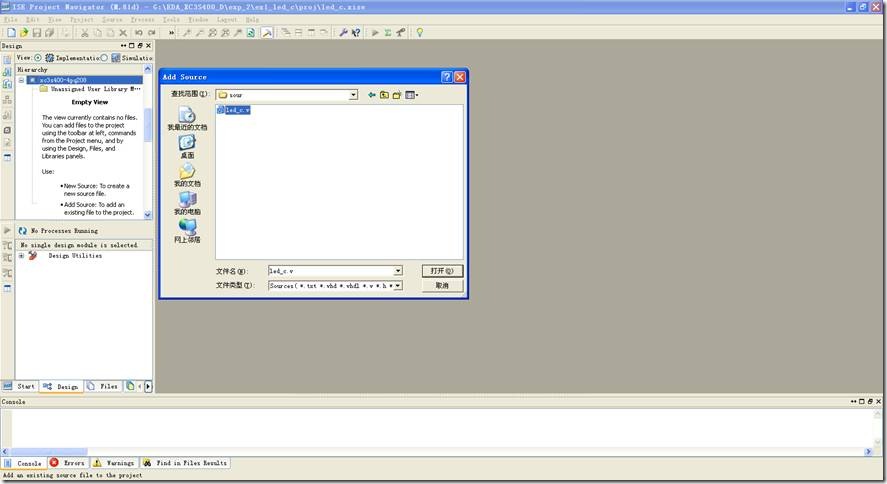

8、 选择前面编好的led_c.v文件,如下图所示:

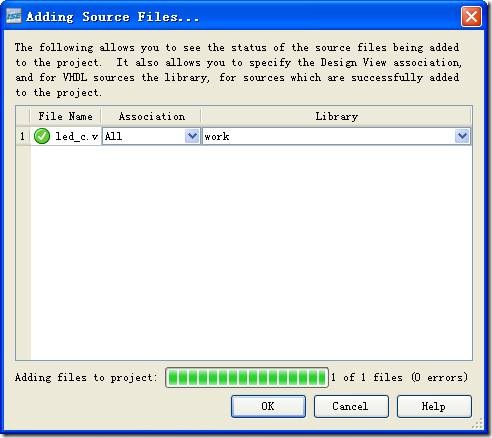

9、 导入文件出现如下图所示对话框,点击【OK】添加文件。

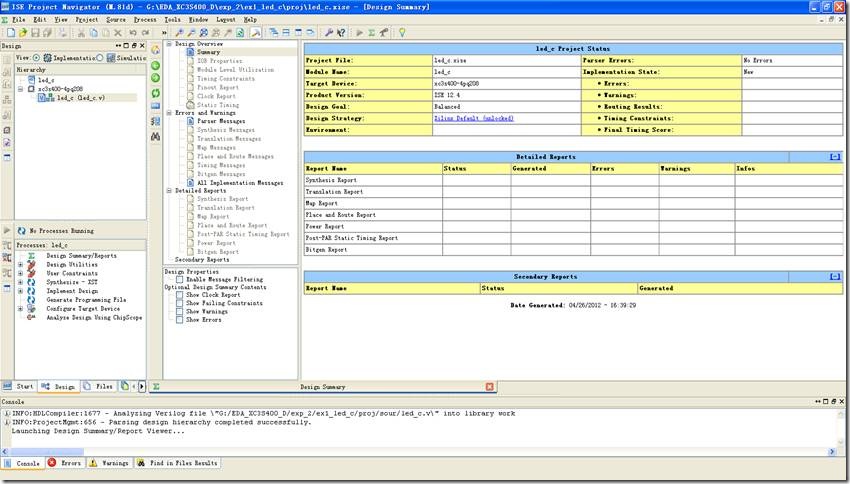

10、添加led_c.v文件后,ISE如下图所示:

11、创建管脚约束文件。

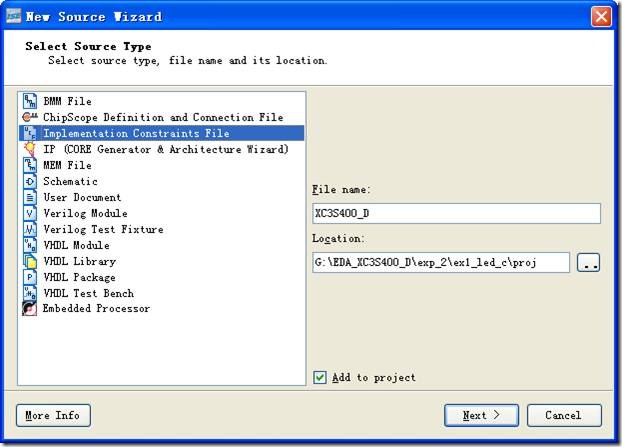

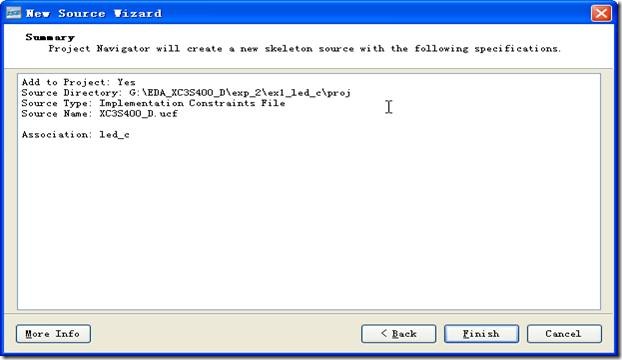

在源代码窗口中单击右键,在弹出的菜单中选择New Source,然后选择![]() ,输入文件名,点击【Next】。在弹出的窗口确认信息无误后点击【Finish】。

,输入文件名,点击【Next】。在弹出的窗口确认信息无误后点击【Finish】。

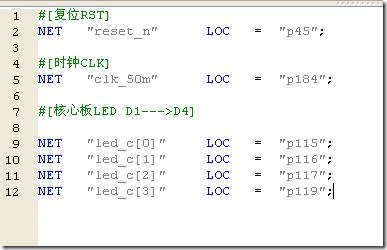

软件会自动打开约束文件编辑窗口,输入以下代码,点击保存。

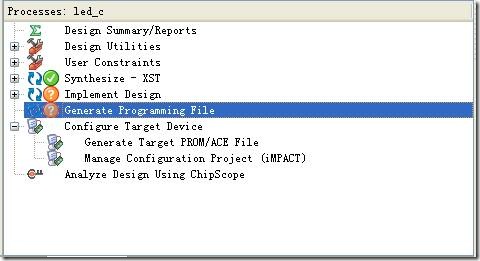

12、回到ISE 主窗口, 展开ISE 窗口左边中部的 ![]() 可以看到

可以看到![]() ,如下图所示:

,如下图所示:

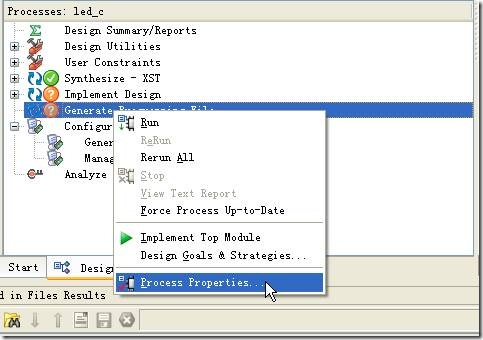

13、在![]() 上点右键选择属性Properties…设置,如下图所示:

上点右键选择属性Properties…设置,如下图所示:

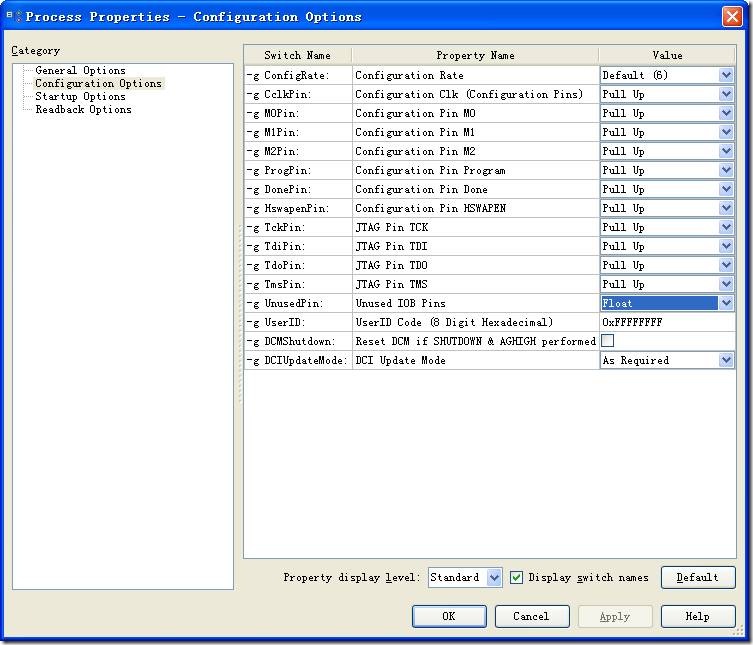

14、打开属性设置窗口,大部分按默认设置即可,找到左边的第二项![]() ,将其右侧对应的设置

,将其右侧对应的设置![]() 由默认的Pull down 改为Float,如下图所示,设置好此项后点击 OK 按钮确认退出:

由默认的Pull down 改为Float,如下图所示,设置好此项后点击 OK 按钮确认退出:

注意:此项设置的功能是将芯片的没有用到的管脚置为浮动状态,也就是高阻态,默认是下拉到低电平的,需要特别注意。

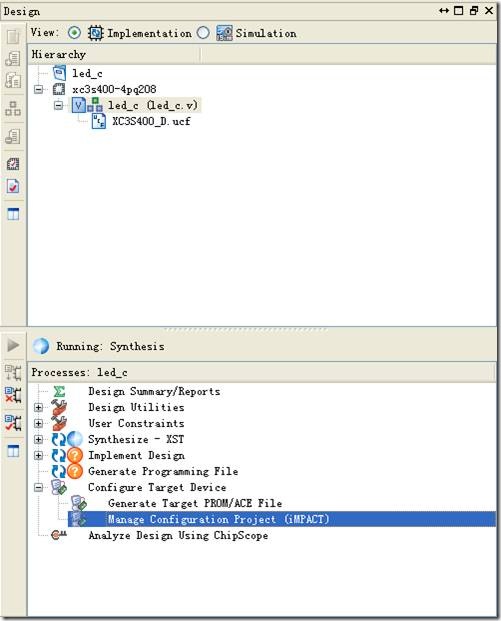

15、回到ISE 左侧中部的![]() ,展开

,展开![]() 可以看到其子项

可以看到其子项![]() ,该项功能为将编译好的文件下载到CPLD/FPGA 芯片内部,双击该项,ISE 将对工程进行编译综合,如下图所示:

,该项功能为将编译好的文件下载到CPLD/FPGA 芯片内部,双击该项,ISE 将对工程进行编译综合,如下图所示:

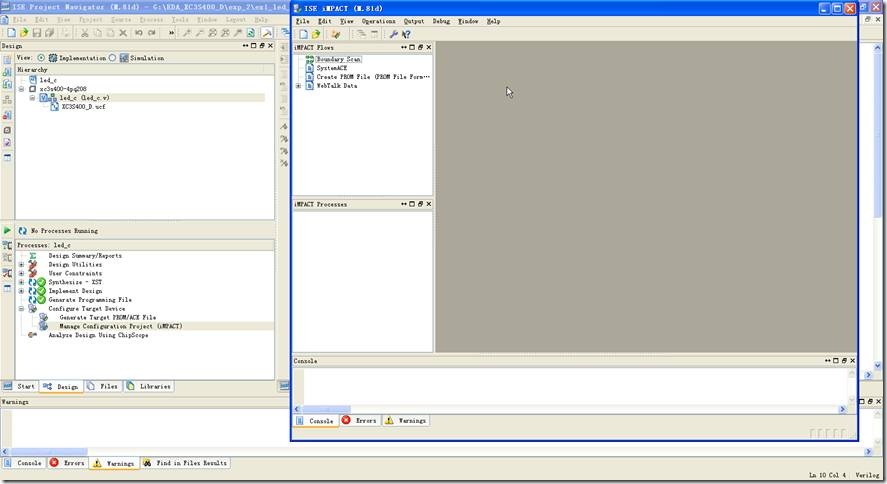

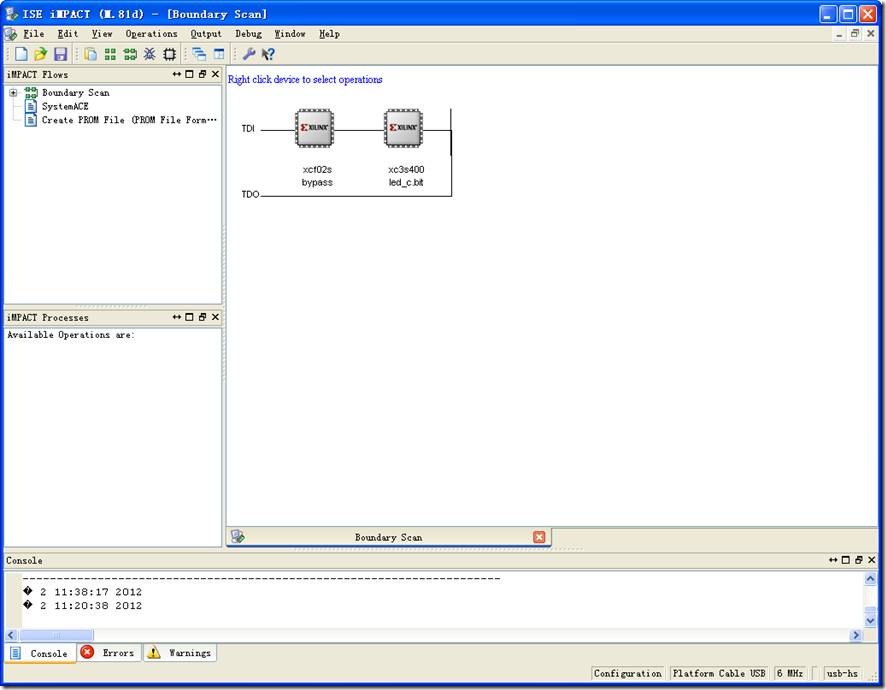

16、编译完成后弹出ISE IMPACT 下载窗口,如下图所示。

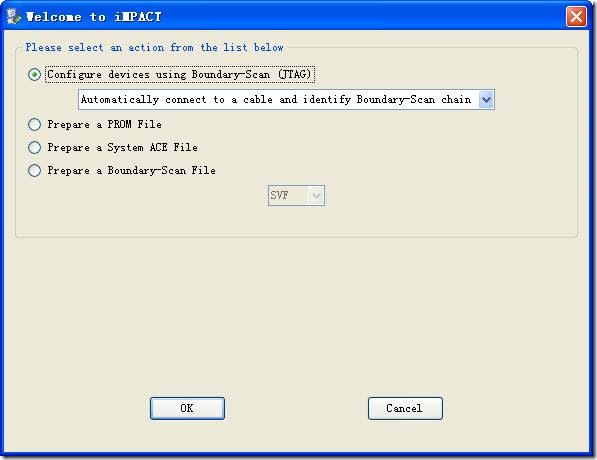

17、在下载窗口点击![]() 或【Eidt---àLaunch Wizard】弹出如下所示的图,点击【OK】进行自动JTAG扫描。

或【Eidt---àLaunch Wizard】弹出如下所示的图,点击【OK】进行自动JTAG扫描。

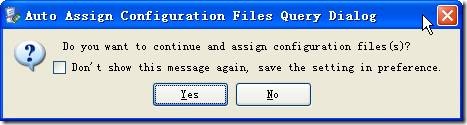

18、如下窗口,是否继续分配配置文件,点击【YES】。

19、弹出分配Flash配置文件的窗口,如图所示。因为这个配置文件需要后面生成,所以关闭这个窗口。

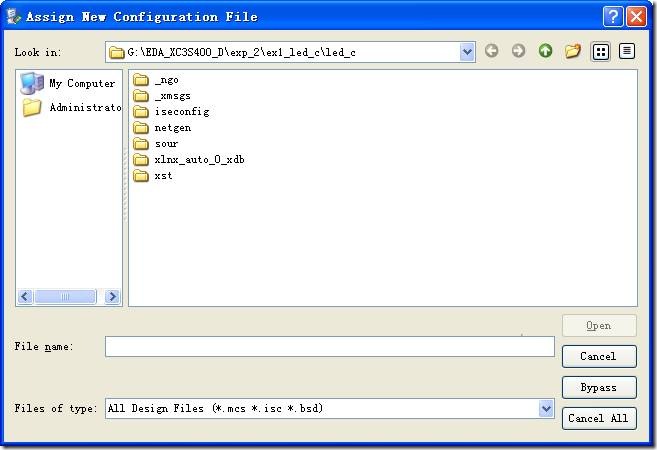

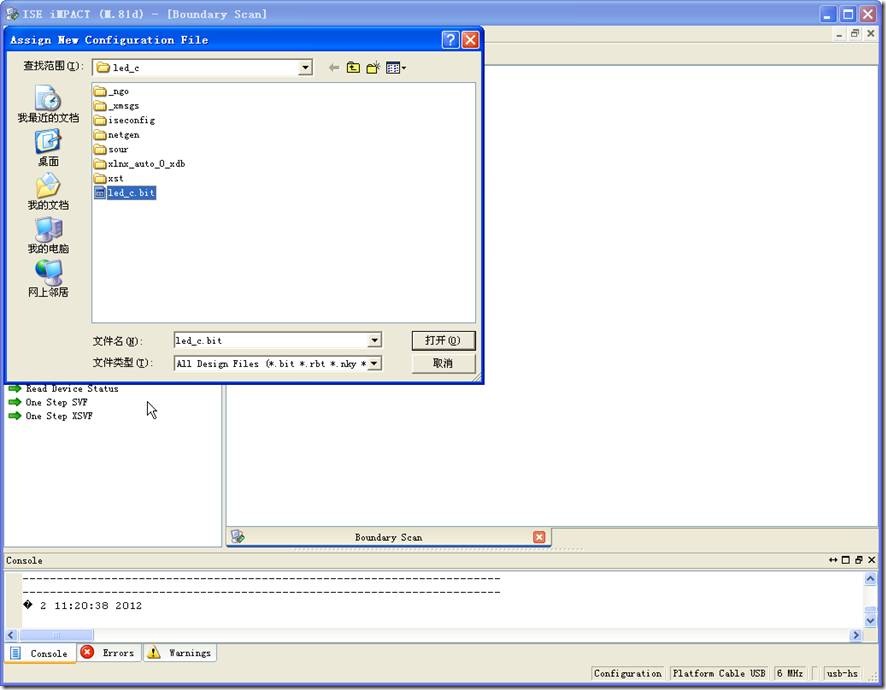

20、接下来会弹出配置FPGA 芯片的窗口,可以看到工程目录下已经自动生成了名为led_c.bit 的配置文件,也

就是我们常说的烧录文件,这里添加这个led_c.bit 文件,如下图所示:

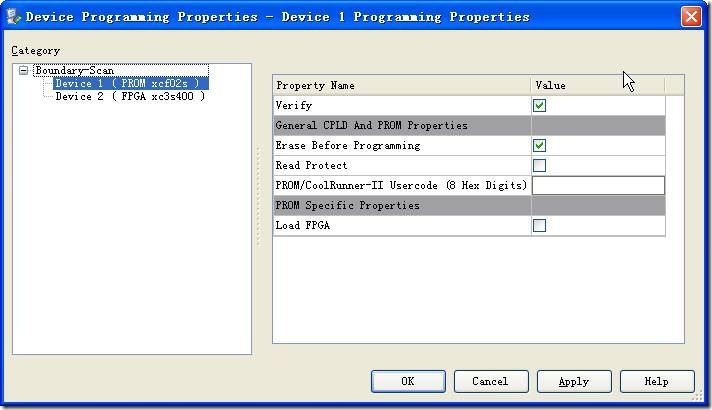

21 、添加led_c.bit 后会弹出设置器件编程特性的窗口,这里点击OK 按钮确认即可,如下图所示:

22、添加好FPGA 配置文件led_c.bit 后如下图所示:

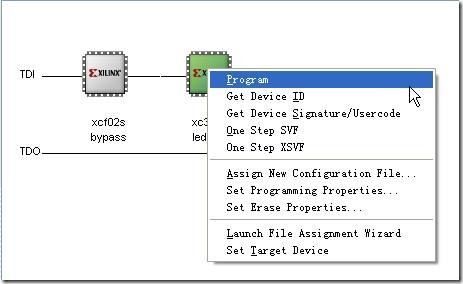

23、在FPGA 芯片XC3S100E 上点右键,弹出如下图所示的几个选项,这里我们要对FPGA 芯片进行编程,选择第一项 Program… 如下图所示:

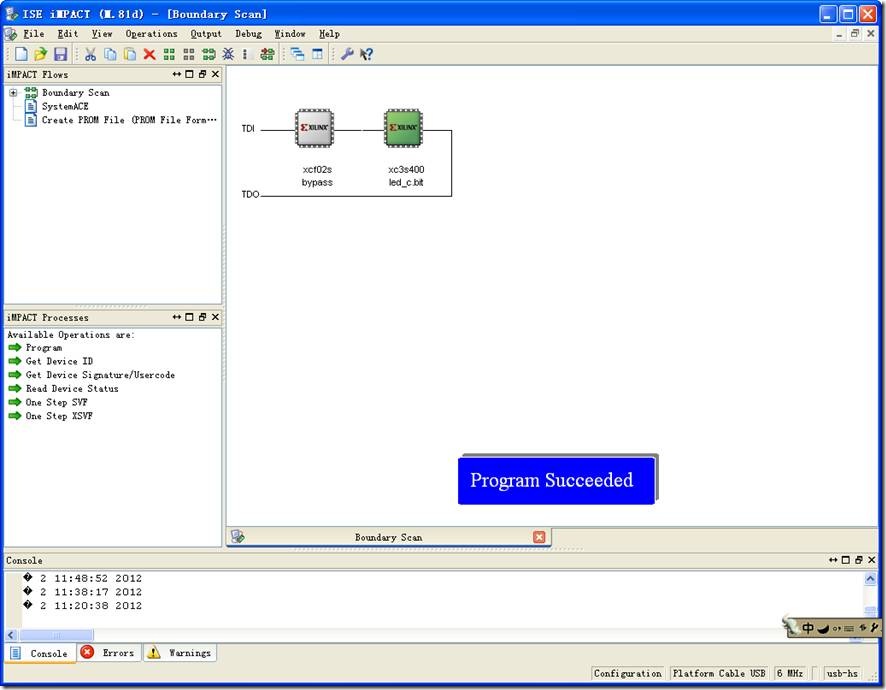

24、如果下载过程没有错误,在下载结束后会提示蓝色的编程成功信息,恭喜你,到这一步,你的第一个程序就已经成功下载到板子上了,这时可以看到板子上的流水灯已经在跑起来了!

25、这时,如果你将开发板断电再重新上电,可以看到板子又恢复到了之前的状态,也就是说你刚才下载到FPGA的程序在重新上电后就没有了,别担心,这个是FPGA 芯片的正常现象,由于FPGA 在刚上电启动时会去读取配置芯片的数据,将配置芯片的数据读入FPGA 后在再运行,所以下面我们需要FGPA 的配置芯片XCF02S 进行编程。

接下来我们要将 ledwater.bit 转换为 mcs 格式的配置文件写入到 xcf02s 里面。

回到ISE 工程的Boundry Scan 窗口,可以看到左侧上部有几个编程选项,双击其中的![]() 项,如下图所示:

项,如下图所示:

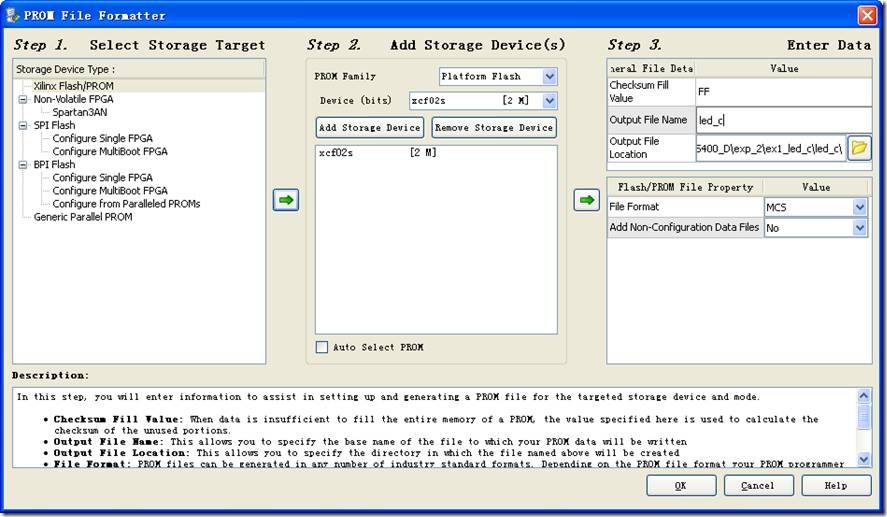

26、点击![]() ,设置

,设置![]() 点击

点击![]() ,再点击从第二步到第三步的

,再点击从第二步到第三步的![]() ,设置烧写文件路径为工程路径,设置文件名为工程名。设置如下图所示,完成设计点击【OK】

,设置烧写文件路径为工程路径,设置文件名为工程名。设置如下图所示,完成设计点击【OK】

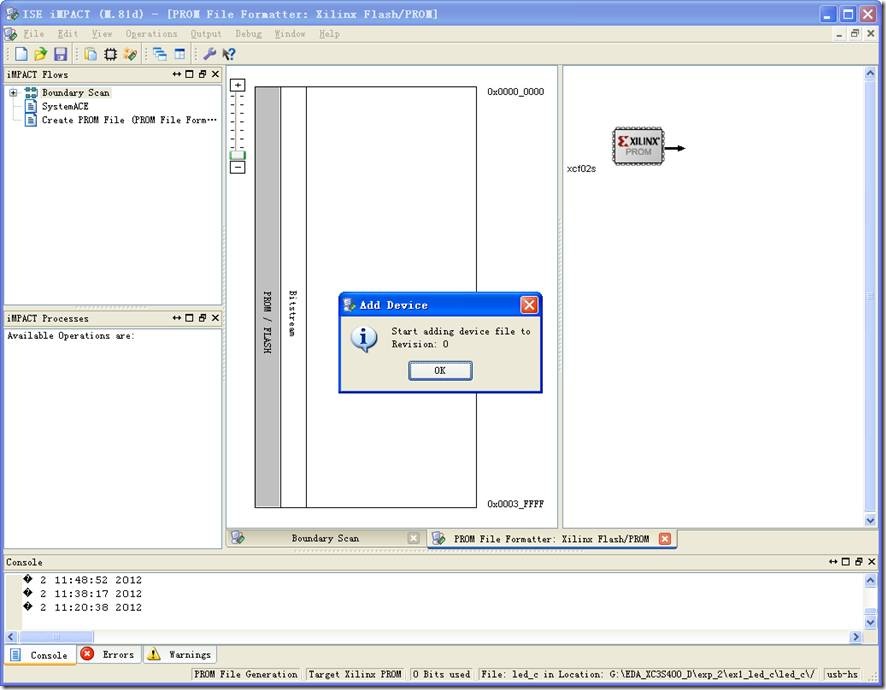

27、弹出添加器件的窗口,点击【OK】。

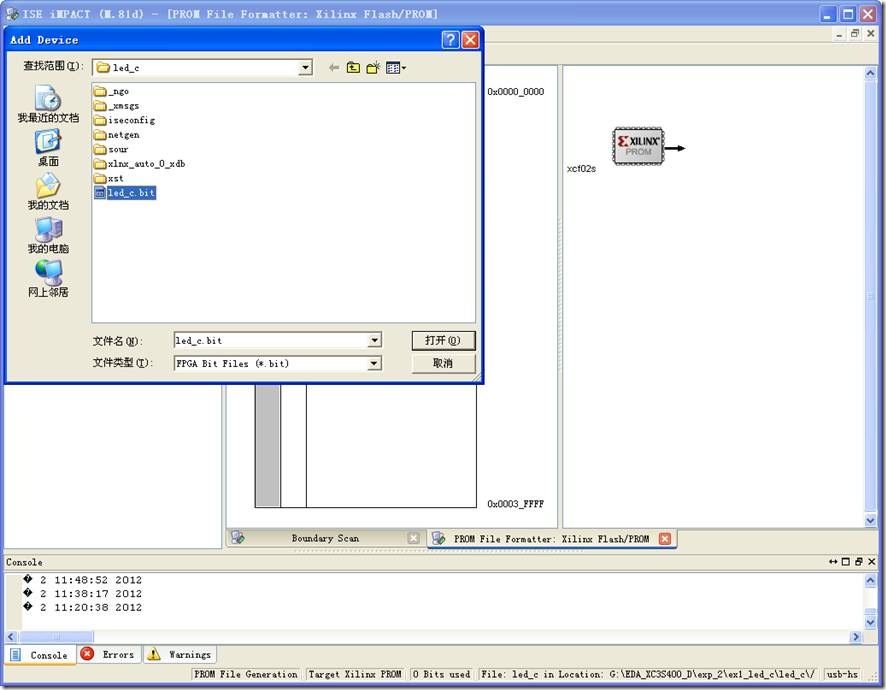

28、接着是添加需要转化的.bit 文件,选择led_c.bit,如下图:

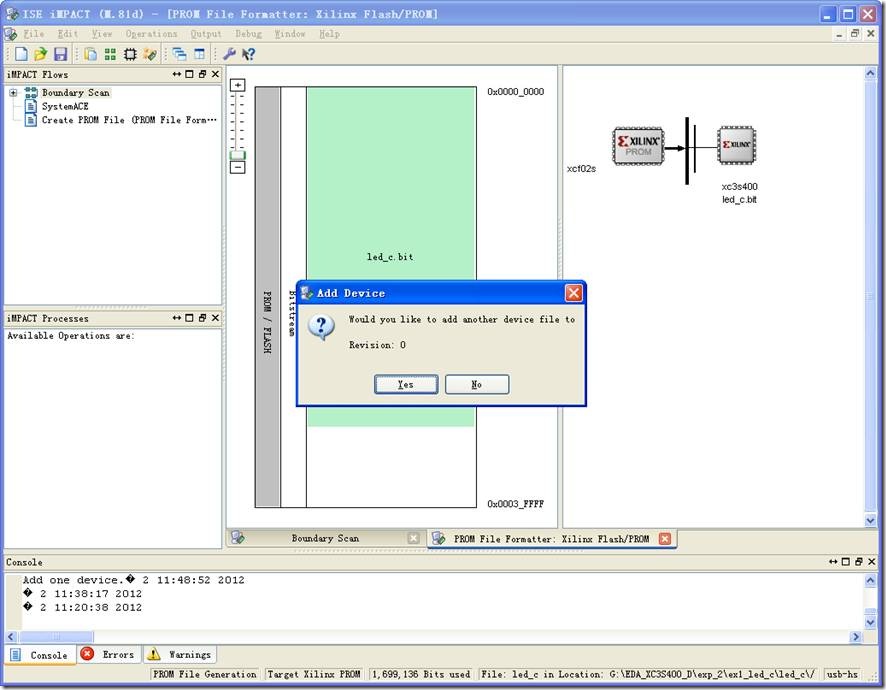

29、询问是否添加另外一个文件,选择 No ,如下图:

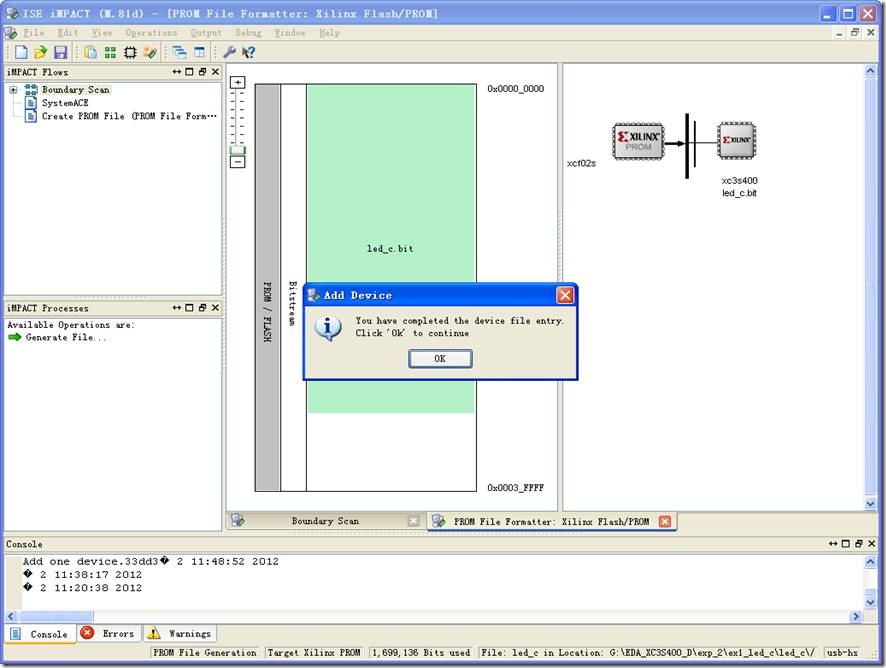

30、接下来的信息框提示已经结束了文件的添加,点击 OK 确认即可,如下图:

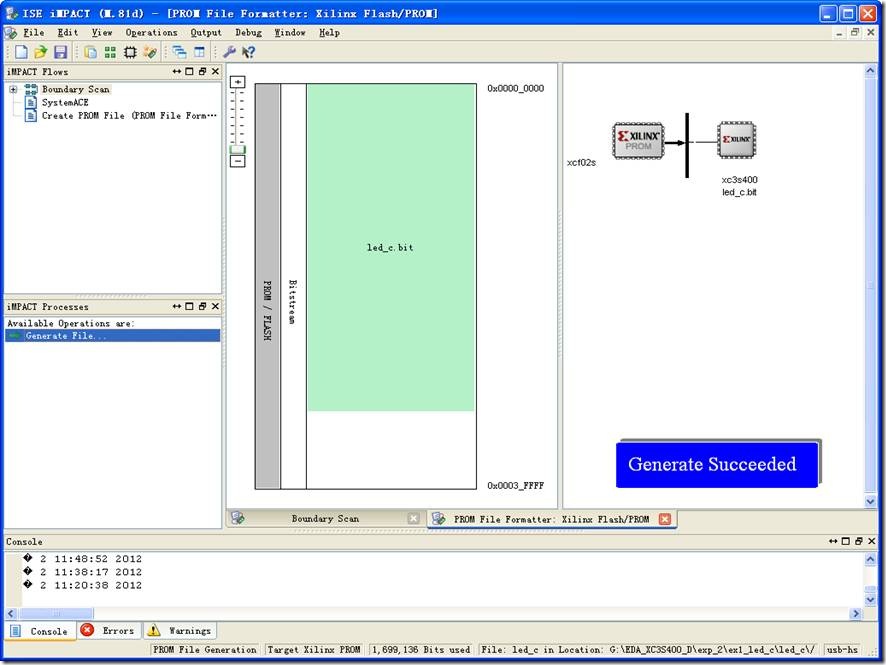

31、将ISE 左侧中部可以看到有项![]() ,双击该项即可生产PROM 配置文件,如下图所示:

,双击该项即可生产PROM 配置文件,如下图所示:

32、生成PROM 配置文件成功。

33、回到Boundary Scan 窗口,在XCF02S 上双击,找到刚生成的led_c.mcs 文件,如下图:

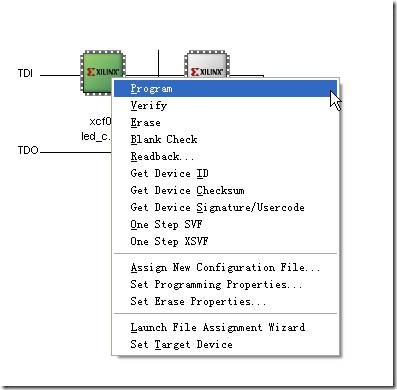

34、类似FPGA 主芯片下载,在XCF02S 上点右键选Program… 如下图所示:

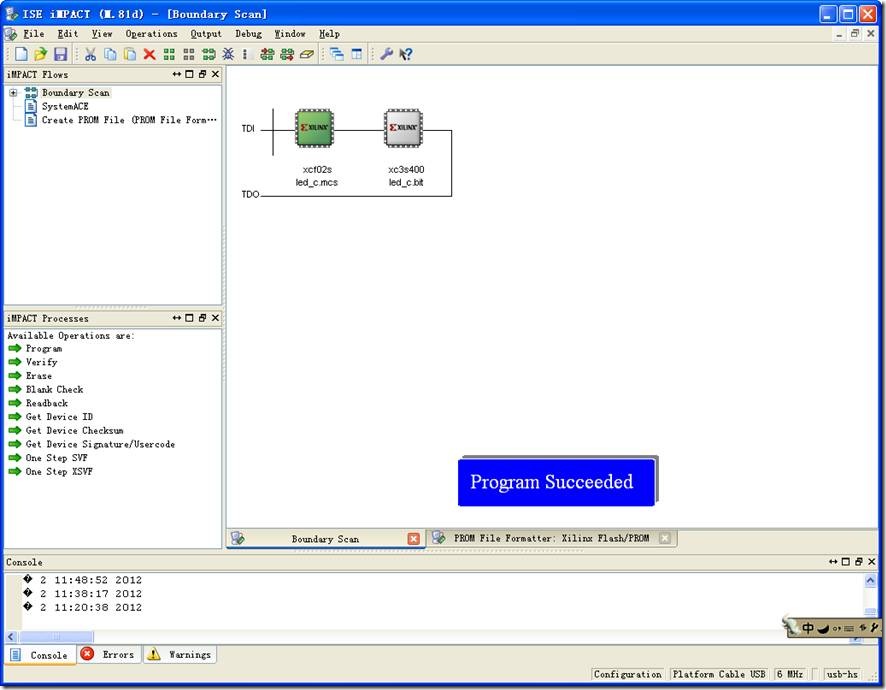

35、开始编程,PROM 的编程速度会慢些,请耐心等待几十秒钟,下载结束后可以重新上电试试,可以看到,流水灯已经按预期跑了起来。

编程完成: