http://www.eefocus.com/yq000cn/blog/11-03/205752_69f56.html

Author:KiKi

Email : yq000cn@gmail.com

Date: 2011.3.7

Blog主题

这篇blog想弄清楚FPGA上电配置后程序引导和启动的整个流程是怎么样的,不是谈论如何编写bootloader。

主题的引出

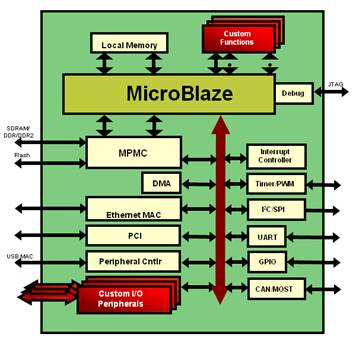

本 人创建了一个基于MicroBlaze的嵌入式系统(类似于如图1所示,当然没有图1那么复杂)。片上BRAM仅仅是64KB,而本人生成的程序镜像有 2MB多,所以这样的话,程序镜像不能跟用于配置FPGA的bit流文件融合直接配置到片上的BRAM中。解决的方案是用外部非易失性存储介质来存储程序 镜像和bit流文件,如PROM,或者Flash。Xilinx提供了一种SystemACE 配置解决方案,那整个工作流程又是如何的呢?

图1. 基于MicroBlaze的SOPC架构

问题的解决

在参考文献1中,有这样一句话,SystemACE解决方案是通过JTAG将程序下载到debug(对 于MicroBlaze也就是,MicroBlaze debug module)。看到这句话,一时没反应过来。要知道SystemACE解决方案是将用于配置FPGA的bitsteams文件和程序可执行二进制文件融 合生成一个*.ace。在看了genace.tcl这个用于生成ace文件的脚本后,终于明白了,刚才提到的那句话。

首先说明一下SystemACE文件是如何生成的?

1. 通过iMPACT工具将bitstream文件转为SVF文件

该SVF文件包含了配置FPGA的JTAG指令序列2.通过XMD将elf可执行文件转为SVF文件

该SVF文件包含了通过XMD将ELF文件下载带内存或许片上BRAM的JTAG指令序列3.通过XMD将数据/二进制代码转为SVF文件

4.连结第一步和第二步中生成的SVF文件

5.通过iMPACT工具利用结合的SVF文件生成systemACE文件

整 个生成过程一目了然了,SystemACE解决替代了这样一个在线调试的流程:通过iMPACT将含有bootloop的程序的bitstream文件通 过JTAG下载到FPGA中,这个时候FPGA在空转,等待运行程序的加载。接下来通过XMD先跟debug和CPU通信,然后将程序下载到指定的内存或 者BRAM中,然后运行CPU。

总结,SystemACE配置方案,需要硬件的支持,即SystemACE控制器和CF卡,当然在嵌 入式系统中还需要添加Debug模块。优点显而易见,不用编写bootload类似的引导程序,也不用关心程序镜像的大小,因为CF卡的容量很大,满足了 绝大多数的嵌入式应用的要求。

问题的延伸

还有一种情况就是通过PROM/FLASH存储程序镜像和bitstream文件配置FPGA,并引导程序启动。具体的流程如下:

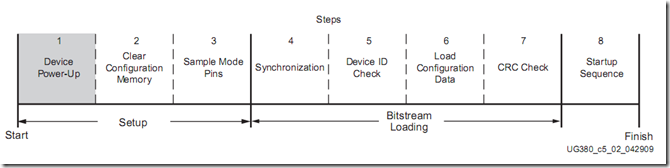

图2 Spartan6的配置和启动的过程

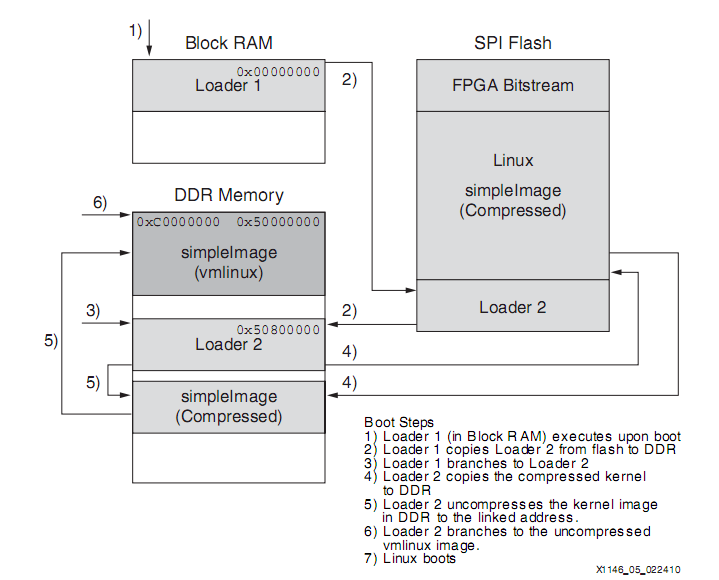

这里不关心如何去配置FPGA,而关心的是系统是如何引导的。以在FPGA运行Linux为例作说明。如图3所示,具体步骤如下:

第一步,CPU从0x0地址(BRAM)执行Loader1 (注意,Loader1放在BRAM中,在配置FPGA过程中就加在进去)

第二步,Loader1读取SPI Flash中Loader2程序,然后复制到内存中。

第三步,Loader1程序跳至在内存中执行Loader2

第四步,Loader2读取SPI Flash中压缩的内核镜像

第五步,Loader2程序解压缩内核到另一块内存空间

第六步,Loader2程序跳至解压缩的内核镜像

第七步,Linux内核启动

图3 Linux引导流程

由上面的流程可知,通过PROM或者Flash进行配置的话,需要Bootload作支持,即需要完成将程序镜像从Flash或者PROM中读取至内存上。当然嵌入式系统中需要添加PROM或者Flash控制器。