仿真中的database主要存放关于signal transition以及时间点的信息。

IUS中的的database包括:

1) SHM, Verilog/VHDL/mixed-language的database

2) VCD/EVCD, Verilog/VHDL/mixed-language的database

Simulator的启动方式有两种:

1)Multi-step,

ncvhdl [options] vhdl_source_files

ncvlog [options] verilog_source_files

ncelab [options] top_level_design_unit

ncsim [options] snapshot_name

2)single-step,

irun + all input files + cmd file

支持各类文件,包括verilog/vhdl/verilog AMS/SV,而后自动调用elaborate和simulator进行仿真,加入-gui可以打开simvision仿真。

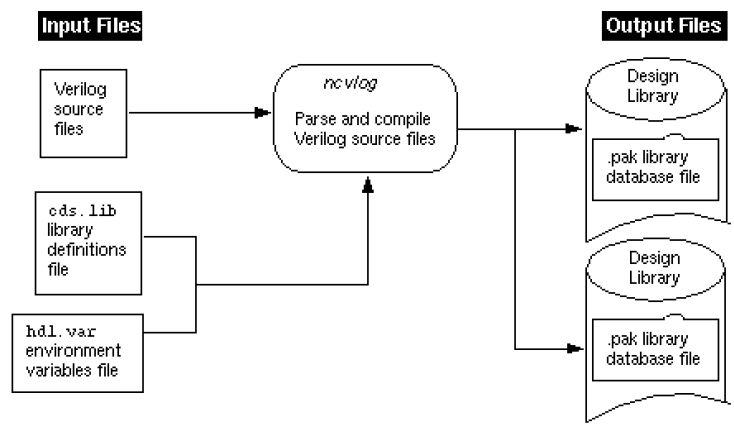

针对verilog文件的编译,仿真流程:

1)verilog文件经过,ncvlog编译之后,生成.pak文件,

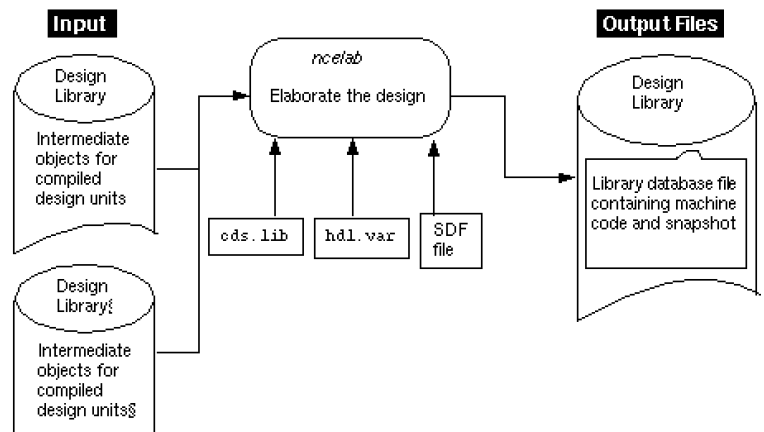

2)ncelab构建design的hierarchy,establish connection,compute initial value

生成machine code和snapshot, snapshot的一般命名方式是worklib.proj_top_th:dut_a

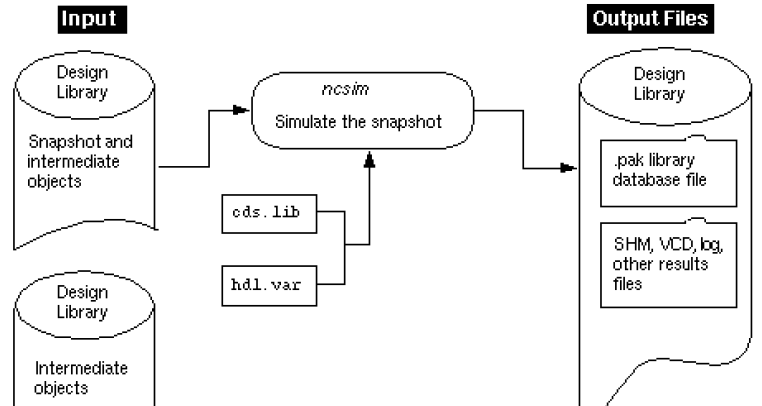

3)ncsim输入snapshot,sim_tcl,产生一个SHM/VCD/EVCD的database

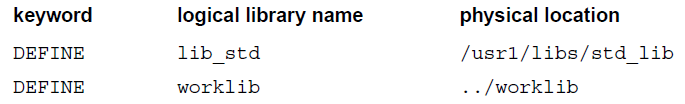

cds.lib文件,用来映射逻辑库和物理库的位置。

hdl.var是一个可配置的文件,主要来配置一些design environment