STM(System Trace macrocell)

STM是coresight system中的一个trace source,可以提供high-bandwidth的trace data。

STM优于Instrumentation Trace Macrocell(ITM):

1) dedicated AXI slave for receiving instrumentation----software writes to its stimulus ports;

2) multiple processor can share and directly access the STM without being aware of each other;

通过分配不同的pages在STM stimulus space中。

3) optionally stall the axi when its fifo becomes full;

4) Timestamping can be requested for each write independently;

5) Timestamps are automatically correlated with other timestamping trace sources in coresight system;

6) Provides a hardware event interface, STM traces when rising edges occur on signals;

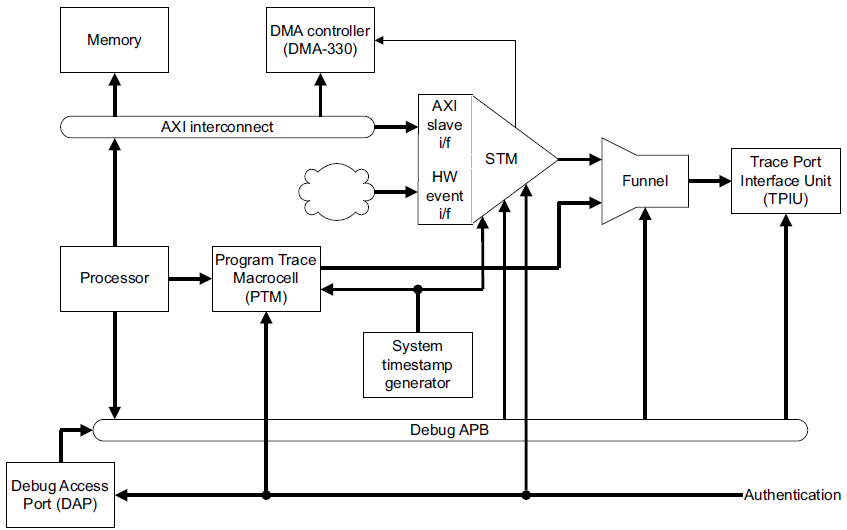

STM模块的集成:

STM的AXI slave连接到system interconnect来关注到所有的system master,如processors和DMA controller;

STM的debug APB连接到off-chip或on-chip的debug agent(DAP);

STM的trace stream通过ATB bus输出到ETB或TPIU或pad;

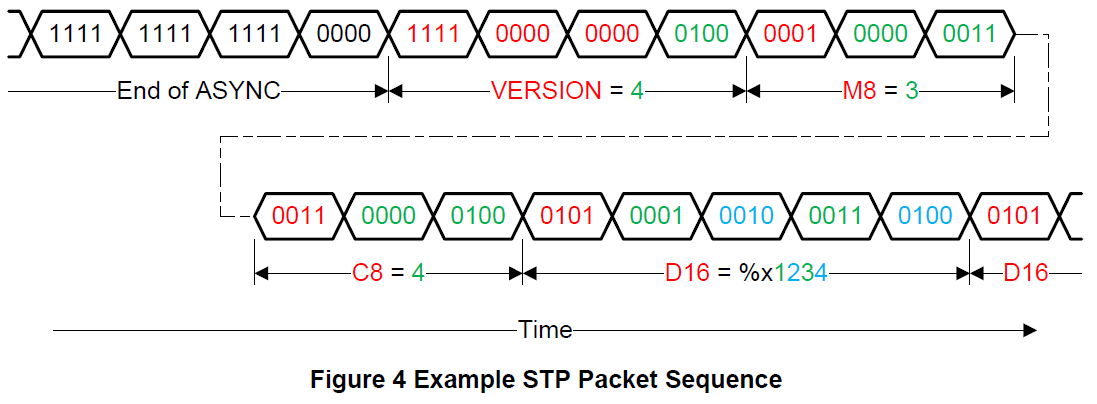

STM trace到的data会按MIPI System Trace Protocol(STPv2)进行package

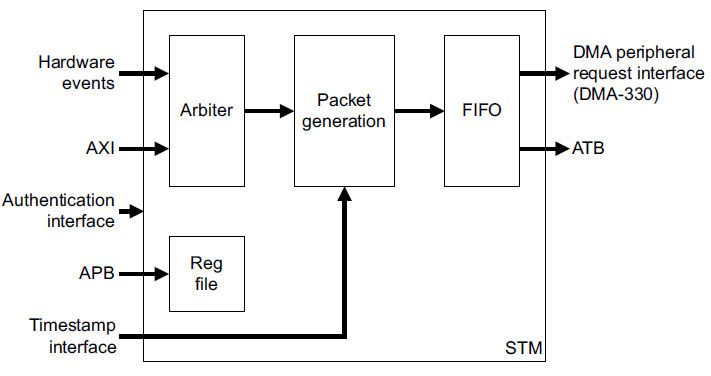

STM内部的block diagram:

STM内的interface:

1) AXI slave,连接STM到system bus;

2) Hardware event observation interface,共32个signals连接到system various signals(Interrupt lines,DMA request lines,CTI trigger outputs);

3) DMA peripheral request interface,连接到一个DMA Controller;

4) Debug APB slave interface;

5) ATB master interface;

6) Timestamp port interfa

7) Cross-trigger interface,连接到coresight system CTI接口,indicate trigger events;

在Real_time trace中,source会比较多,包括trace components monitoring processor instruction and data flow,

instrumentation in the software running on a processor,trace components monitoring activities outside the processor。

STPv2定义了所有的message types和message sequences。

ce;