https://www.zhihu.com/question/263728785/answer/289175276

链接:https://www.zhihu.com/question/263728785/answer/289175276

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

第二次补图

图1

图1 图2

图2

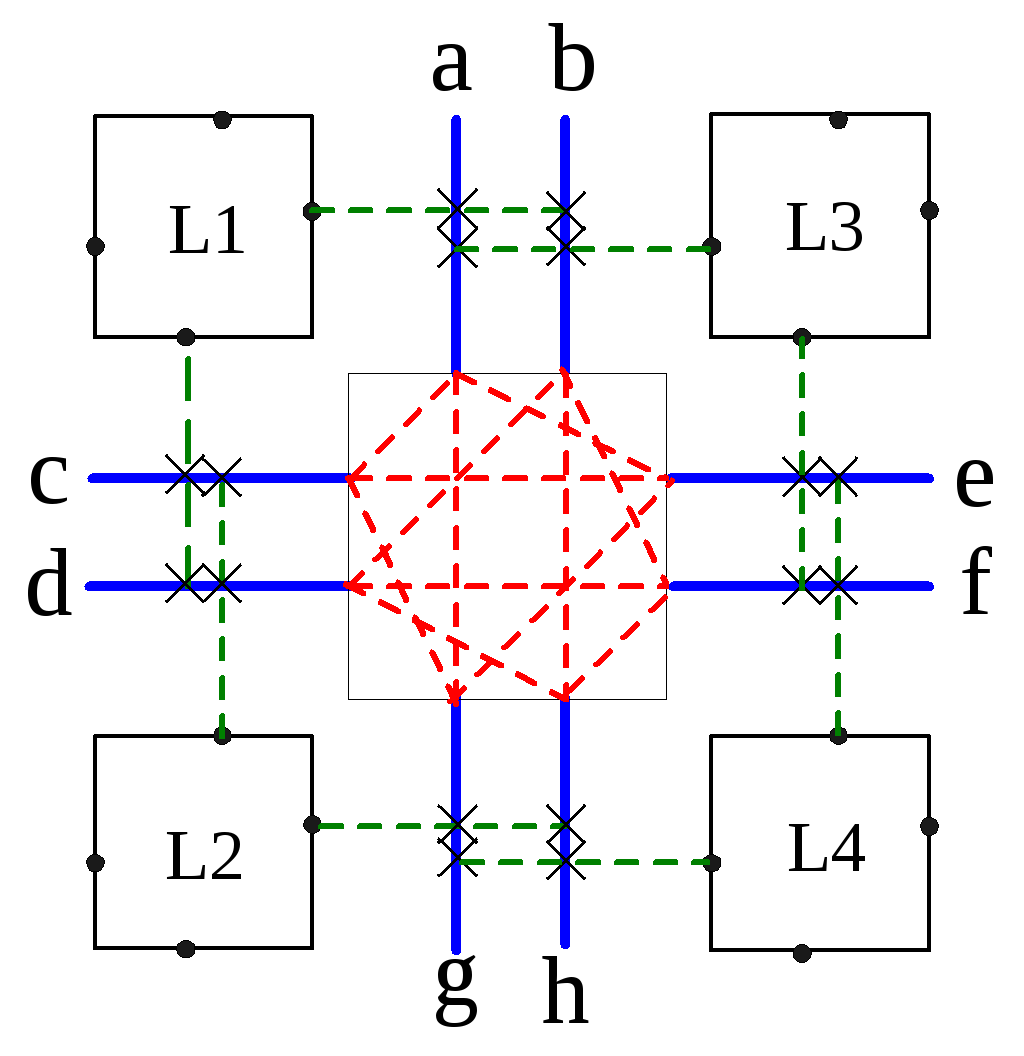

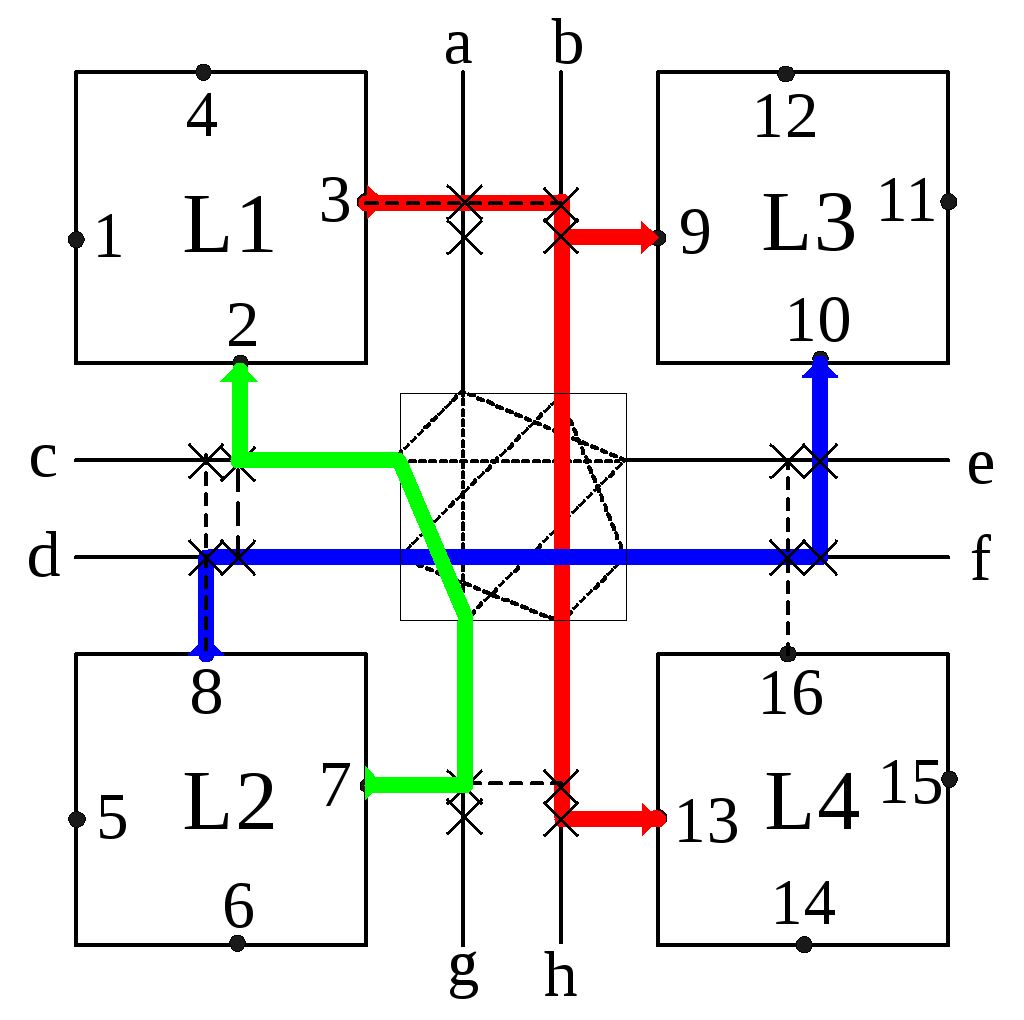

评论回复里的图被吃了,加到这里

一种布线结构

一种布线结构 布线结果

布线结果

################### 原答案 ##################

- FPGA芯片内部工作原理

FPGA(Field-Programmable Gate Array),即现场可编程门阵列。从某种角度上讲我不是很赞同“可编程”这种说法,而更倾向于“可描述”。 它可以通过硬件描述语言(Verilog或VHDL)描述一个电路设计,通过配套的EDA工具综合与布局,并烧录至 FPGA来实现设计需要。

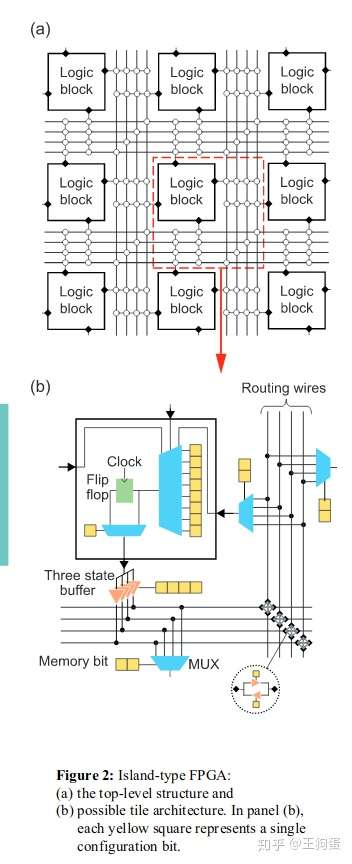

目前所有的FPGA或eFPGA都包含大量的可编程逻辑单元和可编程布线单元。逻辑单元可以实现一小部分数字逻辑,而布线则连接这些逻辑单元来组成更大的数字电路。

可编程逻辑单元和可编程布线单元

可编程逻辑单元和可编程布线单元

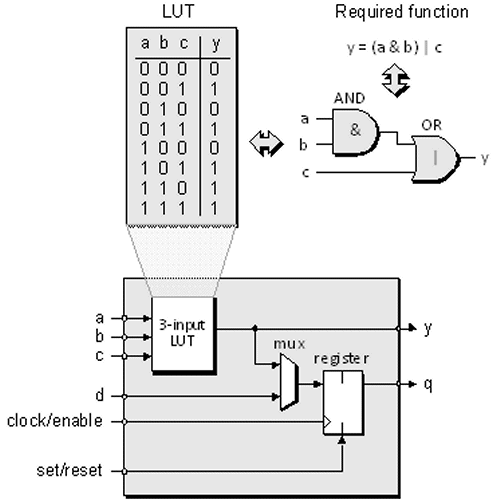

可编程逻辑单元:

我们知道数字电路可以细分为组合逻辑和时序逻辑。 FPGA中实现组合逻辑的部分就是查找表(LUT),时许逻辑则依靠寄存器。若干个LUT和寄存器相互连接则构成了一个逻辑簇。不同的FPGA公司所定义的逻辑簇的结构也是不同的。 逻辑簇结构有2大好处,第一逻辑簇中的互联速度要快,可以提高FPGA速度; 第二, 逻辑簇的应用可以简化排版布线的复杂度,缩短综合时间。

一个逻辑簇

一个逻辑簇

可编程布线单元:

与定制电路不同, FPGA的布线资源都是预制好的, 因此预制的布线资源能够连接绝大多数的逻辑单元(簇)。 对于用户设计好的项目,通过控制一系列的开关来满足特定单元间的互联。 这也就使得布线资源占据了FPGA的绝大部分面积, 而且复杂的布线网络中控制开关过多的话会大大降低FPGA的运行频率。如果减少布线资源, 则会加大EDA软件算法的难度,而且会导致电路布局布线失败。

因此如何设计逻辑簇和与之配合的布线资源,使其达到速度和面积的均衡,而且还要考虑到EDA软件算法的难度,执行时间以及内存占用, 这是每个FPGA厂商的核心中的核心。

2. 有哪些专有设计

上面简述的逻辑资源和布线资源属于FPGA硬件部分的范畴,也就是硬件的专有设计。

与之配套的还有其EDA软件的专有设计。以前和一个搞FPGA的博士聊天, 他表示有2种通用芯片是需要有大量技术积累的; 一个是CPU,另一个是FPGA。 CPU的难点是其硬件结构,软件指令集则不是厂家的主要难点。 而FPGA的硬件结构原理并不是主要技术壁垒, 但是其EDA软件的核心算法则是每个公司的长期积累的成果。

他的观点我还是比较赞同的。 试想, 如果一个小规模FPGA硬件结构和其配套EDA实现了的话,为什么不能把其等比例扩大使其成为一个超大规模的FPGA呢? 而现实是目前国产FPGA规模基本上都在50K LUTs左右。 (有个别宣传有200K LUTs。目前好像还没有量产)。

事实上, FPGA软件综合的每一个流程都是一个NP问题。 从映射, 装箱, 排版 到布线。 而且还要加入物理结构的约束条件,以及时序驱动优化的约束。所有这些会大大增加算法的难度和程序的执行时间, 而且对于超过大规模的电路来说还要考虑软件的内存占用。

因此在软件工具链上的开发经验的积累对于FPGA厂商来说是极为重要和专有的。就我了解的一些公司,可以对硬件结构申请专利,却对核心算法严格保密甚至不去申请专利以防竞争对手通过专利简报推测其内容。

以上是我的回答, 有错误的地方欢迎批评指出, 有不严谨的地方欢迎探讨。如果你还有问题的话也欢迎继续讨论