同步复位与异步复位的优缺点

同步复位的优点:

- 一般能够确保电路是百分之百同步的。

- 确保复位只发生在有效时钟沿,可以作为过滤掉毛刺的手段。

同步复位的缺点:

- 复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位。同时还要考虑如:时钟偏移、组合逻辑路径延时、复位延时等因素。

- 由于大多数的厂商目标库内的触发器都只有异步复位端口,采用同步复位的话,就会耗费较多的逻辑资源。

异步复位优点:

- 异步复位信号识别方便,而且可以很方便的使用全局复位。

- 由于大多数的厂商目标库内的触发器都有异步复位端口,可以节约逻辑资源。

异步复位缺点:

- 复位信号容易受到毛刺的影响。

- 复位结束时刻恰在亚稳态窗口内时,无法决定现在的复位状态是1还是0,会导致亚稳态。

-

异步复位同步释放

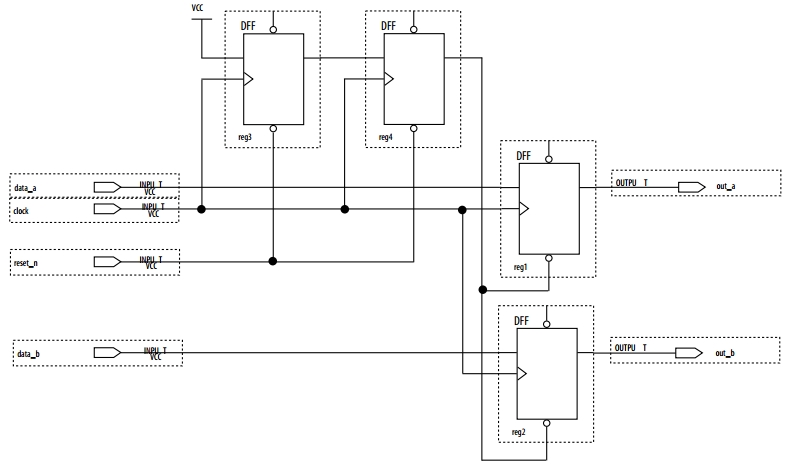

使用异步复位同步释放就可以消除上述缺点。所谓异步复位,同步释放就是在复位信号到来的时候不受时钟信号的同步,而是在复位信号释放的时候受到时钟信号的同步。异步复位同步释放的原理图和代码如下:

-

//Synchronized Asynchronous Reset module sync_async_reset ( input clock, input reset_n, input data_a, input data_b, output out_a, output out_b); reg reg1, reg2; reg reg3, reg4; assign out_a = reg1; assign out_b = reg2; assign rst_n = reg4; always @ (posedge clock, negedge reset_n) begin if (!reset_n) begin reg3 <= 1'b0; reg4 <= 1'b0; end else begin reg3 <= 1'b1; reg4 <= reg3; end end always @ (posedge clock, negedge rst_n) begin if (!rst_n) begin reg1 <= 1'b0; reg2 <= 1'b0; end else begin reg1 <= data_a; reg2 <= data_b; end end endmodule // sync_async_reset