用到的术语:

clock skew的产生

延时与时钟线的长度及被时钟线驱动的时序单元的负载电容、个数有关

由于时钟线长度及负载不同,导致时钟信号到达相邻两个时序单元的时间不同

于是产生所谓的clock skew

1、不绑定配置

在不绑定配置中,PLL只为Native PHY提供高速串行时钟,而低速的并行时钟由各通道的本地的CGB生成。由于

在不绑定配置中各通道互不相干,所以通道之间的clock skew是不能计算的。并且时钟网络引入的skew也不能补偿。

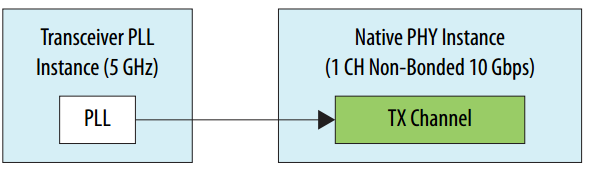

Single Channel x1 Non-Bonded

Single Channel x1 Non-Bonded 配置步骤:

1、例化PLL IP(ATX PLL, fPLL, or CMU PLL)

2、用PLL的参数化配置器对PLL进行配置

对于ATX pll不要包括Master CGB

对于fPLL设置反馈模式为Direct

对于CMU PLL指定参考时钟和数据速率

3、通道Native PHY的参数化编辑器设置eNative PHY IP Core TX Channel bonding mode 为 Non Bonded

4、连接PLL的输出tx_serial_clk 到相应的 tx_serial_clk0 。

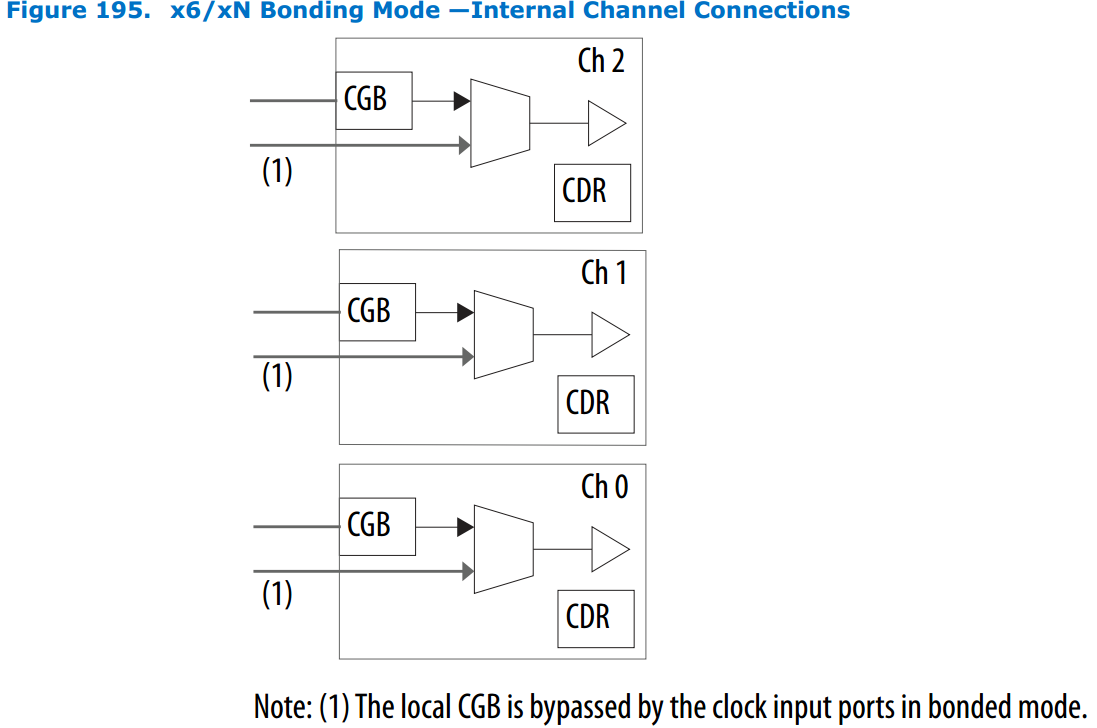

2、绑定配置

在绑定配置中,高速的串行时钟和低速的并行时钟都来自收发器PLL。在这种情况下,每个通道的CGB会被旁路,

并行时钟是由主CGB产生。而且在绑定配置中,通道之间的clock skew最小。

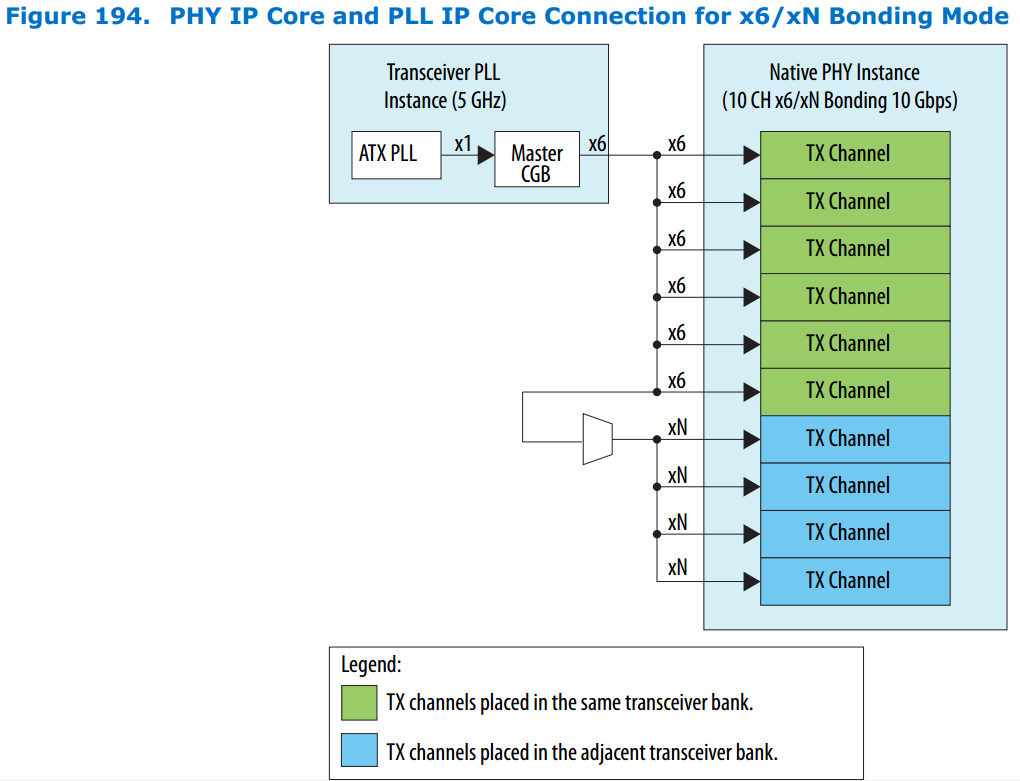

实现X6/XN通道绑定配置步骤:

1、例化ATX PLL或者fPLL。由于CMU PLL不能驱动Master CGB,所以不能用于绑定配置

2、在PLL的参数编辑器中使能Including Master clock Genaration Block,并且使能Enable bonding clock output ports 。

3、设置Native PHY的TX Channel Bonding Model为PMA Bonding或者PMA/PCS Bonding,并且设置通道数目。

4、连接PLL与Native PHY。在种情况下,PLL IP会生成tx_bonding_clocks输出信号,位宽为6, Native PHY会有一个

tx_bonding_clocks输入信号,位宽为6的通道位数,如果通道是5那么位宽为5x6。通道对PLL的tx_bonding_clocks复制

进行连接到Native PHY,{5{tx_bonding_clocks}}