CL (CAS latency)

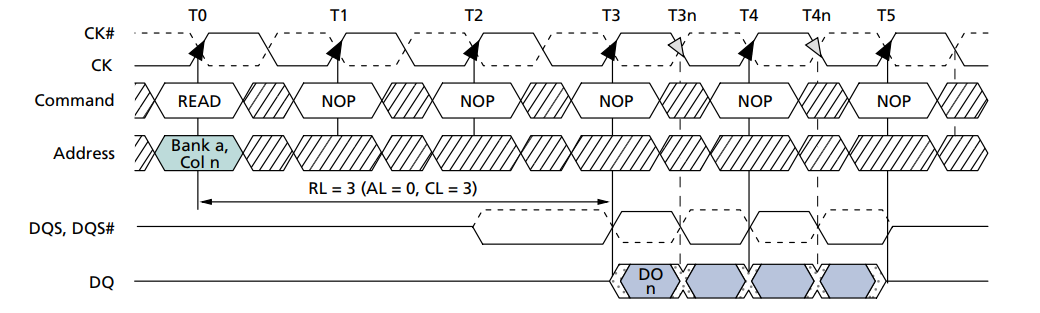

CL是从读命令发出到有效数据到DDR端口的延时,以时钟为单位。下图分别表示CL = 3和CL = 4的两种情况,

如果读命令在第n个时钟周期发出,CL = m,则读取的数据在第n+m个时钟时有效。

我们以MICRON 1Gb DDR2 SDRAM 为例,

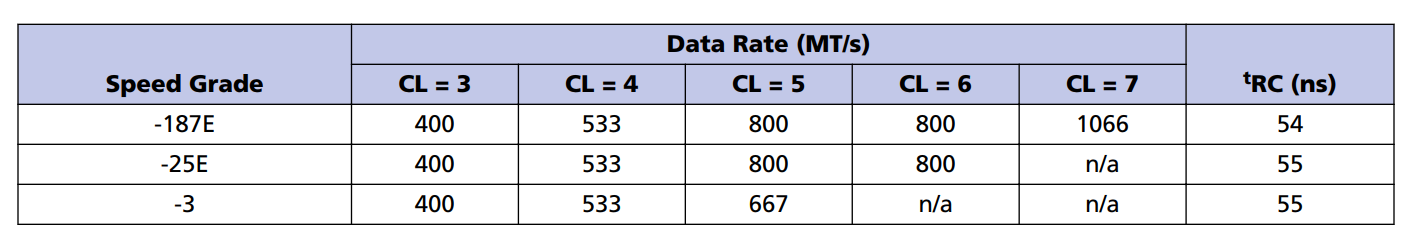

CL一般为3,4,5,6或者7个时钟,不同速度等级的DDR2支持的CL是不同的,如下图,速度等级为-187E的CL支持从3到7,而

速度等级为-25E的DDR2则只支持CL从3到6,速率等级为-3的DDR2支持CL人3到5。

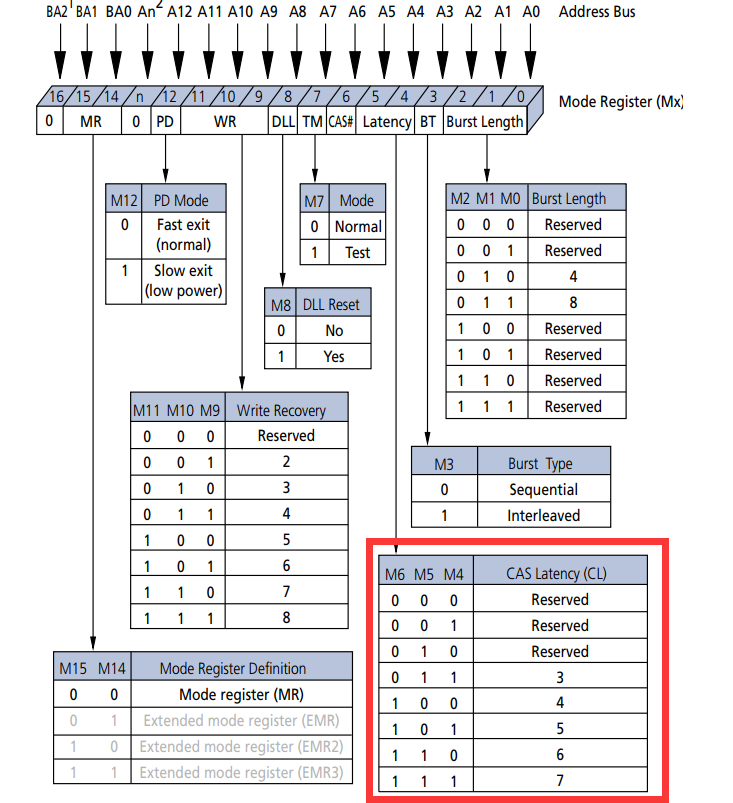

CL的长度在寄存器中设置

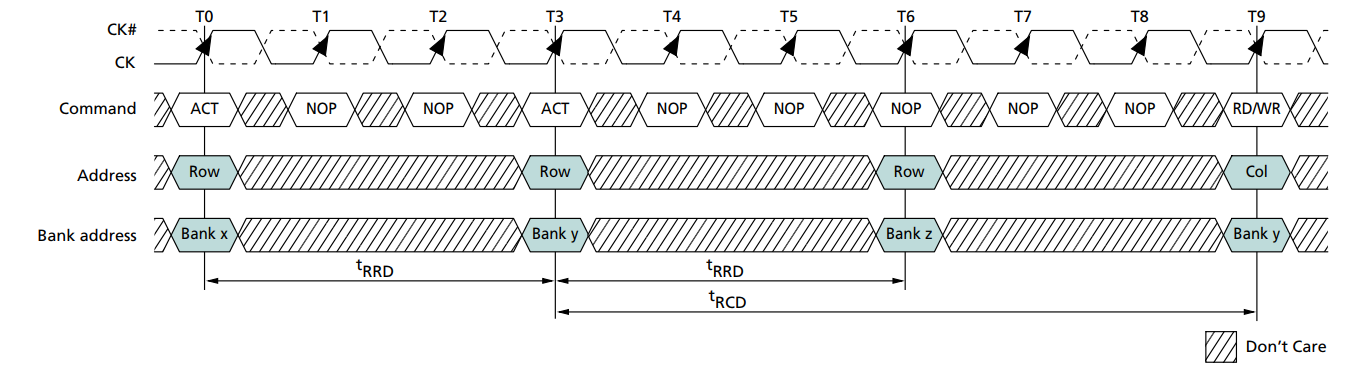

tRC :同一个Bank之间激活命令的时间间隔被定义为tRC。 一个激活命令发送后,同一Bank中不同行的激活命令发送时必须要先关闭前一个激命令,

这个操作称为预充电(precharged)。

tRRD:不同Bank之间的激活命令时间间隔被称为tRRD。

tFAW:在tFAW时间间隔内不能发送超过4个激活(ACTIVATE)命令。在DDR2中8个Bank的芯片中有这一要求。

RL :从列地址发出到数据端口上有效的数据输出延时

RL = AL + CL

tCCD:CAS#-to-CAS#命令之间的时延。读命令之间的时间间隔。如果要输出数据连续读命令之间的间隔是BL/2 个周期,为什么是BL/2?

因为命令是单速率而数据是双速率,如果突发数据速率是8,那读(写)数据输出只需要4个时钟周期。

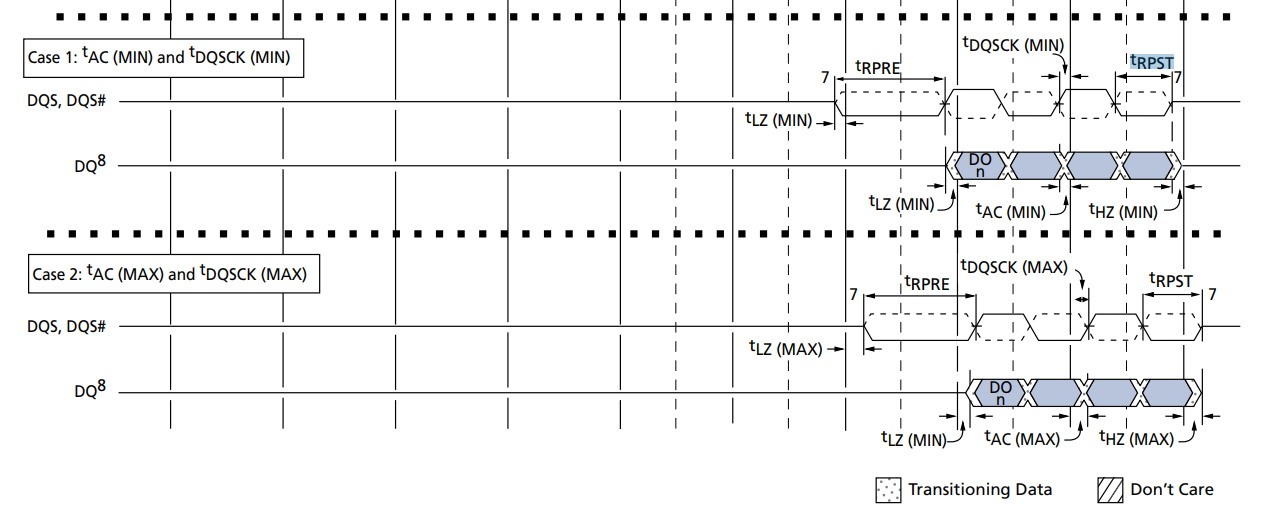

tRPRE:DQS读操作前同步,DQS为低电平,而DQS#为高电平

tRPST:DQS读操作后同步,DQS为低电平,而DQS#为高电平

tWTR :当WRITE命令之后跟随READ命令时,要满足tWTR的时间间隔要求

tWR:写突发之后一定要跟随一个PRECHARGE命令,时间间隔要求tWR.tWR的开始以数据突发最后为参考

tRCD :ACTIVATE-to-READ or WRITE delay

tRCD:在发送列读写命令时必须与前面的bank激活命令(行有效也在其中)有一个间隔,这个间隔被定义为tRCD,即RAS to CAS Delay(RAS 至CAS 延迟),可以理解为行选通周期。这是根据芯片存储阵列内部响应时间所需要的延迟,这个和芯片的工艺相关,是必然存在的一个延时。tRCD 是SDRAM 的一个重要硬件参数。

tRDC最终会以时钟的周期的方式体现,并向上取整数个时钟周期,其它时间参数也是如此,如对于266MHz时钟(tCK = 3.75ns),指定tRCD(MIN) = 20ns,计算得到5.3个时钟,向上取整为6个时钟

这里Delay(延迟)和Latency(潜伏)本质是不同的:Delay是事情要在这个时间之后开始,而Latency是事情已经发生,但是还不够稳定需要一个稳定时间。

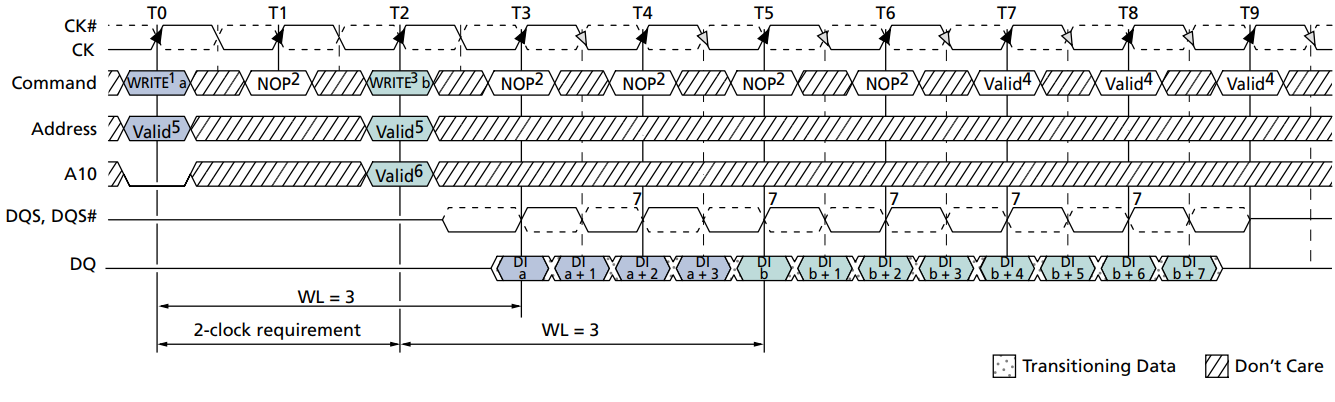

WL: WRITE command to first DQS transition写命令与第一个DQS上升沿之间的延迟。

tRP:单个BanK的PRECHARGE命令发出后,需要tRP时间段

tRPA: 所有BanK的PRECHARGE命令发出后,需要tRPA时间段

(8)AL(posted CAS additive latency )

这是一个间隔读的例子,先发送ACT命令,延时tRCD之后,再发送读命令,tRCD期间也是可以发送ACT命令,

但是两个ACT之间要有一定间隔是BL/2,本来ACT B2应该在ACT B1之后两个时钟周期间隔,但是tRCD

之后是RD,所以B2读出的数据与B1之间会有间隔这样会降低效率。

Post CAS就是为了提高DDR2内存的利用效率而设定的。在PostCAS操作中,CAS信号(读写/命令)能够被插

到RAS信号后面的一个时钟周期,但实际的CAS命令执行可以在附加延迟(Additive Latency,AL)后面。原来

的tRCD(RAS到CAS延迟)被AL所取代,且AL可以在DDR2的初始化时进行设置。由于CAS信号放在了RAS信

号后面一个时钟周期,因此别的bank激活命令(RAS)和CAS信号就不会产生冲突了。

这里我们就引出了AL这个概念:

附加延遲(AL, additive latency)是使用Post CAS技术时,总线上发出CAS信号(读写/命令)后到这个指令实际被执行的延时。

但是对于这个改进有两个地方值得注意的:

1、tRCD依然是存在的,这个是硬件的限制。而Post CAS技术改进的是命令的传输机制。我是这样理解的:Post CAS技术是对CAS信号指令提供一种芯片内部延时的机制,也可以理解为将CAS信号缓存AL时间后执行,这样不妨碍总线上的其他命令的发送。

2、Post CAS技术在单次的突发访问中是没有影响的,只有连续多次的突发访问才有性能的提升,但是对于内存操作一般不可能做单次的突发,就算程序这样做了硬件缓存机制也会做多次的突发。