一、原理图器件库

1.1 相关操作

-

修改封装和名称:【options】->【package properties】,只修改名称 右键 重命名

-

隐藏显示引脚名称编号:【options】->【part properties】,选择对应的修改为ture of false

-

批量修改引脚属性:选中要修改的引脚,右键【Edit Properties】

-

放置引脚阵列:【Place】->【Pin Array】

二、原理图

2.1 常用工具含义

-

off-page connector:端口连接符号,同一层次原理图中,同一页面或者不同页面中相同名称的端口在电气上是连接的,全局有效

-

net alias:网络标号,在同一页面中相同名称在电气上是连接的

-

备注:这个地方区别于AD,AD是只要网络标号一样,在所有页面中电气都是连接的

-

总线命名格式:总线名称[m:n] ,m和n代表总线信号的位数,比如DATA[0:3]。注意:总线名称最后一位不要起数字,比如DATA1[0:3]

-

电源和地符号:全局有效,跟符号形状无关,只跟name有关,不同形状的name相同电气连接

2.2 常用操作

-

Intersheet Reference 当一个原理图有很多页时,会用到很多端口连接符,添加Intersheet Reference后会在端口网络名称处显示该网络存在哪些页面中,选中dsn文件,Tools->annotate->Add Intersheet Reference

-

元器件重新编号:选中dsn文件,Tools->annotate->Incremental Reference update

-

原理图页面显示器件封装:右键->edit part->双击空白处->new->在name里面输入 PCB Footprint->OK->双击,选择Value only

三、焊盘制作

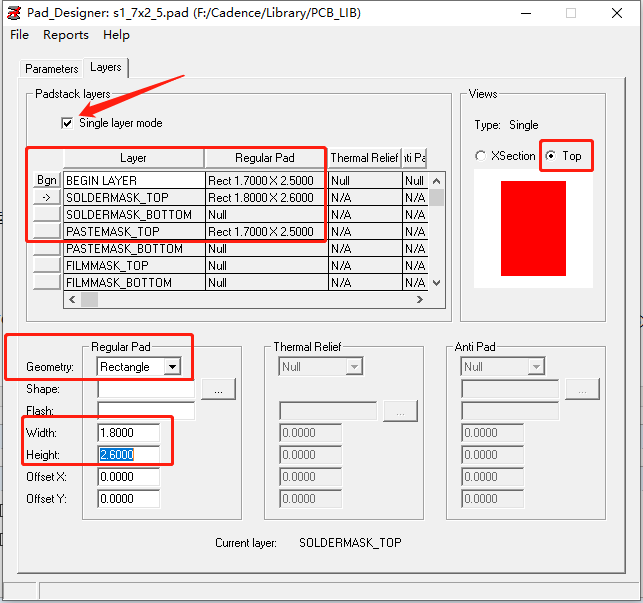

- 表贴焊盘:只需要操作Layer页面 ①新建,选择单位;②勾选single layer mode;③选择begin layer,选择形状,输入尺寸;④选择PASTMASK_TOP/BOTTOM,选择形状,输入尺寸(和begin layer尺寸一样大),或者直接将begin layer复制过来;⑤选择SOLDERMASK_TOP/BOTTOM,选择形状,输入尺寸(比begin layer尺寸大0.1mm)

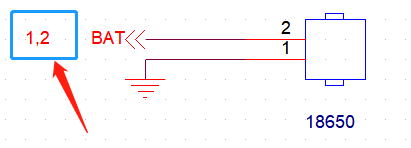

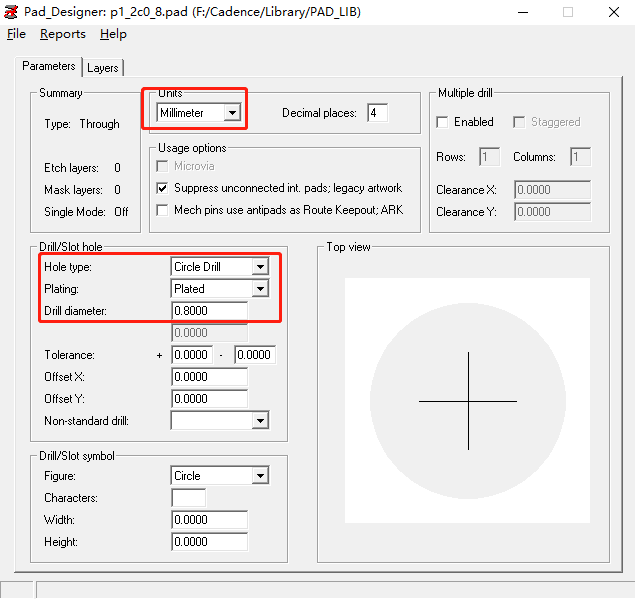

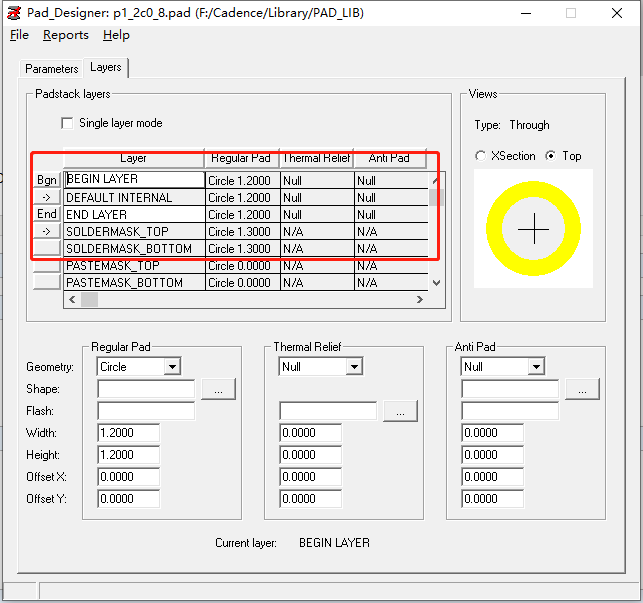

通孔焊盘:①新建,在Parameters界面填写单位,钻孔类型及尺寸;②切换带Layer界面,设计图二所示的几个选项:注意通孔不做钢网,所以可以不做PASTMASK层

3. 不规则焊盘:首先利用PCB editor制作shape图形,然后在pad制作软件对应的层形状选择shape

四、封装路径设置

打开PCB软件,setup-user preferences-paths-library,只需要设置padpath和psmpath,路径一直

五、封装制作

5.1 手动制作步骤

-

新建,设置页面(setup-design parameters)大小个栅格大小(setup-grids)

-

添加焊盘,设置焊盘数量属性,命令行输入坐标,放置

-

修改引脚编号 erit-text

-

添加外框等丝印 Add-line,添加1脚标识,class为packagegeometry,subclas为silk-top

-

放置place bound区域(覆盖整个焊盘和丝印即可),用敷铜来放置,class为packagegeometry,subclas为place bound-top

-

放置位号 ,class 为Ref Des,subclas为silk-top

六、PCB绘制

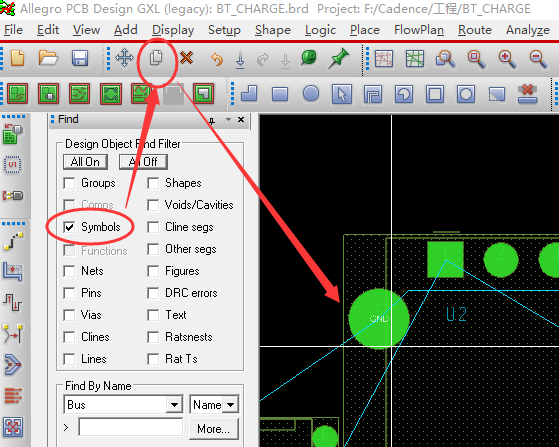

复制封装操作:选择symbols,然后选择copy,单击要复制的封装