INNOVUS/ICC吐出的netlist经过Formal/LEC验证后,Star-RC/QRC抽取RC寄生参数文件并读入到Tempus/PT分别做func/mbist/scan时序sign-off,写出SDF3.0用以后仿真,搭建后仿真的验证环境,添加sc/io/macro的verilog model,仿真输出VCD给Redhawk/Voltus做功耗/IR Drop分析。本文简要叙述下后仿真要点:

请关注下面公众号:全栈芯片工程师

http://weixin.qq.com/r/0jgYHZDEXlgiKNR_b21W (二维码自动识别)

(一) VCS选项,主要介绍几个关键选项。

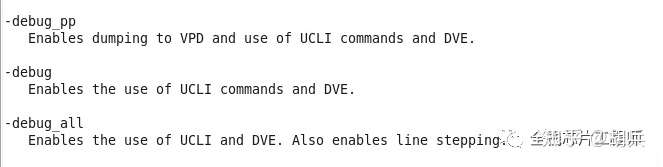

1)-debug选项,为了导出VPD通常选择-debug_pp;

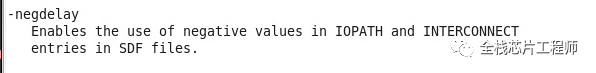

2)-negdelay,支持SDF中的负延时;

3)-ssf自动加载fsdb;

4)-ucli模式,在-debug模式下才使能;

5)+neg_tchk,支持负延时检查;

6)+nospecify/+notimingcheck,忽略path delay和specify延时;

7)+delay_mode_zero,去除仿真中的延迟信息,所有的延时为0;

(二)SDF annotated

$sdf_annotate ([sdf_file], top.U_DIGITAL_TOP, [sdf_configfile], [sdf_logfile],[mtm_spec], [scale_factors], [scale_type]);

- sdf_file指定时序签核输出的sdf文件及其路径;

- sdf_configfile”指定sdf配置文件,一般缺省;

- sdf_logfile指定sdf的log生成文件,该文件会保存VCS在运行过程中产生的Error和Warning信息。为了规VCS默认情况下不会记录超过10个以上的error信息/warning信息到log文件,可通过+sdfverbose选项来开启VCS记录所有信息;

- mtm_spec指定VCS反标哪一类延迟信息。可以使用MINIMUM,TYPICAL,MAXIMUM,TOOL_CONTROL(default);

- scale_factors指定minimum,typical,maximum延迟的因子。默认值是“1.0:1.0:1.0”

- scale_type指定在缩放比例之前使用的SDF 文件里面延迟值,可能的值有“FROM_TYPICAL”,”FROM_MIMINUM”,”FROM_MAXIMUM”,”FROM_MTM”(默认值),一般缺省;

(三)初始化寄存器的值(不常用)

设置寄存器初始值文件:

#init0_regs.ucli

force -deposit tb.U_DIGITAL.reg_A 0在仿真的零时刻用下面的方式加载这个文件

ucli% source ./init0_regs.ucli

(四)关某些寄存器的时序检查(常用)

#notiming.list

instance { tb.U_TOP.reg} { noTiming };

在仿真的时候加载这个文件,避免引起X态传递。

VCS +optconfigfile+notiming.list(五)导出VCD文件

VCD是不压缩的文本格式,兼容性好,缺点是文件太大。后仿先写出高压缩比的FSDB文件,再转成VCD。可指定转换起止时间、结束时间。

fsdb2vcd xxx.fsdb -o xxx.vcd -bt 1000ns -et 2000ns

ISP处理后仿效果

关注微信公众号

关注微信公众号

请关注下面公众号:全栈芯片工程师

http://weixin.qq.com/r/0jgYHZDEXlgiKNR_b21W (二维码自动识别)

附录:

前言:下表所列為VCS常用的Command。

常用的編譯選項

| No. | 命令 | 描述 |

| 1 | +define+<macro_name>=<value> | 命令行进行宏定义,在代码中使用了`ifdef 编译指令 |

| 2 | +mindelays | 器件延时使用sdf 文件中的最小值(sdf 文件中的时序(min:typ:max)) |

| 3 | +maxdelays | 器件延时使用sdf 文件中的最大值 |

| 4 | –v <filename> | 导入库文件的verilog 模型(只编译使用到的module),-v 在verdi 中无法trace,被当作一个器件,不能追踪到内部Module 查找路径,在添加module 时,会在此目录下查找,当编译某文件,如果里面有例化某个module,则会编译这个文件下的内容 |

| 5 | -y < directory > | Module 查找路径,在添加module 时,会在此目录下查找,当编译某文件,如果里面有例化某个module,则会编译这个文件夹下的内容与-v 功能差不多,一个是指定文件,一个是指定文件夹 |

| 6 | +incdir+directory+ | 指定VCS 搜索`include 内文件的目录 |

| 7 | -full64 | 支持64 位模式运行 |

| 8 | -R | 编译完后立刻运行 |

| 9 | –sverilog | 支持systemverilog 语法(vcs 用,verid 用-sv) |

| 10 | +v2k | 支持verilog 2001 特性 |

| 11 | -lca | Limited Customer Availability,支持动态数据类型associative Array,dynamic Array,smart Queue,string, event,class |

| 12 | –debug_all | 支持所有debug 操作,DVE 选项,可以查看所有断点(line,time,value,event etc) all 就是加权限。+w 是写,+r 是读,+f 是force, +l 是支持ucli 的单步调试, +n 是对网表操作。具体可以看手册。+all 就是把所有的权限全开 |

| 13 | –debug_acess+all | 在VCS 编译的时候不用再加-p novas.tab pli.a 来定verdi 的路径。直接在simv 的ucli 脚本里面call $fsdbdumpfile想dump vpd 的时候至今换dump file XXX不用重新编译。版本有差异 |

| 14 | –fsdb | 调用Verdi PLI 库,支持fsdb 波形 |

| 15 | +vcs+lic+wait | 等待vcs license |

| 16 | +plusarg_save | 将某些runtime options 加入到编译中,源代码中存在$test$plusargs(“name”),如果字符匹配则为真,反之为例:在tc 中有代码if($test$plusargs(“testcase0”)) $在Makefile 命令中加入make testcase0,则if 为真,打印 |

| 17 | +libext+ | 在库目录内搜索指定后缀名文件进行编译 |

| 18 | +verilog2001ext+ | Specifies a file name extension for Verilog2001 source file |

| 19 | +systemverilogext+ | Specifies a file name extension for SystemVerilog source file |

| 20 | +warn=[no]ID|none|all… | 打开或关闭warning 信息 |

| 21 | +optconfigfile+<filename> | 定义VCS 配置文件,第一级同步寄存器不检查看用一个文件输入 |

| 22 | -o name | 指定运行文件名称 |

| 23 | -Mdir=directory_path | 指定增量编译的目录(默认为csrc) |

| 24 | -l sim | log 生成指定log 文件 |

| 25 | +ntb_random_seed=value | 指定仿真随机种子 |

| 26 | +ntb_random_seed_automatic | VCS 自动生成随机种子 |

| 27 | -timescale=1ns/10ps | 命令行定义仿真时间刻度,若rtl 中有timescale 的定义,则会覆盖makefile 中的定义 |

| 28 | –override_timescale=1ns/10ps | 覆盖源代码中的仿真时间单位和精度,最好别用,否则会把模型的时间单位覆盖,可能导致模型功能错误 |

| 29 | -pvalue+tb_top.CYCLE=value | 对指定参数进行赋值-pvalue+tb_top.CYCLE=${period} , 那么在命令行就可以使用vcs xxx period=yy 来改变CYCLE |

| 30 | –sv | 支持systemverilog 语法(verdi 有此配置,vcs 没有) |

| 31 | –ssf | 自动加载fsdb 文件 |

| 32 | +neg_tchk | 负延迟检查,P&R 后仿需要加上此选项, |

| 33 | +delay_mode_zero | 去除仿真中的延迟信息,所有的延时为0,当使用了此选项,specify 中的$setup()检测失败,似乎把specparam 设置的变量改为0 了 |

| 34 | -notimingcheck | 忽略仿真中的时序检查,会忽略specify 语句中的检查,小心使用,有些模拟如flash 的时序检查是通过specify 语句来实现,如果使用了,则无法check时序Specify 里面的内容不起作用,相当于0 延时和不做时序检查 |

| 35 | +maxdelays | 选择sdf 文件中的max 延迟信息 |

| 36 | +overlap | SDF 反标后的精确时序检查 |

| 37 | +sdfverbose | 打印出详细的SDF 反标信息,超过10 个warning error, |

| 38 | –negdelay | 允许sdf 文件中iopath 和interconnect 的负延时反标,Pr 后仿需要加上此选项,很多工艺库的holdtime 为负值 |

| 39 | -cm line+tgl+cond+fsm | 指定覆盖率类型 |

| 40 | -cm_dir directory_path (default: simv.cm | 指定覆盖率文件名字和路径 |

| 41 | -cm_hier vcm.cfg (+tree tb_top dut) | 保存模块的层次信息 |

| 42 | -cm_name test_name | 定义覆盖率报告文件名 |

| 43 | –cm_log | 指定覆盖率log 文件名 |

| 44 | -assert | 定义支持断言 |

| 45 | +delay_mode_path | 模块的延时使用路径延时 |

| 46 | +delay_mode_distributed | 模块的延时使用分布延时,对于分布延时,只要脉冲宽度小直接过滤掉(针对惯性延时) |

| 47 | +delay_mode_unit | 模块的延时使用所有时间精度中的最小值,specify 中的延迟不起作用,#后的所有数字变为1,单位使用最小精度,所有timescale 中的最小精度用于Tmax 产生的atpg 验证平台不带时序仿真Enables simulation of TetraMAX’s testbench in zero delay mode |

| 48 | +delay_mode_zero | 模块的延时使用0 延时,不指定延时模式时,vcs 使用路径延时和分布延时中的最大值 |

| 49 | +loopreport | 高版本vcs 会报loop |

| 50 | +race | 自动产生race.out 文件,列出竞争 |

| 51 | +cli+1,2,3 | 使用ucli 模式,一般为3,默认模式 |

| 52 | -ucli | 仿真时,进入ucli 交互模式 |

| No. | 命令 | 描述 |

| 1 | +define+<macro_name>=<value> | 命令行进行宏定义,在代码中使用了`ifdef 编译指令 |

| 2 | +mindelays | 器件延时使用sdf 文件中的最小值(sdf 文件中的时序(min:typ:max)) |

| 3 | +maxdelays | 器件延时使用sdf 文件中的最大值 |

| 4 | –v <filename> | 导入库文件的verilog 模型(只编译使用到的module),-v 在verdi 中无法trace,被当作一个器件,不能追踪到内部Module 查找路径,在添加module 时,会在此目录下查找,当编译某文件,如果里面有例化某个module,则会编译这个文件下的内容 |

| 5 | -y < directory > | Module 查找路径,在添加module 时,会在此目录下查找,当编译某文件,如果里面有例化某个module,则会编译这个文件夹下的内容与-v 功能差不多,一个是指定文件,一个是指定文件夹 |

| 6 | +incdir+directory+ | 指定VCS 搜索`include 内文件的目录 |

| 7 | -full64 | 支持64 位模式运行 |

| 8 | -R | 编译完后立刻运行 |

| 9 | –sverilog | 支持systemverilog 语法(vcs 用,verid 用-sv) |

| 10 | +v2k | 支持verilog 2001 特性 |

| 11 | -lca | Limited Customer Availability,支持动态数据类型associative Array,dynamic Array,smart Queue,string, event,class |

| 12 | –debug_all | 支持所有debug 操作,DVE 选项,可以查看所有断点(line,time,value,event etc) all 就是加权限。+w 是写,+r 是读,+f 是force, +l 是支持ucli 的单步调试, +n 是对网表操作。具体可以看手册。+all 就是把所有的权限全开 |

| 13 | –debug_acess+all | 在VCS 编译的时候不用再加-p novas.tab pli.a 来定verdi 的路径。直接在simv 的ucli 脚本里面call $fsdbdumpfile想dump vpd 的时候至今换dump file XXX不用重新编译。版本有差异 |

| 14 | –fsdb | 调用Verdi PLI 库,支持fsdb 波形 |

| 15 | +vcs+lic+wait | 等待vcs license |

| 16 | +plusarg_save | 将某些runtime options 加入到编译中,源代码中存在$test$plusargs(“name”),如果字符匹配则为真,反之为例:在tc 中有代码if($test$plusargs(“testcase0”)) $在Makefile 命令中加入make testcase0,则if 为真,打印 |

| 17 | +libext+ | 在库目录内搜索指定后缀名文件进行编译 |

| 18 | +verilog2001ext+ | Specifies a file name extension for Verilog2001 source file |

| 19 | +systemverilogext+ | Specifies a file name extension for SystemVerilog source file |

| 20 | +warn=[no]ID|none|all… | 打开或关闭warning 信息 |

| 21 | +optconfigfile+<filename> | 定义VCS 配置文件,第一级同步寄存器不检查看用一个文件输入 |

| 22 | -o name | 指定运行文件名称 |

| 23 | -Mdir=directory_path | 指定增量编译的目录(默认为csrc) |

| 24 | -l sim | log 生成指定log 文件 |

| 25 | +ntb_random_seed=value | 指定仿真随机种子 |

| 26 | +ntb_random_seed_automatic | VCS 自动生成随机种子 |

| 27 | -timescale=1ns/10ps | 命令行定义仿真时间刻度,若rtl 中有timescale 的定义,则会覆盖makefile 中的定义 |

| 28 | –override_timescale=1ns/10ps | 覆盖源代码中的仿真时间单位和精度,最好别用,否则会把模型的时间单位覆盖,可能导致模型功能错误 |

| 29 | -pvalue+tb_top.CYCLE=value | 对指定参数进行赋值-pvalue+tb_top.CYCLE=${period} , 那么在命令行就可以使用vcs xxx period=yy 来改变CYCLE |

| 30 | –sv | 支持systemverilog 语法(verdi 有此配置,vcs 没有) |

| 31 | –ssf | 自动加载fsdb 文件 |

| 32 | +neg_tchk | 负延迟检查,P&R 后仿需要加上此选项, |

| 33 | +delay_mode_zero | 去除仿真中的延迟信息,所有的延时为0,当使用了此选项,specify 中的$setup()检测失败,似乎把specparam 设置的变量改为0 了 |

| 34 | -notimingcheck | 忽略仿真中的时序检查,会忽略specify 语句中的检查,小心使用,有些模拟如flash 的时序检查是通过specify 语句来实现,如果使用了,则无法check时序Specify 里面的内容不起作用,相当于0 延时和不做时序检查 |

| 35 | +maxdelays | 选择sdf 文件中的max 延迟信息 |

| 36 | +overlap | SDF 反标后的精确时序检查 |

| 37 | +sdfverbose | 打印出详细的SDF 反标信息,超过10 个warning error, |

| 38 | –negdelay | 允许sdf 文件中iopath 和interconnect 的负延时反标,Pr 后仿需要加上此选项,很多工艺库的holdtime 为负值 |

| 39 | -cm line+tgl+cond+fsm | 指定覆盖率类型 |

| 40 | -cm_dir directory_path (default: simv.cm | 指定覆盖率文件名字和路径 |

| 41 | -cm_hier vcm.cfg (+tree tb_top dut) | 保存模块的层次信息 |

| 42 | -cm_name test_name | 定义覆盖率报告文件名 |

| 43 | –cm_log | 指定覆盖率log 文件名 |

| 44 | -assert | 定义支持断言 |

| 45 | +delay_mode_path | 模块的延时使用路径延时 |

| 46 | +delay_mode_distributed | 模块的延时使用分布延时,对于分布延时,只要脉冲宽度小直接过滤掉(针对惯性延时) |

| 47 | +delay_mode_unit | 模块的延时使用所有时间精度中的最小值,specify 中的延迟不起作用,#后的所有数字变为1,单位使用最小精度,所有timescale 中的最小精度用于Tmax 产生的atpg 验证平台不带时序仿真Enables simulation of TetraMAX’s testbench in zero delay mode |

| 48 | +delay_mode_zero | 模块的延时使用0 延时,不指定延时模式时,vcs 使用路径延时和分布延时中的最大值 |

| 49 | +loopreport | 高版本vcs 会报loop |

| 50 | +race | 自动产生race.out 文件,列出竞争 |

| 51 | +cli+1,2,3 | 使用ucli 模式,一般为3,默认模式 |

| 52 | -ucli | 仿真时,进入ucli 交互模式 |

VCS常用的編譯選項

| 編號 | 选项 | 说明 |

| 1 | -assert dumpoff | enable_diag | filter_past | 定义SystemVerilog断言(SVA)dumpoff:禁止将SVA信息DUMP到VPD中enable_diag:使能SVA结果报告由运行选项进一步控制filter_past:忽略$past中的子序列 |

| 2 | -cm <options> | 指定覆盖率的类型,包括:line(行覆盖)、cond(条件覆盖)、fsm(状态机覆盖)、tgl(翻转率覆盖)、path(路径覆盖)、branch(分支覆盖)和assert(断言覆盖)。如果包括两种或以上的覆盖率类型,可用“+”,如-cm line+cond+fsm+tgl |

| 3 | -cm_assert_hier <filename> | 将SVA覆盖率统计限定在文件列表中指定的module层次。 |

| 4 | -cm_cond <arguments> | 进一步细化条件覆盖率的统计方式,包括:basic,std,full,allops,event,anywidth,for,tf,sop等选项。 |

| 5 | -cm_count | 在统计是否覆盖的基础上,进一步统计覆盖的次数 |

| 6 | -cm_dir <directory_path_name> | 指定覆盖率统计结果的存放路径,默认是simv.cm |

| 7 | -cm_hier <filename> | 指定覆盖率统计的范围,范围在文件中定义,可以指定module名、层次名和源文件等。 |

| 8 | -cm_log <filename> | 指定仿真过程中记录覆盖率的log文件名 |

| 9 | -cm_name <filename> | 指定保存覆盖率结果的文本文件的名称 |

| 10 | -cm obc | 使能可观察(observed)覆盖率的编译。传统的覆盖率跟功能的正确性毫无关联,可观察覆盖率通过设置观察点,一定程度上将代码行覆盖率与功能正确性关联起来。 |

| 11 | -comp64 | 在64-bit模式下对设计进行编译,并生成32-bit格式的可执行文件用于32-bit模式仿真 |

| 12 | -debug 或 -debug_all | 使能UCLI命令行 |

| 13 | -e <new_name_for_main> | 指定PLI应用时main()程序的名称 |

| 14 | -f <filename> | 指定文件列表的文件名,文件中可包括源代码文件的路径和名称,也可以包括编译选项参数 |

| 15 | -file filename | 类似于-f,但文件内容更灵活,可以包含PLI选项和对象文件,可以使用转义字符等 |

| 16 | -full64 | 在64-bit模式下编译,生成64-bit模式仿真的可执行文件 |

| 17 | -h or -help | 列举常用的编译选项和运行选项的参数 |

| 18 | -I | 交互模式的编译,让VCS自动包括+cli,-P virsims.tab选项,并支持VirSim后处理模式下生成VCD+文件。 |

| 19 | -ID | 显示及其的hostid或dongle ID |

| 20 | -ignore <keyword_argument> | 屏蔽SV中unique/priority型的if或case语句的告警信息,参数包括:unique_checks、priority_checks、all。 |

| 21 | -j<number_of_processes> | 设定并行编译的进程数,“j”后面没有空格 |

| 22 | -l <filename> | 指定记录VCS编译和运行信息的log文件名 |

| 23 | -line | 使能VriSim中的单步运行 |

| 24 | -lmc-swift | 使能LMC SWIFT接口 |

| 25 | -Mdir=<directory> | 指定一个目录让VCS存储编译产生的文件,默认是csrc |

| 26 | -Mlib=<directory> | 指定一个目录让VCS搜索某个模块是否需要重新编译。与-Mdir配合,可以实现不同模块的增量编译。 |

| 27 | -Mmakeprogram=<program> | 指定用于make对象的程序,默认是make |

| 28 | -Mupdate[=0] | 默认情况下,VCS编译时会覆盖上次编译生成的makefile。如果想保留上次的makefile,使用-Mupdate=0;如果不带=0,则进行增量编译,并覆盖上次的makefile。 |

| 29 | -noIncrComp | 关闭增量编译 |

| 30 | -notice | 显示详细的诊断信息 |

| 31 | -ntb | 使能ntb(Native TestBench),支持OpenVera验证平台语言结构。 |

| 32 | -o <name> | 指定编译生成的可执行文件的名称,默认是simv |

| 33 | -timescale=<time_unit>/<time_precision> | 源代码文件中有的包括`timescale编译指令,有的不包括,如果在VCS命令行中,不包括`timescale的源代码文件在最前面,VCS会停止编译。使用-timescale选项为这些在前面且又没有`timescale的源文件指定timescale |

| 34 | -override_timescale=<time_unit>/<time_precision> | 让源文件统一使用指定的timescale |

| 35 | -P <pli.tab> | 指定PLI表文件 |

| 36 | -pvalues+<parameter_name>=<value> | 改变指定参数的值 |

| 37 | -parameters <filename> | 通过文件的方式改变参数的值,参数的路径和改变的值均在文件中定义 |

| 38 | -q | 安静模式,屏蔽VCS的编译信息 |

| 39 | -R | 在编译之后立即执行产生的可执行文件 |

| 40 | -s | 刚开始仿真时即停止,一般与-R和+cli配合使用 |

| 41 | -V | 使能verbose模式 |

| 42 | -v <filename> | 指定verilog库文件 |

| 43 | -y <dir_pathname> | 指定verilog库路径 |

| 44 | +libext+<extension> | 让VCS在verilog库路径下搜索指定的扩展名文件,与-y配合 |

| 45 | -vera | 指定标准的Vera PLI表文件和对象库 |

| 46 | +acc+1|2|3|4 | 使能PLI中的ACC(PLI 1.0的一种方式) |

| 47 | +cli+[<module_name>=]1|2|3|4 | 使能CLI调试功能 |

| 48 | +autoprotect[<file_suffix>] | 生成一个加密的源文件 |

| 49 | +protect[<file_suffix>] | 生成一个加密的源文件,只加密`protect/`endprotect部分 |

| 50 | +putprotect+<target_dir> | 指定加密文件存放的目录 |

| 51 | +csdf+precompile | 在VCS编译源代码时预先SDF文件 |

| 52 | +define+<macro_name>=<value> | 定义一个文本宏,与源文件中的`ifdef配合 |

| 53 | +error+<n> | 将编译时运行的NTB错误增加到N |

| 54 | +incdir+<directory> | 指定VCS搜索`include指令使用的包含文件的目录,可以用“+”定义多个目录。 |

| 55 | +maxdelays | 使用SDF文件中的max值 |

| 56 | +mindelays | 使用SDF文件中的min值 |

| 57 | +typdelays | 使用SDF文件中的typ值 |

| 58 | +nbaopt | 删除非阻塞赋值语句中的延时 |

| 59 | +neg_tchk | 使能时序检查中的负延时 |

| 60 | +nospecify | 屏蔽specify块中的路径延时和时序检查 |

| 61 | +notimingcheck | 屏蔽specify块中的时序检查 |

| 62 | +nowarnTFMPC | 屏蔽编译时的“Too few module port connections”告警信息 |

| 63 | +no_notifier | 屏蔽一些时序检查系统任务中定义的notifier寄存器的翻转(toggling),但不影响时序violation的报告 |

| 64 | +no_tchk_msg | 屏蔽时序检查的告警信息,但不关闭时序检查时notifier寄存器的翻转(toggling) |

| 65 | +optconfigfile+<filename> | 指定Radiant技术和二态仿真用到的配置文件名 |

| 66 | +prof | 让VCS在仿真过程中生成一个vcs.prof文件,记录设计中最耗CPU时间的module、层次和verilog结构 |

| 67 | +race | 让VCS在仿真过程中生成一个race.out文件,记录设计中所有的竞争冒险 |

| 68 | +radincr | 增量编译时使能Radiant技术 |

| 69 | +sdf_nocheck_celltype | SDF反标时不检查SDF文件中的CELLTYPE的一致性 |

| 70 | +sdfverbose | 显示SDF反标时的详细告警和错误信息 |

| 71 | +v2k | 支持Verilog-2001标准 |

| 72 | +vc[+abstract][+allhdrs][+list] | 使用DirectC接口时,使能verilog直接调用C/C++函数 |

| 73 | +vcs+flush+log | 加速编译仿真时log文件缓存的刷新频率 |

| 74 | +vcs+flush+all | +vcs+flush+log,+vcs+flush+dump和+vcs+flush+fopen的集合 |

| 75 | +vcs+initmem+0|1|x|z | 初始化设计中所有存储器的值 |

| 76 | +vcs+initreg+0|1|x|z | 初始化设计中所有寄存器的值 |

| 77 | +vcs+lic+wait | 一直等待license |

| 78 | +vpi | 使能VPI |

| 79 | +warn=[no]ID|none|all,... | 使能或关闭告警信息 |

| 編號 | 选项 | 说明 |

| 1 | -assert dumpoff | enable_diag | filter_past | 定义SystemVerilog断言(SVA)dumpoff:禁止将SVA信息DUMP到VPD中enable_diag:使能SVA结果报告由运行选项进一步控制filter_past:忽略$past中的子序列 |

| 2 | -cm <options> | 指定覆盖率的类型,包括:line(行覆盖)、cond(条件覆盖)、fsm(状态机覆盖)、tgl(翻转率覆盖)、path(路径覆盖)、branch(分支覆盖)和assert(断言覆盖)。如果包括两种或以上的覆盖率类型,可用“+”,如-cm line+cond+fsm+tgl |

| 3 | -cm_assert_hier <filename> | 将SVA覆盖率统计限定在文件列表中指定的module层次。 |

| 4 | -cm_cond <arguments> | 进一步细化条件覆盖率的统计方式,包括:basic,std,full,allops,event,anywidth,for,tf,sop等选项。 |

| 5 | -cm_count | 在统计是否覆盖的基础上,进一步统计覆盖的次数 |

| 6 | -cm_dir <directory_path_name> | 指定覆盖率统计结果的存放路径,默认是simv.cm |

| 7 | -cm_hier <filename> | 指定覆盖率统计的范围,范围在文件中定义,可以指定module名、层次名和源文件等。 |

| 8 | -cm_log <filename> | 指定仿真过程中记录覆盖率的log文件名 |

| 9 | -cm_name <filename> | 指定保存覆盖率结果的文本文件的名称 |

| 10 | -cm obc | 使能可观察(observed)覆盖率的编译。传统的覆盖率跟功能的正确性毫无关联,可观察覆盖率通过设置观察点,一定程度上将代码行覆盖率与功能正确性关联起来。 |

| 11 | -comp64 | 在64-bit模式下对设计进行编译,并生成32-bit格式的可执行文件用于32-bit模式仿真 |

| 12 | -debug 或 -debug_all | 使能UCLI命令行 |

| 13 | -e <new_name_for_main> | 指定PLI应用时main()程序的名称 |

| 14 | -f <filename> | 指定文件列表的文件名,文件中可包括源代码文件的路径和名称,也可以包括编译选项参数 |

| 15 | -file filename | 类似于-f,但文件内容更灵活,可以包含PLI选项和对象文件,可以使用转义字符等 |

| 16 | -full64 | 在64-bit模式下编译,生成64-bit模式仿真的可执行文件 |

| 17 | -h or -help | 列举常用的编译选项和运行选项的参数 |

| 18 | -I | 交互模式的编译,让VCS自动包括+cli,-P virsims.tab选项,并支持VirSim后处理模式下生成VCD+文件。 |

| 19 | -ID | 显示及其的hostid或dongle ID |

| 20 | -ignore <keyword_argument> | 屏蔽SV中unique/priority型的if或case语句的告警信息,参数包括:unique_checks、priority_checks、all。 |

| 21 | -j<number_of_processes> | 设定并行编译的进程数,“j”后面没有空格 |

| 22 | -l <filename> | 指定记录VCS编译和运行信息的log文件名 |

| 23 | -line | 使能VriSim中的单步运行 |

| 24 | -lmc-swift | 使能LMC SWIFT接口 |

| 25 | -Mdir=<directory> | 指定一个目录让VCS存储编译产生的文件,默认是csrc |

| 26 | -Mlib=<directory> | 指定一个目录让VCS搜索某个模块是否需要重新编译。与-Mdir配合,可以实现不同模块的增量编译。 |

| 27 | -Mmakeprogram=<program> | 指定用于make对象的程序,默认是make |

| 28 | -Mupdate[=0] | 默认情况下,VCS编译时会覆盖上次编译生成的makefile。如果想保留上次的makefile,使用-Mupdate=0;如果不带=0,则进行增量编译,并覆盖上次的makefile。 |

| 29 | -noIncrComp | 关闭增量编译 |

| 30 | -notice | 显示详细的诊断信息 |

| 31 | -ntb | 使能ntb(Native TestBench),支持OpenVera验证平台语言结构。 |

| 32 | -o <name> | 指定编译生成的可执行文件的名称,默认是simv |

| 33 | -timescale=<time_unit>/<time_precision> | 源代码文件中有的包括`timescale编译指令,有的不包括,如果在VCS命令行中,不包括`timescale的源代码文件在最前面,VCS会停止编译。使用-timescale选项为这些在前面且又没有`timescale的源文件指定timescale |

| 34 | -override_timescale=<time_unit>/<time_precision> | 让源文件统一使用指定的timescale |

| 35 | -P <pli.tab> | 指定PLI表文件 |

| 36 | -pvalues+<parameter_name>=<value> | 改变指定参数的值 |

| 37 | -parameters <filename> | 通过文件的方式改变参数的值,参数的路径和改变的值均在文件中定义 |

| 38 | -q | 安静模式,屏蔽VCS的编译信息 |

| 39 | -R | 在编译之后立即执行产生的可执行文件 |

| 40 | -s | 刚开始仿真时即停止,一般与-R和+cli配合使用 |

| 41 | -V | 使能verbose模式 |

| 42 | -v <filename> | 指定verilog库文件 |

| 43 | -y <dir_pathname> | 指定verilog库路径 |

| 44 | +libext+<extension> | 让VCS在verilog库路径下搜索指定的扩展名文件,与-y配合 |

| 45 | -vera | 指定标准的Vera PLI表文件和对象库 |

| 46 | +acc+1|2|3|4 | 使能PLI中的ACC(PLI 1.0的一种方式) |

| 47 | +cli+[<module_name>=]1|2|3|4 | 使能CLI调试功能 |

| 48 | +autoprotect[<file_suffix>] | 生成一个加密的源文件 |

| 49 | +protect[<file_suffix>] | 生成一个加密的源文件,只加密`protect/`endprotect部分 |

| 50 | +putprotect+<target_dir> | 指定加密文件存放的目录 |

| 51 | +csdf+precompile | 在VCS编译源代码时预先SDF文件 |

| 52 | +define+<macro_name>=<value> | 定义一个文本宏,与源文件中的`ifdef配合 |

| 53 | +error+<n> | 将编译时运行的NTB错误增加到N |

| 54 | +incdir+<directory> | 指定VCS搜索`include指令使用的包含文件的目录,可以用“+”定义多个目录。 |

| 55 | +maxdelays | 使用SDF文件中的max值 |

| 56 | +mindelays | 使用SDF文件中的min值 |

| 57 | +typdelays | 使用SDF文件中的typ值 |

| 58 | +nbaopt | 删除非阻塞赋值语句中的延时 |

| 59 | +neg_tchk | 使能时序检查中的负延时 |

| 60 | +nospecify | 屏蔽specify块中的路径延时和时序检查 |

| 61 | +notimingcheck | 屏蔽specify块中的时序检查 |

| 62 | +nowarnTFMPC | 屏蔽编译时的“Too few module port connections”告警信息 |

| 63 | +no_notifier | 屏蔽一些时序检查系统任务中定义的notifier寄存器的翻转(toggling),但不影响时序violation的报告 |

| 64 | +no_tchk_msg | 屏蔽时序检查的告警信息,但不关闭时序检查时notifier寄存器的翻转(toggling) |

| 65 | +optconfigfile+<filename> | 指定Radiant技术和二态仿真用到的配置文件名 |

| 66 | +prof | 让VCS在仿真过程中生成一个vcs.prof文件,记录设计中最耗CPU时间的module、层次和verilog结构 |

| 67 | +race | 让VCS在仿真过程中生成一个race.out文件,记录设计中所有的竞争冒险 |

| 68 | +radincr | 增量编译时使能Radiant技术 |

| 69 | +sdf_nocheck_celltype | SDF反标时不检查SDF文件中的CELLTYPE的一致性 |

| 70 | +sdfverbose | 显示SDF反标时的详细告警和错误信息 |

| 71 | +v2k | 支持Verilog-2001标准 |

| 72 | +vc[+abstract][+allhdrs][+list] | 使用DirectC接口时,使能verilog直接调用C/C++函数 |

| 73 | +vcs+flush+log | 加速编译仿真时log文件缓存的刷新频率 |

| 74 | +vcs+flush+all | +vcs+flush+log,+vcs+flush+dump和+vcs+flush+fopen的集合 |

| 75 | +vcs+initmem+0|1|x|z | 初始化设计中所有存储器的值 |

| 76 | +vcs+initreg+0|1|x|z | 初始化设计中所有寄存器的值 |

| 77 | +vcs+lic+wait | 一直等待license |

| 78 | +vpi | 使能VPI |

| 79 | +warn=[no]ID|none|all,... | 使能或关闭告警信息 |

| 編號 | 选项 | 说明 |

| 1 | -assert dumpoff | enable_diag | filter_past | 定义SystemVerilog断言(SVA)dumpoff:禁止将SVA信息DUMP到VPD中enable_diag:使能SVA结果报告由运行选项进一步控制filter_past:忽略$past中的子序列 |

| 2 | -cm <options> | 指定覆盖率的类型,包括:line(行覆盖)、cond(条件覆盖)、fsm(状态机覆盖)、tgl(翻转率覆盖)、path(路径覆盖)、branch(分支覆盖)和assert(断言覆盖)。如果包括两种或以上的覆盖率类型,可用“+”,如-cm line+cond+fsm+tgl |

| 3 | -cm_assert_hier <filename> | 将SVA覆盖率统计限定在文件列表中指定的module层次。 |

| 4 | -cm_cond <arguments> | 进一步细化条件覆盖率的统计方式,包括:basic,std,full,allops,event,anywidth,for,tf,sop等选项。 |

| 5 | -cm_count | 在统计是否覆盖的基础上,进一步统计覆盖的次数 |

| 6 | -cm_dir <directory_path_name> | 指定覆盖率统计结果的存放路径,默认是simv.cm |

| 7 | -cm_hier <filename> | 指定覆盖率统计的范围,范围在文件中定义,可以指定module名、层次名和源文件等。 |

| 8 | -cm_log <filename> | 指定仿真过程中记录覆盖率的log文件名 |

| 9 | -cm_name <filename> | 指定保存覆盖率结果的文本文件的名称 |

| 10 | -cm obc | 使能可观察(observed)覆盖率的编译。传统的覆盖率跟功能的正确性毫无关联,可观察覆盖率通过设置观察点,一定程度上将代码行覆盖率与功能正确性关联起来。 |

| 11 | -comp64 | 在64-bit模式下对设计进行编译,并生成32-bit格式的可执行文件用于32-bit模式仿真 |

| 12 | -debug 或 -debug_all | 使能UCLI命令行 |

| 13 | -e <new_name_for_main> | 指定PLI应用时main()程序的名称 |

| 14 | -f <filename> | 指定文件列表的文件名,文件中可包括源代码文件的路径和名称,也可以包括编译选项参数 |

| 15 | -file filename | 类似于-f,但文件内容更灵活,可以包含PLI选项和对象文件,可以使用转义字符等 |

| 16 | -full64 | 在64-bit模式下编译,生成64-bit模式仿真的可执行文件 |

| 17 | -h or -help | 列举常用的编译选项和运行选项的参数 |

| 18 | -I | 交互模式的编译,让VCS自动包括+cli,-P virsims.tab选项,并支持VirSim后处理模式下生成VCD+文件。 |

| 19 | -ID | 显示及其的hostid或dongle ID |

| 20 | -ignore <keyword_argument> | 屏蔽SV中unique/priority型的if或case语句的告警信息,参数包括:unique_checks、priority_checks、all。 |

| 21 | -j<number_of_processes> | 设定并行编译的进程数,“j”后面没有空格 |

| 22 | -l <filename> | 指定记录VCS编译和运行信息的log文件名 |

| 23 | -line | 使能VriSim中的单步运行 |

| 24 | -lmc-swift | 使能LMC SWIFT接口 |

| 25 | -Mdir=<directory> | 指定一个目录让VCS存储编译产生的文件,默认是csrc |

| 26 | -Mlib=<directory> | 指定一个目录让VCS搜索某个模块是否需要重新编译。与-Mdir配合,可以实现不同模块的增量编译。 |

| 27 | -Mmakeprogram=<program> | 指定用于make对象的程序,默认是make |

| 28 | -Mupdate[=0] | 默认情况下,VCS编译时会覆盖上次编译生成的makefile。如果想保留上次的makefile,使用-Mupdate=0;如果不带=0,则进行增量编译,并覆盖上次的makefile。 |

| 29 | -noIncrComp | 关闭增量编译 |

| 30 | -notice | 显示详细的诊断信息 |

| 31 | -ntb | 使能ntb(Native TestBench),支持OpenVera验证平台语言结构。 |

| 32 | -o <name> | 指定编译生成的可执行文件的名称,默认是simv |

| 33 | -timescale=<time_unit>/<time_precision> | 源代码文件中有的包括`timescale编译指令,有的不包括,如果在VCS命令行中,不包括`timescale的源代码文件在最前面,VCS会停止编译。使用-timescale选项为这些在前面且又没有`timescale的源文件指定timescale |

| 34 | -override_timescale=<time_unit>/<time_precision> | 让源文件统一使用指定的timescale |

| 35 | -P <pli.tab> | 指定PLI表文件 |

| 36 | -pvalues+<parameter_name>=<value> | 改变指定参数的值 |

| 37 | -parameters <filename> | 通过文件的方式改变参数的值,参数的路径和改变的值均在文件中定义 |

| 38 | -q | 安静模式,屏蔽VCS的编译信息 |

| 39 | -R | 在编译之后立即执行产生的可执行文件 |

| 40 | -s | 刚开始仿真时即停止,一般与-R和+cli配合使用 |

| 41 | -V | 使能verbose模式 |

| 42 | -v <filename> | 指定verilog库文件 |

| 43 | -y <dir_pathname> | 指定verilog库路径 |

| 44 | +libext+<extension> | 让VCS在verilog库路径下搜索指定的扩展名文件,与-y配合 |

| 45 | -vera | 指定标准的Vera PLI表文件和对象库 |

| 46 | +acc+1|2|3|4 | 使能PLI中的ACC(PLI 1.0的一种方式) |

| 47 | +cli+[<module_name>=]1|2|3|4 | 使能CLI调试功能 |

| 48 | +autoprotect[<file_suffix>] | 生成一个加密的源文件 |

| 49 | +protect[<file_suffix>] | 生成一个加密的源文件,只加密`protect/`endprotect部分 |

| 50 | +putprotect+<target_dir> | 指定加密文件存放的目录 |

| 51 | +csdf+precompile | 在VCS编译源代码时预先SDF文件 |

| 52 | +define+<macro_name>=<value> | 定义一个文本宏,与源文件中的`ifdef配合 |

| 53 | +error+<n> | 将编译时运行的NTB错误增加到N |

| 54 | +incdir+<directory> | 指定VCS搜索`include指令使用的包含文件的目录,可以用“+”定义多个目录。 |

| 55 | +maxdelays | 使用SDF文件中的max值 |

| 56 | +mindelays | 使用SDF文件中的min值 |

| 57 | +typdelays | 使用SDF文件中的typ值 |

| 58 | +nbaopt | 删除非阻塞赋值语句中的延时 |

| 59 | +neg_tchk | 使能时序检查中的负延时 |

| 60 | +nospecify | 屏蔽specify块中的路径延时和时序检查 |

| 61 | +notimingcheck | 屏蔽specify块中的时序检查 |

| 62 | +nowarnTFMPC | 屏蔽编译时的“Too few module port connections”告警信息 |

| 63 | +no_notifier | 屏蔽一些时序检查系统任务中定义的notifier寄存器的翻转(toggling),但不影响时序violation的报告 |

| 64 | +no_tchk_msg | 屏蔽时序检查的告警信息,但不关闭时序检查时notifier寄存器的翻转(toggling) |

| 65 | +optconfigfile+<filename> | 指定Radiant技术和二态仿真用到的配置文件名 |

| 66 | +prof | 让VCS在仿真过程中生成一个vcs.prof文件,记录设计中最耗CPU时间的module、层次和verilog结构 |

| 67 | +race | 让VCS在仿真过程中生成一个race.out文件,记录设计中所有的竞争冒险 |

| 68 | +radincr | 增量编译时使能Radiant技术 |

| 69 | +sdf_nocheck_celltype | SDF反标时不检查SDF文件中的CELLTYPE的一致性 |

| 70 | +sdfverbose | 显示SDF反标时的详细告警和错误信息 |

| 71 | +v2k | 支持Verilog-2001标准 |

| 72 | +vc[+abstract][+allhdrs][+list] | 使用DirectC接口时,使能verilog直接调用C/C++函数 |

| 73 | +vcs+flush+log | 加速编译仿真时log文件缓存的刷新频率 |

| 74 | +vcs+flush+all | +vcs+flush+log,+vcs+flush+dump和+vcs+flush+fopen的集合 |

| 75 | +vcs+initmem+0|1|x|z | 初始化设计中所有存储器的值 |

| 76 | +vcs+initreg+0|1|x|z | 初始化设计中所有寄存器的值 |

| 77 | +vcs+lic+wait | 一直等待license |

| 78 | +vpi | 使能VPI |

| 79 | +warn=[no]ID|none|all,... | 使能或关闭告警信息 |

| 編號 | 选项 | 说明 |

| 1 | -assert dumpoff | enable_diag | filter_past | 定义SystemVerilog断言(SVA)dumpoff:禁止将SVA信息DUMP到VPD中enable_diag:使能SVA结果报告由运行选项进一步控制filter_past:忽略$past中的子序列 |

| 2 | -cm <options> | 指定覆盖率的类型,包括:line(行覆盖)、cond(条件覆盖)、fsm(状态机覆盖)、tgl(翻转率覆盖)、path(路径覆盖)、branch(分支覆盖)和assert(断言覆盖)。如果包括两种或以上的覆盖率类型,可用“+”,如-cm line+cond+fsm+tgl |

| 3 | -cm_assert_hier <filename> | 将SVA覆盖率统计限定在文件列表中指定的module层次。 |

| 4 | -cm_cond <arguments> | 进一步细化条件覆盖率的统计方式,包括:basic,std,full,allops,event,anywidth,for,tf,sop等选项。 |

| 5 | -cm_count | 在统计是否覆盖的基础上,进一步统计覆盖的次数 |

| 6 | -cm_dir <directory_path_name> | 指定覆盖率统计结果的存放路径,默认是simv.cm |

| 7 | -cm_hier <filename> | 指定覆盖率统计的范围,范围在文件中定义,可以指定module名、层次名和源文件等。 |

| 8 | -cm_log <filename> | 指定仿真过程中记录覆盖率的log文件名 |

| 9 | -cm_name <filename> | 指定保存覆盖率结果的文本文件的名称 |

| 10 | -cm obc | 使能可观察(observed)覆盖率的编译。传统的覆盖率跟功能的正确性毫无关联,可观察覆盖率通过设置观察点,一定程度上将代码行覆盖率与功能正确性关联起来。 |

| 11 | -comp64 | 在64-bit模式下对设计进行编译,并生成32-bit格式的可执行文件用于32-bit模式仿真 |

| 12 | -debug 或 -debug_all | 使能UCLI命令行 |

| 13 | -e <new_name_for_main> | 指定PLI应用时main()程序的名称 |

| 14 | -f <filename> | 指定文件列表的文件名,文件中可包括源代码文件的路径和名称,也可以包括编译选项参数 |

| 15 | -file filename | 类似于-f,但文件内容更灵活,可以包含PLI选项和对象文件,可以使用转义字符等 |

| 16 | -full64 | 在64-bit模式下编译,生成64-bit模式仿真的可执行文件 |

| 17 | -h or -help | 列举常用的编译选项和运行选项的参数 |

| 18 | -I | 交互模式的编译,让VCS自动包括+cli,-P virsims.tab选项,并支持VirSim后处理模式下生成VCD+文件。 |

| 19 | -ID | 显示及其的hostid或dongle ID |

| 20 | -ignore <keyword_argument> | 屏蔽SV中unique/priority型的if或case语句的告警信息,参数包括:unique_checks、priority_checks、all。 |

| 21 | -j<number_of_processes> | 设定并行编译的进程数,“j”后面没有空格 |

| 22 | -l <filename> | 指定记录VCS编译和运行信息的log文件名 |

| 23 | -line | 使能VriSim中的单步运行 |

| 24 | -lmc-swift | 使能LMC SWIFT接口 |

| 25 | -Mdir=<directory> | 指定一个目录让VCS存储编译产生的文件,默认是csrc |

| 26 | -Mlib=<directory> | 指定一个目录让VCS搜索某个模块是否需要重新编译。与-Mdir配合,可以实现不同模块的增量编译。 |

| 27 | -Mmakeprogram=<program> | 指定用于make对象的程序,默认是make |

| 28 | -Mupdate[=0] | 默认情况下,VCS编译时会覆盖上次编译生成的makefile。如果想保留上次的makefile,使用-Mupdate=0;如果不带=0,则进行增量编译,并覆盖上次的makefile。 |

| 29 | -noIncrComp | 关闭增量编译 |

| 30 | -notice | 显示详细的诊断信息 |

| 31 | -ntb | 使能ntb(Native TestBench),支持OpenVera验证平台语言结构。 |

| 32 | -o <name> | 指定编译生成的可执行文件的名称,默认是simv |

| 33 | -timescale=<time_unit>/<time_precision> | 源代码文件中有的包括`timescale编译指令,有的不包括,如果在VCS命令行中,不包括`timescale的源代码文件在最前面,VCS会停止编译。使用-timescale选项为这些在前面且又没有`timescale的源文件指定timescale |

| 34 | -override_timescale=<time_unit>/<time_precision> | 让源文件统一使用指定的timescale |

| 35 | -P <pli.tab> | 指定PLI表文件 |

| 36 | -pvalues+<parameter_name>=<value> | 改变指定参数的值 |

| 37 | -parameters <filename> | 通过文件的方式改变参数的值,参数的路径和改变的值均在文件中定义 |

| 38 | -q | 安静模式,屏蔽VCS的编译信息 |

| 39 | -R | 在编译之后立即执行产生的可执行文件 |

| 40 | -s | 刚开始仿真时即停止,一般与-R和+cli配合使用 |

| 41 | -V | 使能verbose模式 |

| 42 | -v <filename> | 指定verilog库文件 |

| 43 | -y <dir_pathname> | 指定verilog库路径 |

| 44 | +libext+<extension> | 让VCS在verilog库路径下搜索指定的扩展名文件,与-y配合 |

| 45 | -vera | 指定标准的Vera PLI表文件和对象库 |

| 46 | +acc+1|2|3|4 | 使能PLI中的ACC(PLI 1.0的一种方式) |

| 47 | +cli+[<module_name>=]1|2|3|4 | 使能CLI调试功能 |

| 48 | +autoprotect[<file_suffix>] | 生成一个加密的源文件 |

| 49 | +protect[<file_suffix>] | 生成一个加密的源文件,只加密`protect/`endprotect部分 |

| 50 | +putprotect+<target_dir> | 指定加密文件存放的目录 |

| 51 | +csdf+precompile | 在VCS编译源代码时预先SDF文件 |

| 52 | +define+<macro_name>=<value> | 定义一个文本宏,与源文件中的`ifdef配合 |

| 53 | +error+<n> | 将编译时运行的NTB错误增加到N |

| 54 | +incdir+<directory> | 指定VCS搜索`include指令使用的包含文件的目录,可以用“+”定义多个目录。 |

| 55 | +maxdelays | 使用SDF文件中的max值 |

| 56 | +mindelays | 使用SDF文件中的min值 |

| 57 | +typdelays | 使用SDF文件中的typ值 |

| 58 | +nbaopt | 删除非阻塞赋值语句中的延时 |

| 59 | +neg_tchk | 使能时序检查中的负延时 |

| 60 | +nospecify | 屏蔽specify块中的路径延时和时序检查 |

| 61 | +notimingcheck | 屏蔽specify块中的时序检查 |

| 62 | +nowarnTFMPC | 屏蔽编译时的“Too few module port connections”告警信息 |

| 63 | +no_notifier | 屏蔽一些时序检查系统任务中定义的notifier寄存器的翻转(toggling),但不影响时序violation的报告 |

| 64 | +no_tchk_msg | 屏蔽时序检查的告警信息,但不关闭时序检查时notifier寄存器的翻转(toggling) |

| 65 | +optconfigfile+<filename> | 指定Radiant技术和二态仿真用到的配置文件名 |

| 66 | +prof | 让VCS在仿真过程中生成一个vcs.prof文件,记录设计中最耗CPU时间的module、层次和verilog结构 |

| 67 | +race | 让VCS在仿真过程中生成一个race.out文件,记录设计中所有的竞争冒险 |

| 68 | +radincr | 增量编译时使能Radiant技术 |

| 69 | +sdf_nocheck_celltype | SDF反标时不检查SDF文件中的CELLTYPE的一致性 |

| 70 | +sdfverbose | 显示SDF反标时的详细告警和错误信息 |

| 71 | +v2k | 支持Verilog-2001标准 |

| 72 | +vc[+abstract][+allhdrs][+list] | 使用DirectC接口时,使能verilog直接调用C/C++函数 |

| 73 | +vcs+flush+log | 加速编译仿真时log文件缓存的刷新频率 |

| 74 | +vcs+flush+all | +vcs+flush+log,+vcs+flush+dump和+vcs+flush+fopen的集合 |

| 75 | +vcs+initmem+0|1|x|z | 初始化设计中所有存储器的值 |

| 76 | +vcs+initreg+0|1|x|z | 初始化设计中所有寄存器的值 |

| 77 | +vcs+lic+wait | 一直等待license |

| 78 | +vpi | 使能VPI |

| 79 | +warn=[no]ID|none|all,... | 使能或关闭告警信息 |

| 編號 | 选项 | 说明 |

| 1 | -assert dumpoff | enable_diag | filter_past | 定义SystemVerilog断言(SVA)dumpoff:禁止将SVA信息DUMP到VPD中enable_diag:使能SVA结果报告由运行选项进一步控制filter_past:忽略$past中的子序列 |

| 2 | -cm <options> | 指定覆盖率的类型,包括:line(行覆盖)、cond(条件覆盖)、fsm(状态机覆盖)、tgl(翻转率覆盖)、path(路径覆盖)、branch(分支覆盖)和assert(断言覆盖)。如果包括两种或以上的覆盖率类型,可用“+”,如-cm line+cond+fsm+tgl |

| 3 | -cm_assert_hier <filename> | 将SVA覆盖率统计限定在文件列表中指定的module层次。 |

| 4 | -cm_cond <arguments> | 进一步细化条件覆盖率的统计方式,包括:basic,std,full,allops,event,anywidth,for,tf,sop等选项。 |

| 5 | -cm_count | 在统计是否覆盖的基础上,进一步统计覆盖的次数 |

| 6 | -cm_dir <directory_path_name> | 指定覆盖率统计结果的存放路径,默认是simv.cm |

| 7 | -cm_hier <filename> | 指定覆盖率统计的范围,范围在文件中定义,可以指定module名、层次名和源文件等。 |

| 8 | -cm_log <filename> | 指定仿真过程中记录覆盖率的log文件名 |

| 9 | -cm_name <filename> | 指定保存覆盖率结果的文本文件的名称 |

| 10 | -cm obc | 使能可观察(observed)覆盖率的编译。传统的覆盖率跟功能的正确性毫无关联,可观察覆盖率通过设置观察点,一定程度上将代码行覆盖率与功能正确性关联起来。 |

| 11 | -comp64 | 在64-bit模式下对设计进行编译,并生成32-bit格式的可执行文件用于32-bit模式仿真 |

| 12 | -debug 或 -debug_all | 使能UCLI命令行 |

| 13 | -e <new_name_for_main> | 指定PLI应用时main()程序的名称 |

| 14 | -f <filename> | 指定文件列表的文件名,文件中可包括源代码文件的路径和名称,也可以包括编译选项参数 |

| 15 | -file filename | 类似于-f,但文件内容更灵活,可以包含PLI选项和对象文件,可以使用转义字符等 |

| 16 | -full64 | 在64-bit模式下编译,生成64-bit模式仿真的可执行文件 |

| 17 | -h or -help | 列举常用的编译选项和运行选项的参数 |

| 18 | -I | 交互模式的编译,让VCS自动包括+cli,-P virsims.tab选项,并支持VirSim后处理模式下生成VCD+文件。 |

| 19 | -ID | 显示及其的hostid或dongle ID |

| 20 | -ignore <keyword_argument> | 屏蔽SV中unique/priority型的if或case语句的告警信息,参数包括:unique_checks、priority_checks、all。 |

| 21 | -j<number_of_processes> | 设定并行编译的进程数,“j”后面没有空格 |

| 22 | -l <filename> | 指定记录VCS编译和运行信息的log文件名 |

| 23 | -line | 使能VriSim中的单步运行 |

| 24 | -lmc-swift | 使能LMC SWIFT接口 |

| 25 | -Mdir=<directory> | 指定一个目录让VCS存储编译产生的文件,默认是csrc |

| 26 | -Mlib=<directory> | 指定一个目录让VCS搜索某个模块是否需要重新编译。与-Mdir配合,可以实现不同模块的增量编译。 |

| 27 | -Mmakeprogram=<program> | 指定用于make对象的程序,默认是make |

| 28 | -Mupdate[=0] | 默认情况下,VCS编译时会覆盖上次编译生成的makefile。如果想保留上次的makefile,使用-Mupdate=0;如果不带=0,则进行增量编译,并覆盖上次的makefile。 |

| 29 | -noIncrComp | 关闭增量编译 |

| 30 | -notice | 显示详细的诊断信息 |

| 31 | -ntb | 使能ntb(Native TestBench),支持OpenVera验证平台语言结构。 |

| 32 | -o <name> | 指定编译生成的可执行文件的名称,默认是simv |

| 33 | -timescale=<time_unit>/<time_precision> | 源代码文件中有的包括`timescale编译指令,有的不包括,如果在VCS命令行中,不包括`timescale的源代码文件在最前面,VCS会停止编译。使用-timescale选项为这些在前面且又没有`timescale的源文件指定timescale |

| 34 | -override_timescale=<time_unit>/<time_precision> | 让源文件统一使用指定的timescale |

| 35 | -P <pli.tab> | 指定PLI表文件 |

| 36 | -pvalues+<parameter_name>=<value> | 改变指定参数的值 |

| 37 | -parameters <filename> | 通过文件的方式改变参数的值,参数的路径和改变的值均在文件中定义 |

| 38 | -q | 安静模式,屏蔽VCS的编译信息 |

| 39 | -R | 在编译之后立即执行产生的可执行文件 |

| 40 | -s | 刚开始仿真时即停止,一般与-R和+cli配合使用 |

| 41 | -V | 使能verbose模式 |

| 42 | -v <filename> | 指定verilog库文件 |

| 43 | -y <dir_pathname> | 指定verilog库路径 |

| 44 | +libext+<extension> | 让VCS在verilog库路径下搜索指定的扩展名文件,与-y配合 |

| 45 | -vera | 指定标准的Vera PLI表文件和对象库 |

| 46 | +acc+1|2|3|4 | 使能PLI中的ACC(PLI 1.0的一种方式) |

| 47 | +cli+[<module_name>=]1|2|3|4 | 使能CLI调试功能 |

| 48 | +autoprotect[<file_suffix>] | 生成一个加密的源文件 |

| 49 | +protect[<file_suffix>] | 生成一个加密的源文件,只加密`protect/`endprotect部分 |

| 50 | +putprotect+<target_dir> | 指定加密文件存放的目录 |

| 51 | +csdf+precompile | 在VCS编译源代码时预先SDF文件 |

| 52 | +define+<macro_name>=<value> | 定义一个文本宏,与源文件中的`ifdef配合 |

| 53 | +error+<n> | 将编译时运行的NTB错误增加到N |

| 54 | +incdir+<directory> | 指定VCS搜索`include指令使用的包含文件的目录,可以用“+”定义多个目录。 |

| 55 | +maxdelays | 使用SDF文件中的max值 |

| 56 | +mindelays | 使用SDF文件中的min值 |

| 57 | +typdelays | 使用SDF文件中的typ值 |

| 58 | +nbaopt | 删除非阻塞赋值语句中的延时 |

| 59 | +neg_tchk | 使能时序检查中的负延时 |

| 60 | +nospecify | 屏蔽specify块中的路径延时和时序检查 |

| 61 | +notimingcheck | 屏蔽specify块中的时序检查 |

| 62 | +nowarnTFMPC | 屏蔽编译时的“Too few module port connections”告警信息 |

| 63 | +no_notifier | 屏蔽一些时序检查系统任务中定义的notifier寄存器的翻转(toggling),但不影响时序violation的报告 |

| 64 | +no_tchk_msg | 屏蔽时序检查的告警信息,但不关闭时序检查时notifier寄存器的翻转(toggling) |

| 65 | +optconfigfile+<filename> | 指定Radiant技术和二态仿真用到的配置文件名 |

| 66 | +prof | 让VCS在仿真过程中生成一个vcs.prof文件,记录设计中最耗CPU时间的module、层次和verilog结构 |

| 67 | +race | 让VCS在仿真过程中生成一个race.out文件,记录设计中所有的竞争冒险 |

| 68 | +radincr | 增量编译时使能Radiant技术 |

| 69 | +sdf_nocheck_celltype | SDF反标时不检查SDF文件中的CELLTYPE的一致性 |

| 70 | +sdfverbose | 显示SDF反标时的详细告警和错误信息 |

| 71 | +v2k | 支持Verilog-2001标准 |

| 72 | +vc[+abstract][+allhdrs][+list] | 使用DirectC接口时,使能verilog直接调用C/C++函数 |

| 73 | +vcs+flush+log | 加速编译仿真时log文件缓存的刷新频率 |

| 74 | +vcs+flush+all | +vcs+flush+log,+vcs+flush+dump和+vcs+flush+fopen的集合 |

| 75 | +vcs+initmem+0|1|x|z | 初始化设计中所有存储器的值 |

| 76 | +vcs+initreg+0|1|x|z | 初始化设计中所有寄存器的值 |

| 77 | +vcs+lic+wait | 一直等待license |

| 78 | +vpi | 使能VPI |

| 79 | +warn=[no]ID|none|all,... | 使能或关闭告警信息 |

| 編號 | 选项 | 说明 |

| 1 | -assert dumpoff | enable_diag | filter_past | 定义SystemVerilog断言(SVA)dumpoff:禁止将SVA信息DUMP到VPD中enable_diag:使能SVA结果报告由运行选项进一步控制filter_past:忽略$past中的子序列 |

| 2 | -cm <options> | 指定覆盖率的类型,包括:line(行覆盖)、cond(条件覆盖)、fsm(状态机覆盖)、tgl(翻转率覆盖)、path(路径覆盖)、branch(分支覆盖)和assert(断言覆盖)。如果包括两种或以上的覆盖率类型,可用“+”,如-cm line+cond+fsm+tgl |

| 3 | -cm_assert_hier <filename> | 将SVA覆盖率统计限定在文件列表中指定的module层次。 |

| 4 | -cm_cond <arguments> | 进一步细化条件覆盖率的统计方式,包括:basic,std,full,allops,event,anywidth,for,tf,sop等选项。 |

| 5 | -cm_count | 在统计是否覆盖的基础上,进一步统计覆盖的次数 |

| 6 | -cm_dir <directory_path_name> | 指定覆盖率统计结果的存放路径,默认是simv.cm |

| 7 | -cm_hier <filename> | 指定覆盖率统计的范围,范围在文件中定义,可以指定module名、层次名和源文件等。 |

| 8 | -cm_log <filename> | 指定仿真过程中记录覆盖率的log文件名 |

| 9 | -cm_name <filename> | 指定保存覆盖率结果的文本文件的名称 |

| 10 | -cm obc | 使能可观察(observed)覆盖率的编译。传统的覆盖率跟功能的正确性毫无关联,可观察覆盖率通过设置观察点,一定程度上将代码行覆盖率与功能正确性关联起来。 |

| 11 | -comp64 | 在64-bit模式下对设计进行编译,并生成32-bit格式的可执行文件用于32-bit模式仿真 |

| 12 | -debug 或 -debug_all | 使能UCLI命令行 |

| 13 | -e <new_name_for_main> | 指定PLI应用时main()程序的名称 |

| 14 | -f <filename> | 指定文件列表的文件名,文件中可包括源代码文件的路径和名称,也可以包括编译选项参数 |

| 15 | -file filename | 类似于-f,但文件内容更灵活,可以包含PLI选项和对象文件,可以使用转义字符等 |

| 16 | -full64 | 在64-bit模式下编译,生成64-bit模式仿真的可执行文件 |

| 17 | -h or -help | 列举常用的编译选项和运行选项的参数 |

| 18 | -I | 交互模式的编译,让VCS自动包括+cli,-P virsims.tab选项,并支持VirSim后处理模式下生成VCD+文件。 |

| 19 | -ID | 显示及其的hostid或dongle ID |

| 20 | -ignore <keyword_argument> | 屏蔽SV中unique/priority型的if或case语句的告警信息,参数包括:unique_checks、priority_checks、all。 |

| 21 | -j<number_of_processes> | 设定并行编译的进程数,“j”后面没有空格 |

| 22 | -l <filename> | 指定记录VCS编译和运行信息的log文件名 |

| 23 | -line | 使能VriSim中的单步运行 |

| 24 | -lmc-swift | 使能LMC SWIFT接口 |

| 25 | -Mdir=<directory> | 指定一个目录让VCS存储编译产生的文件,默认是csrc |

| 26 | -Mlib=<directory> | 指定一个目录让VCS搜索某个模块是否需要重新编译。与-Mdir配合,可以实现不同模块的增量编译。 |

| 27 | -Mmakeprogram=<program> | 指定用于make对象的程序,默认是make |

| 28 | -Mupdate[=0] | 默认情况下,VCS编译时会覆盖上次编译生成的makefile。如果想保留上次的makefile,使用-Mupdate=0;如果不带=0,则进行增量编译,并覆盖上次的makefile。 |

| 29 | -noIncrComp | 关闭增量编译 |

| 30 | -notice | 显示详细的诊断信息 |

| 31 | -ntb | 使能ntb(Native TestBench),支持OpenVera验证平台语言结构。 |

| 32 | -o <name> | 指定编译生成的可执行文件的名称,默认是simv |

| 33 | -timescale=<time_unit>/<time_precision> | 源代码文件中有的包括`timescale编译指令,有的不包括,如果在VCS命令行中,不包括`timescale的源代码文件在最前面,VCS会停止编译。使用-timescale选项为这些在前面且又没有`timescale的源文件指定timescale |

| 34 | -override_timescale=<time_unit>/<time_precision> | 让源文件统一使用指定的timescale |

| 35 | -P <pli.tab> | 指定PLI表文件 |

| 36 | -pvalues+<parameter_name>=<value> | 改变指定参数的值 |

| 37 | -parameters <filename> | 通过文件的方式改变参数的值,参数的路径和改变的值均在文件中定义 |

| 38 | -q | 安静模式,屏蔽VCS的编译信息 |

| 39 | -R | 在编译之后立即执行产生的可执行文件 |

| 40 | -s | 刚开始仿真时即停止,一般与-R和+cli配合使用 |

| 41 | -V | 使能verbose模式 |

| 42 | -v <filename> | 指定verilog库文件 |

| 43 | -y <dir_pathname> | 指定verilog库路径 |

| 44 | +libext+<extension> | 让VCS在verilog库路径下搜索指定的扩展名文件,与-y配合 |

| 45 | -vera | 指定标准的Vera PLI表文件和对象库 |

| 46 | +acc+1|2|3|4 | 使能PLI中的ACC(PLI 1.0的一种方式) |

| 47 | +cli+[<module_name>=]1|2|3|4 | 使能CLI调试功能 |

| 48 | +autoprotect[<file_suffix>] | 生成一个加密的源文件 |

| 49 | +protect[<file_suffix>] | 生成一个加密的源文件,只加密`protect/`endprotect部分 |

| 50 | +putprotect+<target_dir> | 指定加密文件存放的目录 |

| 51 | +csdf+precompile | 在VCS编译源代码时预先SDF文件 |

| 52 | +define+<macro_name>=<value> | 定义一个文本宏,与源文件中的`ifdef配合 |

| 53 | +error+<n> | 将编译时运行的NTB错误增加到N |

| 54 | +incdir+<directory> | 指定VCS搜索`include指令使用的包含文件的目录,可以用“+”定义多个目录。 |

| 55 | +maxdelays | 使用SDF文件中的max值 |

| 56 | +mindelays | 使用SDF文件中的min值 |

| 57 | +typdelays | 使用SDF文件中的typ值 |

| 58 | +nbaopt | 删除非阻塞赋值语句中的延时 |

| 59 | +neg_tchk | 使能时序检查中的负延时 |

| 60 | +nospecify | 屏蔽specify块中的路径延时和时序检查 |

| 61 | +notimingcheck | 屏蔽specify块中的时序检查 |

| 62 | +nowarnTFMPC | 屏蔽编译时的“Too few module port connections”告警信息 |

| 63 | +no_notifier | 屏蔽一些时序检查系统任务中定义的notifier寄存器的翻转(toggling),但不影响时序violation的报告 |

| 64 | +no_tchk_msg | 屏蔽时序检查的告警信息,但不关闭时序检查时notifier寄存器的翻转(toggling) |

| 65 | +optconfigfile+<filename> | 指定Radiant技术和二态仿真用到的配置文件名 |

| 66 | +prof | 让VCS在仿真过程中生成一个vcs.prof文件,记录设计中最耗CPU时间的module、层次和verilog结构 |

| 67 | +race | 让VCS在仿真过程中生成一个race.out文件,记录设计中所有的竞争冒险 |

| 68 | +radincr | 增量编译时使能Radiant技术 |

| 69 | +sdf_nocheck_celltype | SDF反标时不检查SDF文件中的CELLTYPE的一致性 |

| 70 | +sdfverbose | 显示SDF反标时的详细告警和错误信息 |

| 71 | +v2k | 支持Verilog-2001标准 |

| 72 | +vc[+abstract][+allhdrs][+list] | 使用DirectC接口时,使能verilog直接调用C/C++函数 |

| 73 | +vcs+flush+log | 加速编译仿真时log文件缓存的刷新频率 |

| 74 | +vcs+flush+all | +vcs+flush+log,+vcs+flush+dump和+vcs+flush+fopen的集合 |

| 75 | +vcs+initmem+0|1|x|z | 初始化设计中所有存储器的值 |

| 76 | +vcs+initreg+0|1|x|z | 初始化设计中所有寄存器的值 |

| 77 | +vcs+lic+wait | 一直等待license |

| 78 | +vpi | 使能VPI |

| 79 | +warn=[no]ID|none|all,... | 使能或关闭告警信息 |

VCS常用的运行选项

| 編號 | 选项 | 说明 |

| 1 | -a <filename> | 将仿真显示的log信息附件在指定文件尾部 |

| 2 | -E <program> | 执行指定的程序用来显示生成simv可执行文件时VCS使用的编译选项 |

| 3 | -i <filename> | 指定一个VCS执行仿真时包含CLI命令的文件,一般与-ucli配合 |

| 4 | -k <filename> | off | 指定一个文件,用来记录VCS仿真过程中的CLI和VirSim交互命令,默认是vcs.key,off选项是关闭记录。 |

| 5 | -sverilog | 支持SystemVerilog |

| 6 | -ucli | 使能UCLI命令 |

| 7 | -vcd <filename> | 指定VCD波形文件名,默认是verilog.dump,会被源代码文件中的$dumpfile覆盖 |

| 8 | +vcs+learn+pli | 追踪当前仿真的ACC选项,记录在pli_learn.tab文件中,下次仿真时可以用+applylearn来重新编译。 |

| 9 | +vcs+nostdout | 关闭所有$monitor和$display的文本输出,但依然会记录在-l的log文件中。 |

| 10 | +vera_load=<filename.vro> | 定义Vera对象文件 |

| 11 | +vera_mload=<filename> | 定义一个包括多个Vera对象文件的文本文件 |

VCS调试模式常用选项

| 編號 | 选项 | 说明 |

| 1 | -RI | 编译完成之后马上启动VirSim,进入交互模式 |

| 2 | -RIG | 不编译,启动VirSim使用已有的可执行文件,进入交互调试模式。 |

| 3 | +sim+<simv_name> | 指定使用的可执行文件名,与-RIG配合 |

| 4 | -RPP | 运行后处理(Post-Processing)模式:启动VirSim,使用VCD+文件 |

| 5 | -PP | 支持在源代码文件中调用$vcdpluson生成VPD文件 |

| 6 | +cfgfile+<filename> | 定义一个VCS使用的已建好的场景配置文件 |

| 7 | +vslogfile[+<filename>] | 保存一个VirSim命令的log文件,默认是VirSim.log |

参考: