2018-2019-1 20165314《信息安全系统设计基础》第五周学习总结

2018-2019-1 20165314《信息安全系统设计基础》第五周学习总结

- SRAM和DRAM都是易失的,只是两者结构不同,速度有差异,SRAM存取速度要快些。

- PROM只能被编程一次。

- 存储在ROM设备中的程序通常被称为固件。

- EEPROM不需要用紫外线照射,也不需取下,就可以用特定的电压,来抹除芯片上- 的信息,以便写入新的数据。

- 程序中循环语句具有良好的局部性

- LRU策略指的是替换策略的缓存会选择最后被访问时间距现在最远的块

- 缓存不命时,决定哪个块是牺牲块由替换策略来控制、

- 空缓存的不命中叫强制性不命中或冷不命中

- 根据携带信号不同,总线可分为数据总线、地址总线、控制总线

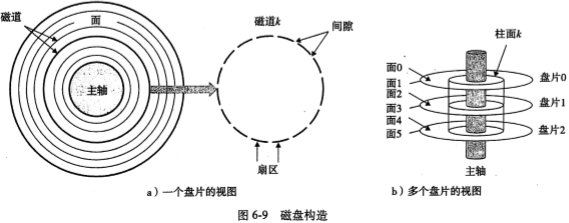

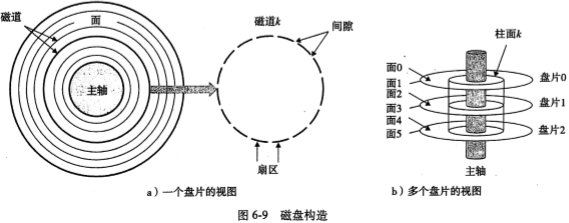

- 磁盘以扇区大小的块来读写数据

- 对磁盘扇区的访问时间包括三个部分中,传送时间最小。

- 读写头总处于同一柱面

- 通过使用两个时钟沿作为控制信号,对DRAM进行增强的是DDR SDRAM

- CPU通过内存映射I/O向I/O设备发命令,DMA传送不需要CPU的干涉,SSD是一种基于闪存或Flash的存储技术,逻辑磁盘块的逻辑块号可以翻译成一个(盘面,磁道,扇区 )三元组。

- 程序访问一个向量,步长越小或短,空间局部性越好

- 局部性有两种形式:空间局部性,时间局部性

- 硬件、OS,应用程序都会用到局部性原理

- 磁盘的读取时间为毫秒级

- 磁盘表面由磁道组成

- 每张磁盘有多个表面且虽然面积不同,但是数据位的数量一样

- 一个驱动器有三个盘片和六个面,每个表面上的磁道的编号都是一致的,那么柱面K就是6个磁道k的集合

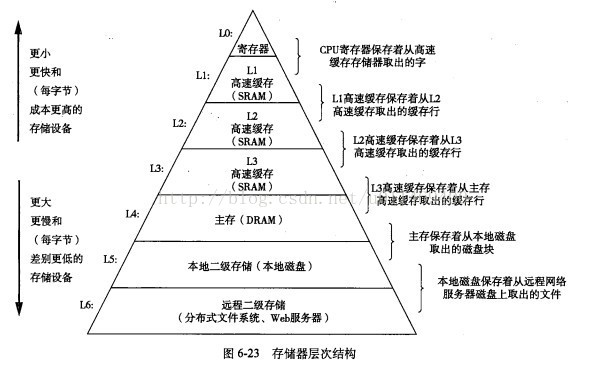

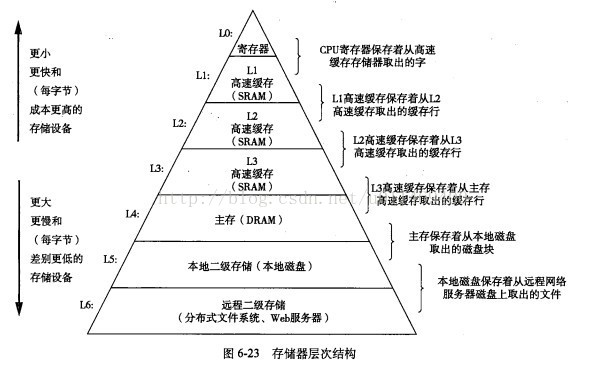

- 存储层次涉用不同容量,成本,访问时间的存储设备

- 存储层次设计基于局部性原理

- “存储山”是时间局部性和空间局部性的函数

- 程序具有良好的局部性表现在倾向于从存储器层次结构中的较高层次处访问数据

- SRAM、DRAM不是非易失性存储。SRAM将一个bit存在一个双稳态的存储单元中,而DRAM一般采用电容作为存储单元。DRAM每一个2ms要刷新1次避免数据丢失而SRAM是静态的不需要刷新。SDRAM在1个时钟周期内只传输1次数据,它是在时钟的上升期进行数据传输;而DDR内存则是1个时钟周期内传输两次次数据,它能够在时钟的上升期和降落期各传输1次数据,因此称为双倍速率同步动态随机存储器。DRAM一般采用电容作为存储单元;DRAM比SRAM快;DRAM需要重写刷新

- 高速缓存的容量可以用C=SEB来计算

- 直接映射高速缓存要:组选择、行匹配、字抽取

- 当程序访问大小为2的幂的数组时,直接映射高带缓存中常发生冲突不命中

原文地址:https://www.cnblogs.com/zhangshuai9345/p/9867702.html