7.1什么是STA环境

表现为时序约束

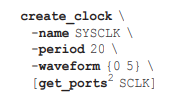

7.2时钟定义

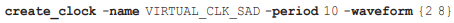

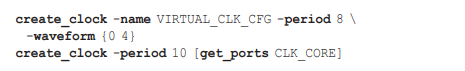

典型:

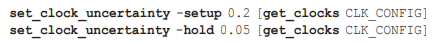

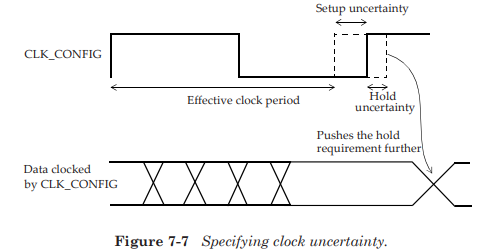

7.2.1clock uncertainty

约束:

建立时钟不确定性缩短了有效时钟周期,保持时间不确定性增加了require time,就是说需要保持的时间更长了

还有在时钟边界上的时钟不确定性 讲的不是很细 没图

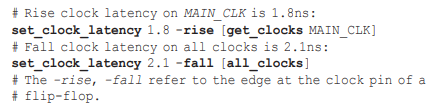

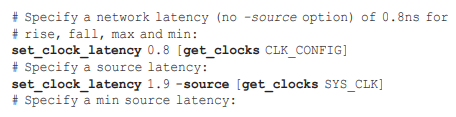

7.2.2clock latency

约束:

有两种时钟延迟:

network latency是指从时钟定义的点create_clock到触发器时钟引脚的延时

source latency也称为insertion delay是从时钟源到时钟定义点的延时

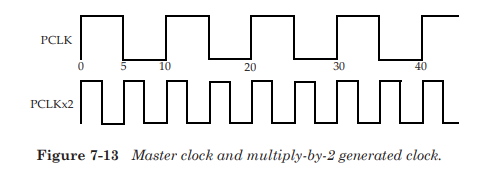

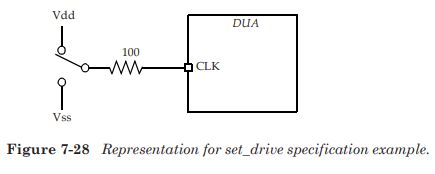

7.3衍生时钟

衍生时钟不需要额外的约束,source latency不必考虑在内

衍生时钟频率可以高于主时钟:

衍生时钟有很多种约束,具体遇到再看吧

7.4 约束输入路径

STA不能检查没有约束的路径

7.5 约束输出路径

7.6时序路径组

7.7外部属性建模

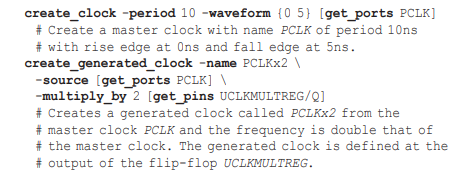

对于输入信号要指定slew 输出要指定负载

7.7.1 set_drive 设定的是输入端口的电阻值,如果设置为0认为驱动无限大

7.8设计规则检查

常用于STA设计检查的是max_transition和max_capacitance。

7.9虚拟时钟

之后可以对虚拟时钟指定IO约束

7.10提炼时序分析

set_case_annlysis为单元引脚或者输入端口指定一个常量

set_disable_timing打破时序弧

set_false_path设置不让sta分析的路径

set_multicycle_path指定需要超过一个时钟周期的路径

7.12路径分割

如果只想知道一段路径里面部分组合逻辑链的延时可以自行设定startpoint和endpoint