单bit跨时钟域传输 单bitCDC

快时钟 to 慢时钟

如果是电平信号传输直接用两级同步器

信号宽度问题:信号位宽有限的情况下,由于快时钟域下数据可能会多次改变,慢时钟可能来不及采样,导致数据丢失。

快时钟域的信号宽度必须是慢时钟域时钟周期的1.5倍以上,也就是持续3个时钟沿以上(上升下降沿都算),所以被称为3个时钟沿要求。

1倍宽度还是有可能不保证建立保持时间。

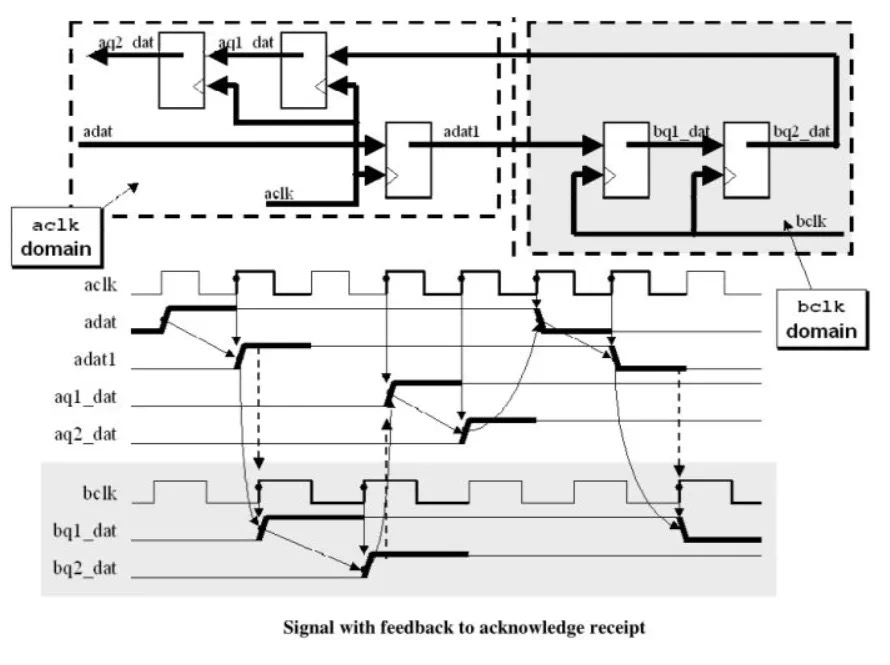

通常做法:通过握手的方式保证数据被采样到。发送一个使能信号,将它同步到新的时钟域,然后通过另一个同步器将同步信号作为确认信号传回发送时钟域。

adat是使能控制信号

优点:非常安全。缺点:在允许控制信号改变之前,两个方向上的同步信号可能会有相当大的延迟,也就是说在应答信号到来之前,是不允许源信号改变的。(adat和aq2_dat)

慢时钟 to 快时钟

两级信号同步器

注意:目标时钟频率必须是源时钟频率的1.5倍或者以上,才能算慢时钟到快时钟的CDC。

多bit跨时钟域传输

同步器的同步延时会不一样

为了避免多bit跨时钟域倾斜采样:

1.在可能的情况下,将多个跨时钟域传播位合并为1位跨时钟域信号

2.多周期路径法

3.使用格雷码

4.使用异步fifo

说明:

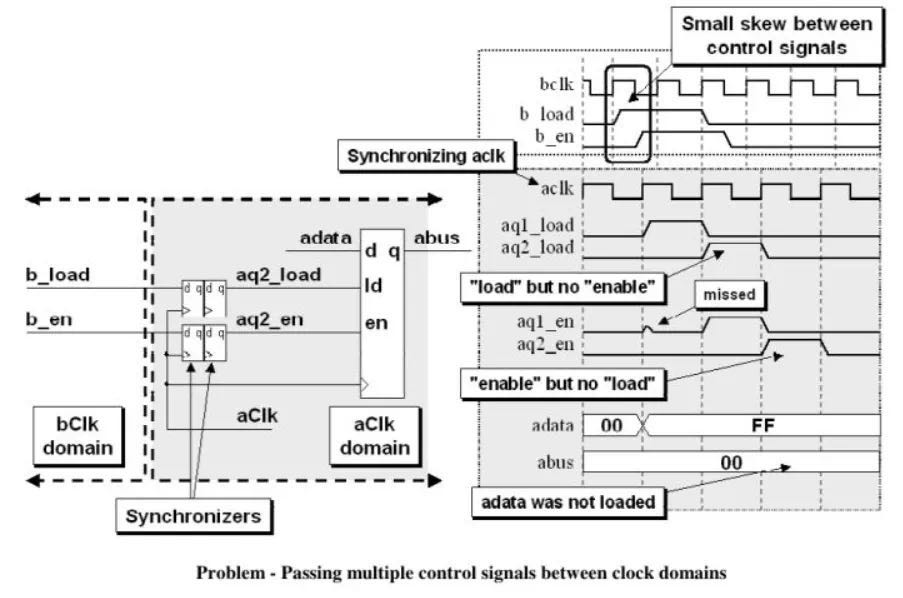

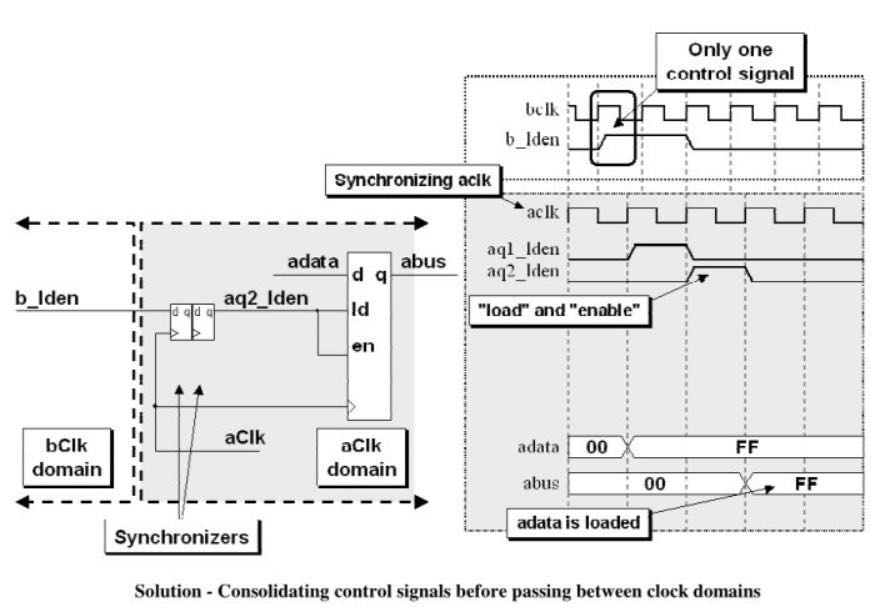

1.如下图所示,接收时钟域中的寄存器需要加载信号load和使能信号enable才能将数据值加载到寄存器中。如果负载和使能信号都是在同一个发送时钟边缘上驱动,那么控制信号的小偏差就有可能导致两个信号在接收时钟域同步到不同的时钟周期,如下图small skew between control signals中的信号由aclk采样,load信号被采样到的时候,enable信号没有被采样到。快时钟到慢时钟,慢时钟到快时钟。

在这种情况下,数据ff就不会被采样到寄存器中,见adata、abus。

解决方法:将b_load和b_en合并:b_len = b_load & b_en

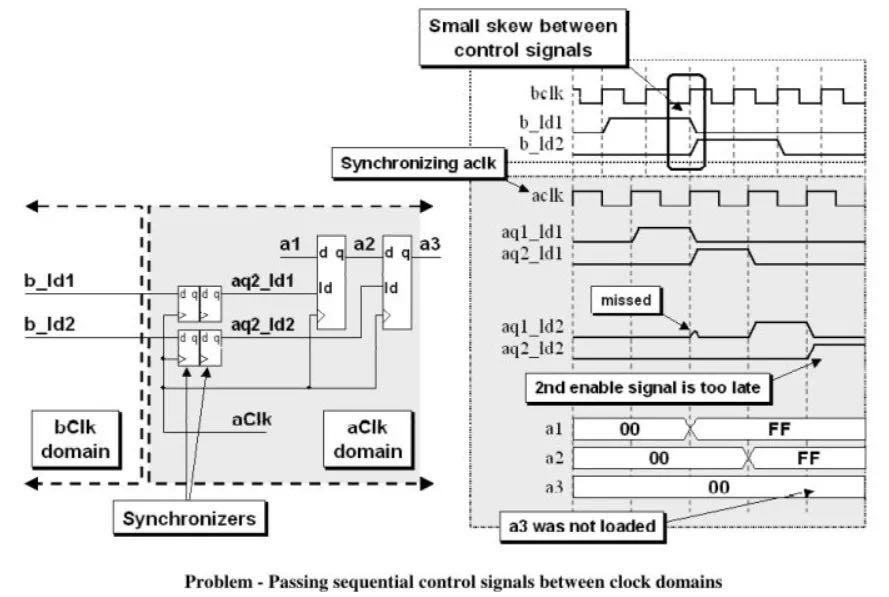

还要第2个例子,aq2_ld1 aq2_ld2控制流水线寄存器的使能输入,但是框框里圈出来的部分采样有问题,就不能保证两个使能信号的同步,missed那个地方本应该是一个周期的高电平。

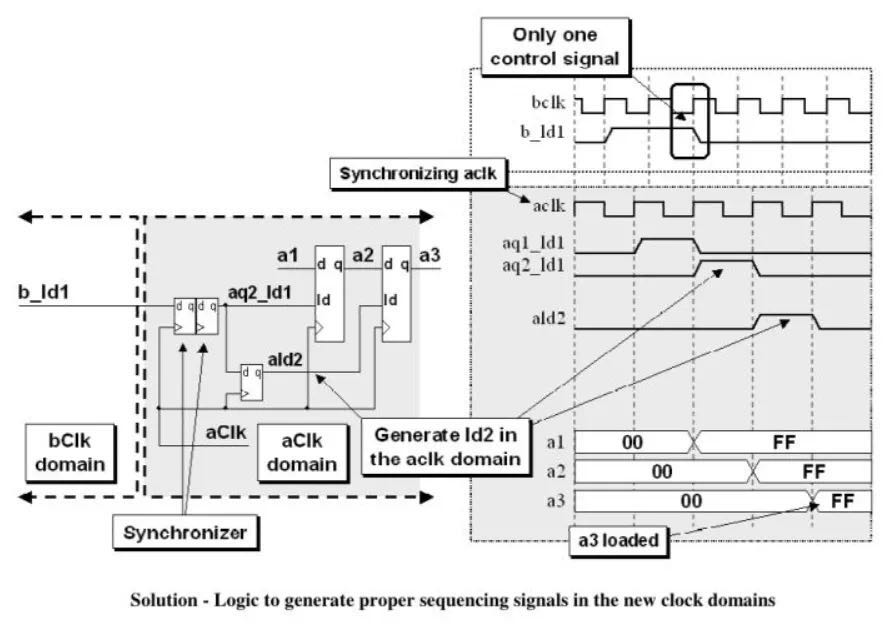

解决方法:只向接收时钟域发送一个控制信号b_ld1,在接收时钟域内加一个传递控制信号的寄存器ald2,生成第二个周期流水线使能信号。

这个图...为啥又给寄存器加了一个使能端en???不太懂,有上图就够了。

多周期路径 Muti-Cycle path MCP

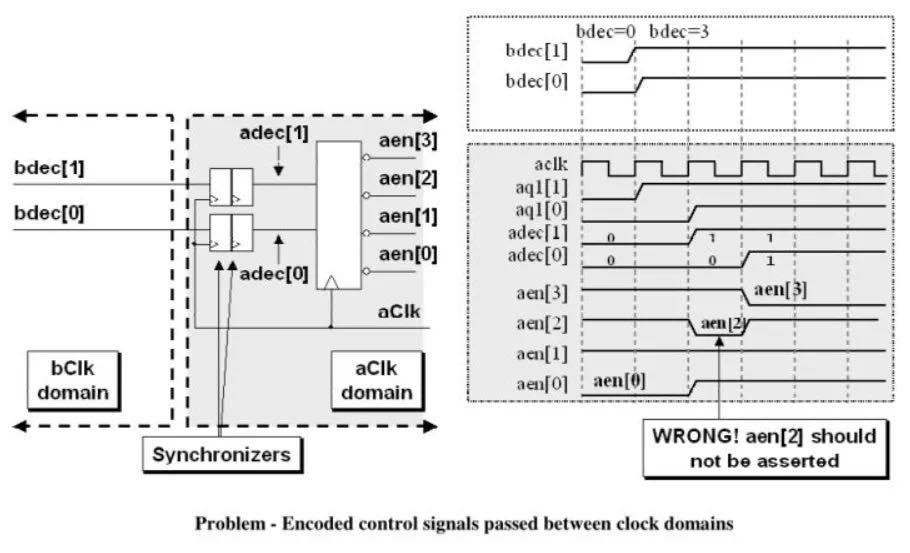

跨时钟域传播编码控制信号,如果这两个编码信号在采样时略有偏差(图中aq1[0]晚了一个时钟周期),则在接收时钟域中一个时钟周期内可能会产生错误解码输出。

多位数据问题可以用多周期路径法来解决。

不同步多位的数据,值同步一位的控制信号,通过握手保证控制信号能够正确传输,然后在目标时钟域通过控制信号来采样数据。

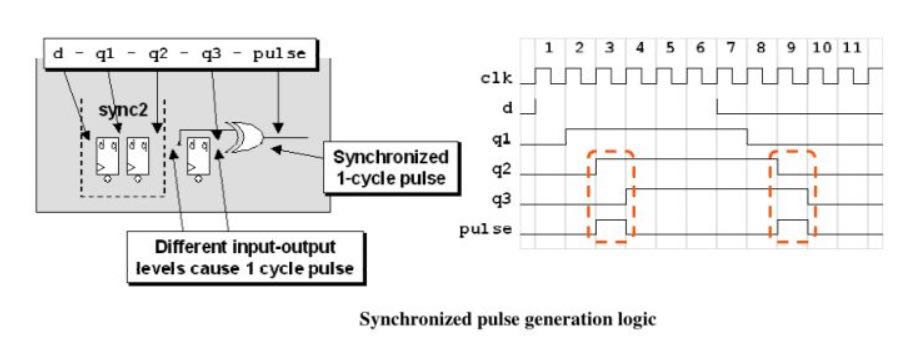

需要用到同步脉冲器。

带反馈的MCP、带应答反馈的MCP

格雷码

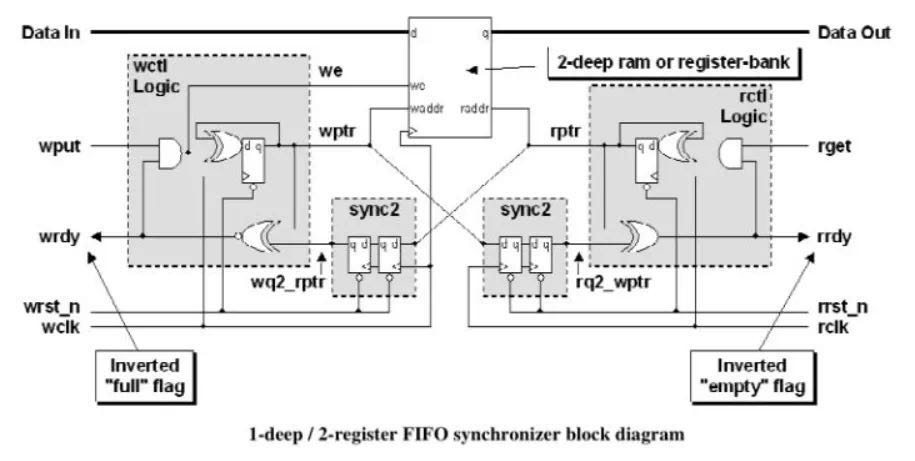

通过异步fifo进行多位信号跨时钟传递

特殊应用:深度为2的异步fifo,来进行多位信号跨时钟传播,2个寄存器搭建的异步FIFO,地址只需要1位,相比MCP方法,逻辑简单。

总结:

1bit:

慢时钟到快时钟:同步器

快时钟到慢时钟:多时钟周期路径,握手

多bit:

多个信号合成一个信号

异步fifo