GDSII是一种标准版图描述语言,采用二进制格式记录版图几何图形、拓扑关系、结构、层次以及信息,文件一般以.gds做后缀。

technology file 工艺技术文件,内容一般包括图形定义及显示信息、互连线工艺和通孔工艺信息。.tf

设计规则检查DRC 将版图中所有几何图形与设计规则规定的尺寸、间距进行比较,并将所有违反规则的地方通过EDA工具以醒目标识反标到版图中告诉设计者。

电路规则检查LVS 主要目的是验证版图与电路原理图的电路结构是否一致。

完整的工艺库里面的单元可以分为三类:标准单元、模块宏单元、输入输出单元IO pad cell。

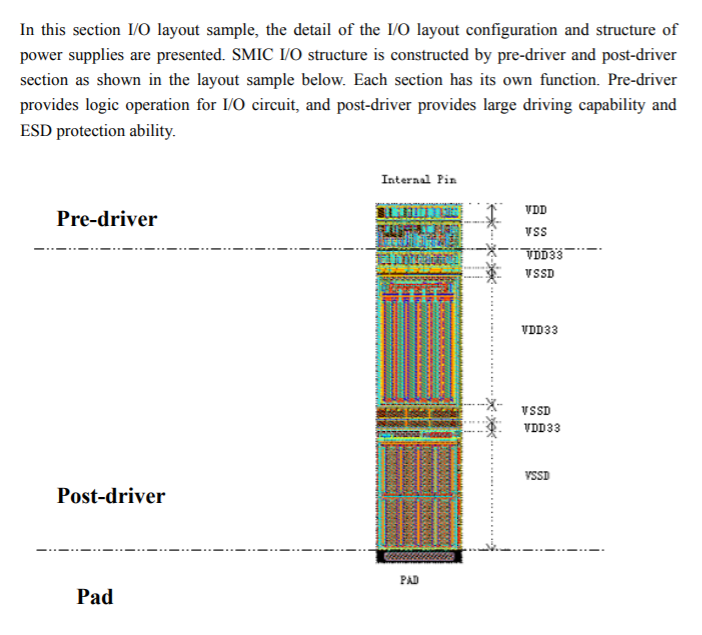

芯片与印刷电路板通信的结构电路统称为IO电路,作为芯片与外界通信的接口必须具有较大的驱动能力,抵御静电放电的能力以及足够的带宽和过电保护功能,种类包括:输入io、输出io、双向输入输出io、供电io、接地io。

io的组成大致可分为三部分:pad接口、信号缓冲电路、静电保护电路;下图是smic180工艺提供datasheet里描述的io pad。输入缓冲电路的主要作用是将外部电压转换为芯片内部信号电压,还可以过滤输入噪声。

特殊的标准单元:

填充单元、电压钳位单元、二极管单元、时钟缓冲单元、延时缓冲单元、阱连接单元、电压转换单元、隔离单元、开关单元

去耦单元,当电路中大量单元同时翻转时会导致充放电瞬间电流增大,使得电路动态供电电压下降或者地线电压升高,引起动态电压降IR-drop。为了避免动态电压降对电路性能的影响,通常在电源和地线之间放置由MOS管构成的电容,被称为去耦电容或去耦单元decap cell,它的作用是在瞬态电流增大、电压下降时向电路补充电流以保持电源和地线之间的电压稳定。

物理库交换格式LEF文件,c家是这样,s家可以转换为xxx,定义单元的物理信息。

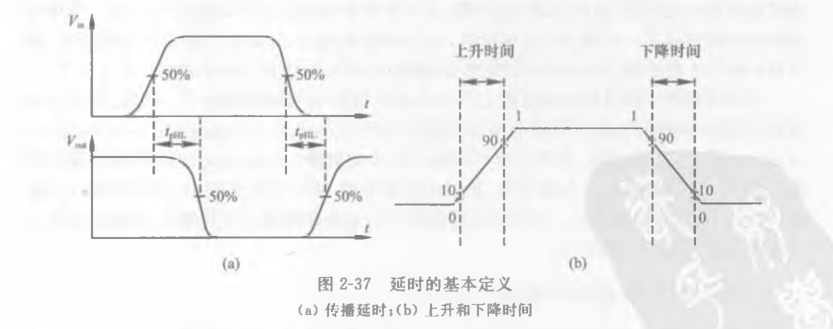

器件延时:

信号通过一个逻辑门所经历的时间,反映了门对输入信号变化响应的快慢,也称作传播延时。数集书上有计算公式。

在DC中,是采用非线性延时模型去估计的,参数有输入翻转延时(信号斜率)和输出负载(电容)。

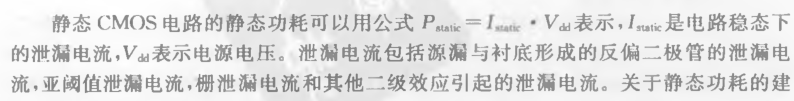

静态功耗:

动态功耗:翻转功耗

时序库lib、天线效应

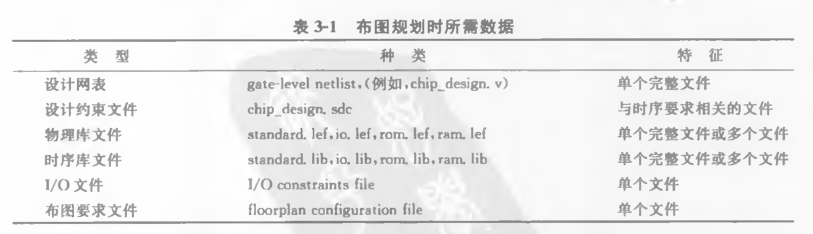

布图规划floorplan:布局包括对标准单元、io单元、block的规划,标准单元部分包括扫描链重组;

布图规划主要内容包含了对芯片大小die size、io、macro的规划,

需要的准备数据

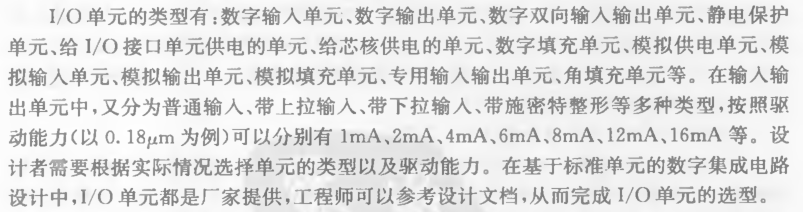

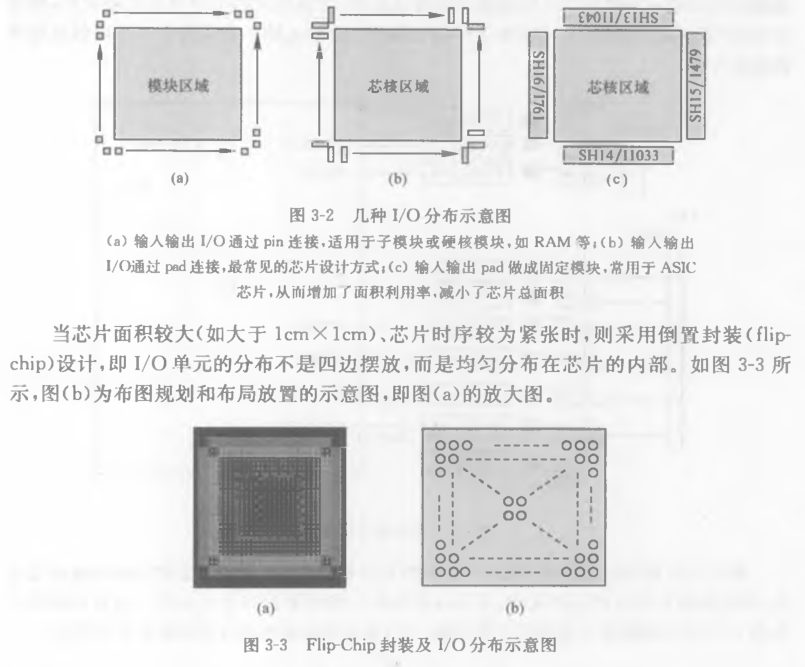

io单元的类型和布局

类型有:

布局:

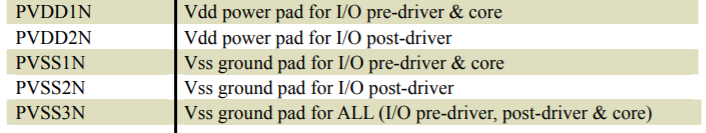

数字供电io单元分为两组,一组给核内的标准单元供电,一组给io单元供电。下面是smic180的io供电单元:

供电单元数量的确定:

供电单元位置的摆放:

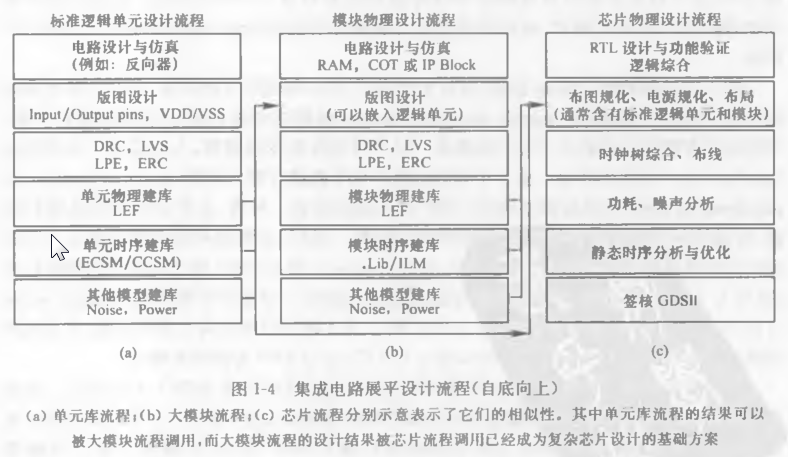

展平设计与层次化设计

展平式物理设计:

硅虚拟原型设计

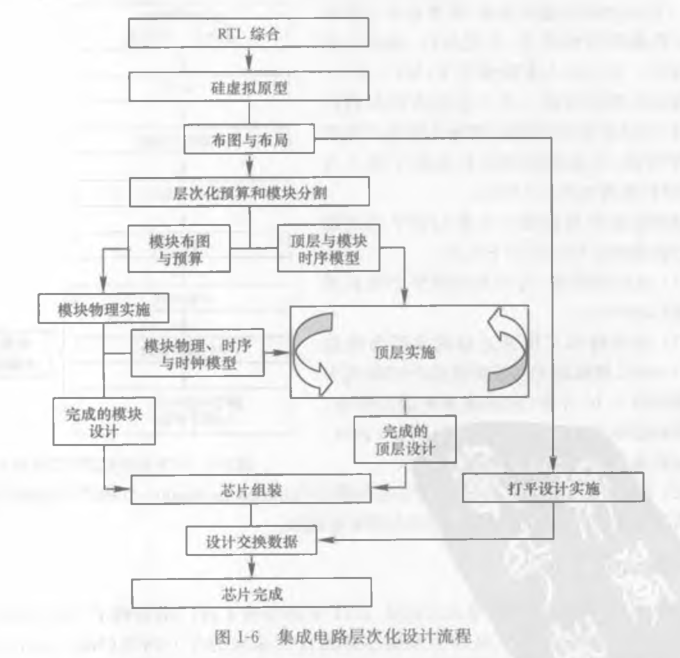

层次化物理设计

芯片面积die size

布线轨道:芯片内部专门用于布线的路径

布线通道:每两条或多条布线轨道的空间,他们上面不可以摆放标准单元

模块block:为层次化设计中从顶层分割而成的子模块,每个子模块可以包含一个或多个逻辑模块module。

当每个子模块实现了布局布线并满足时序要求后,可以产生自己的物理单元和时序单元,这时它就成为一个硬核模块。

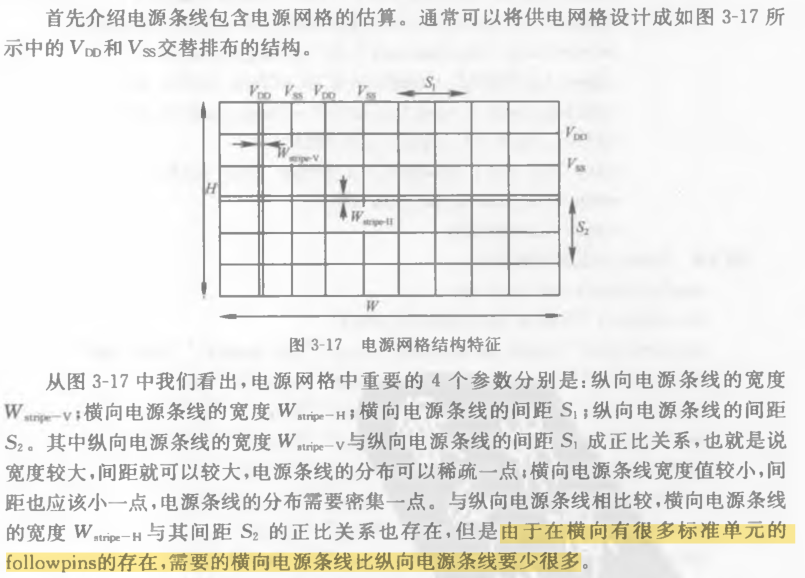

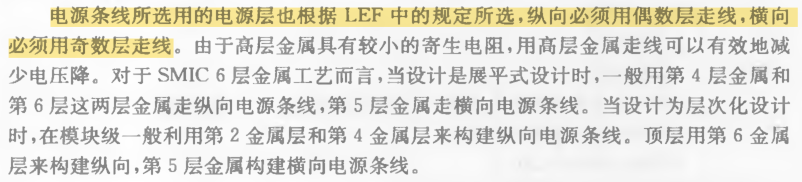

电源规划powerplan

给整个芯片的供电设计出一个均匀的网络。

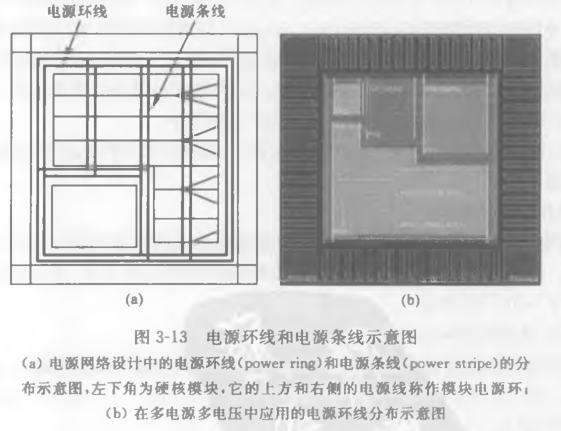

电源环线与电源条线:

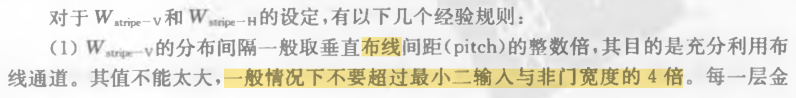

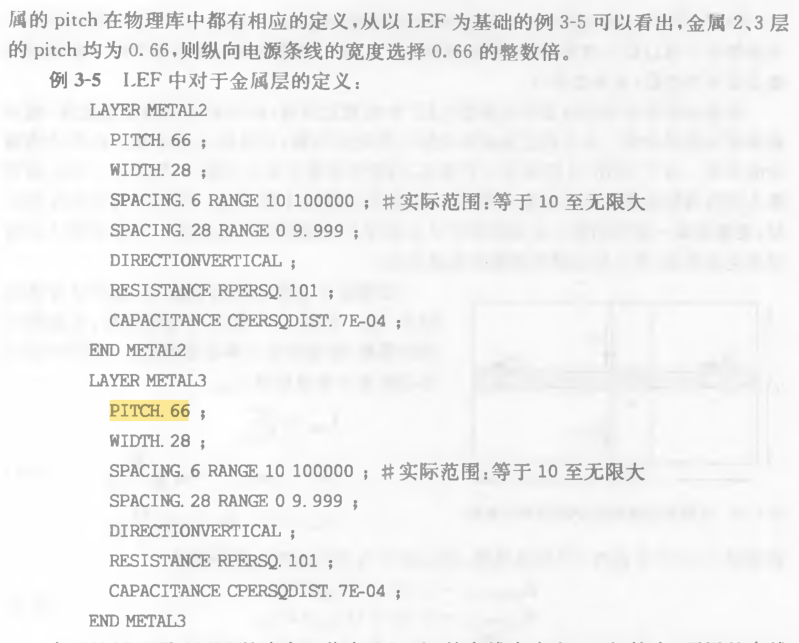

电源网络设计:

LEF文件:包括CEL、FRAM文件夹

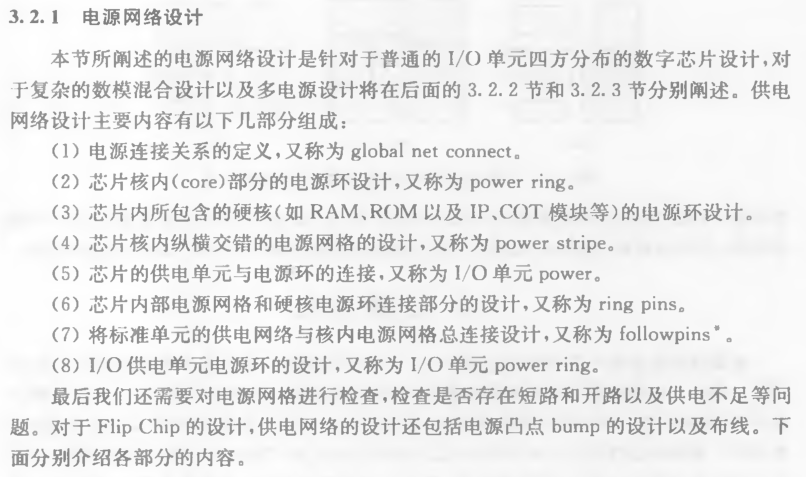

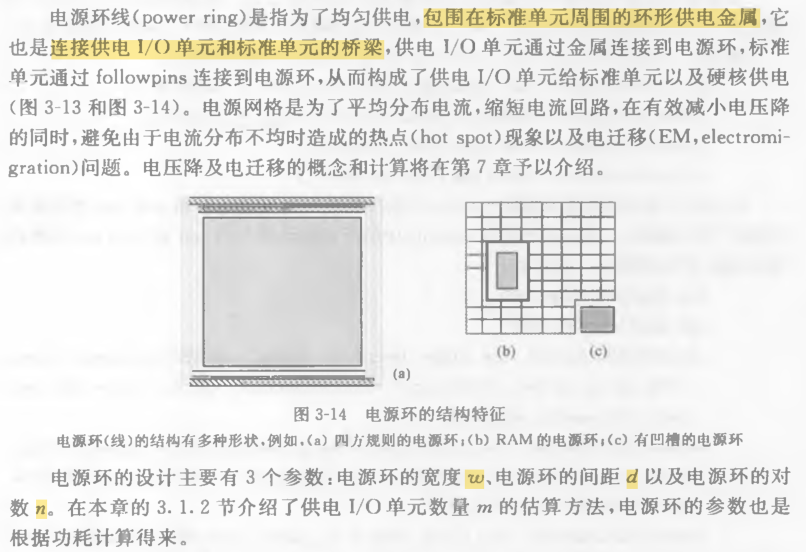

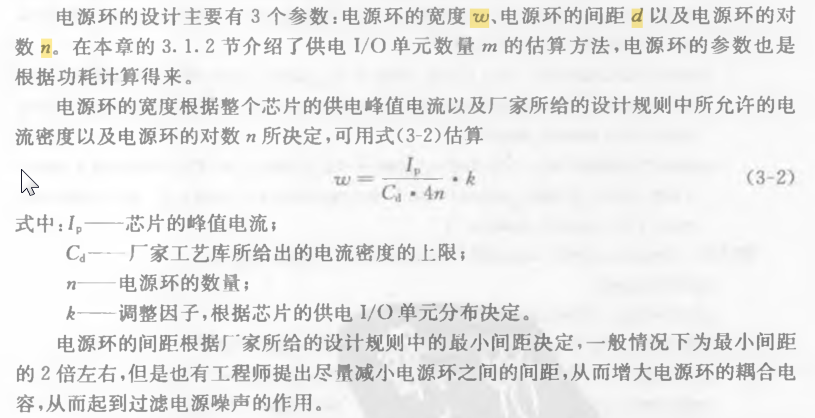

电源环线:

![]()

电源网格:

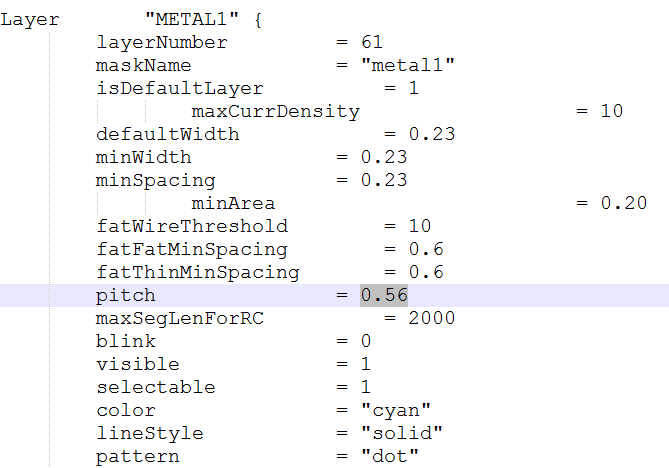

smic180 smic18_6lm.tf文件里指明的pitch如下,每一层金属的pitch不一样,via也有pitch

布局