---恢复内容开始---

pipeline control:看ppt

流水线不会改变lantency,但是会提高through put。

dependence:当前指令的data,下一个指令要用。

hazards:

structural hazards:两个指令要用一个resource

每一个stage的resource要不一样

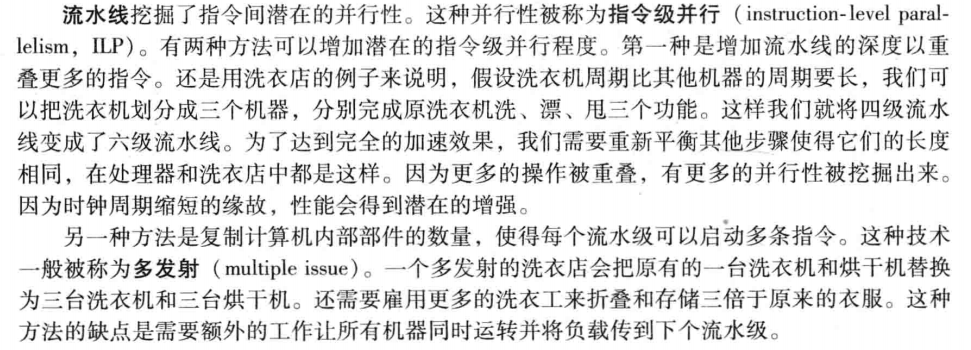

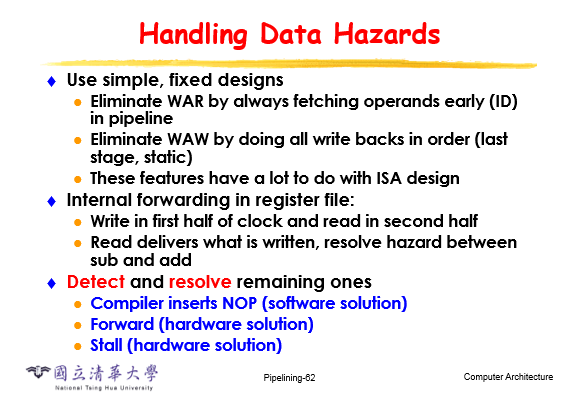

data hazards:有两类 forwarding/stalls

前三个都是错的:

1.write然后是read write还没写进去,read就开始读了,哔!hazard!MIPS会发生!

2.read然后write,write抢先,read读到错误的资料,哔!hazard!MIPS不会发生,因为设计中write永远在第5个stage,read在第二个stage

3.后面的先写进去了,哔!hazard!MIPS不会发生,因为设计中write永远在第5个stage

举例说明:

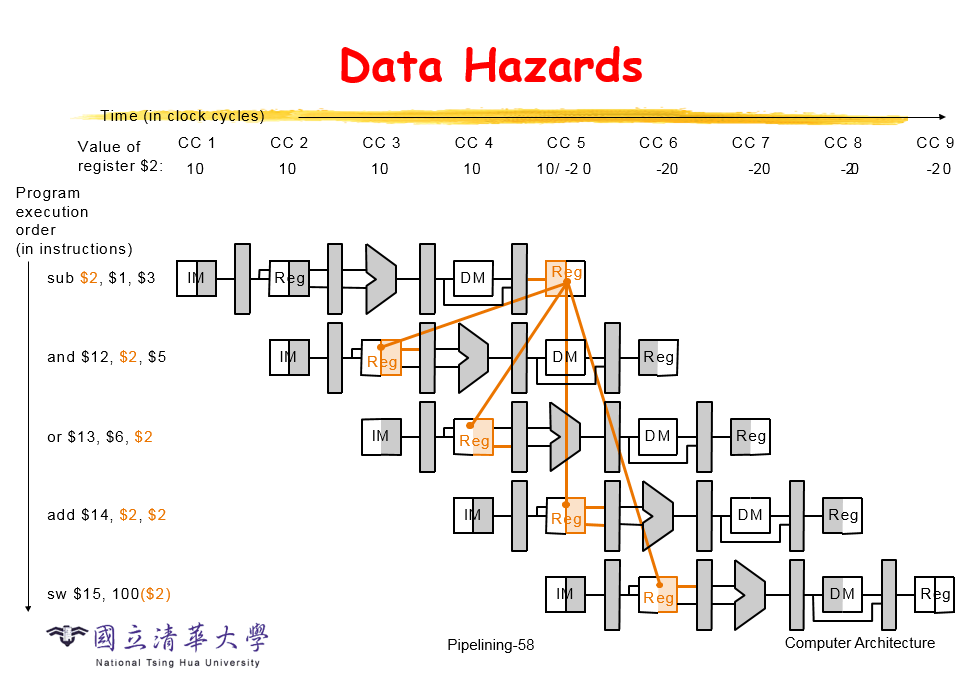

解决办法:

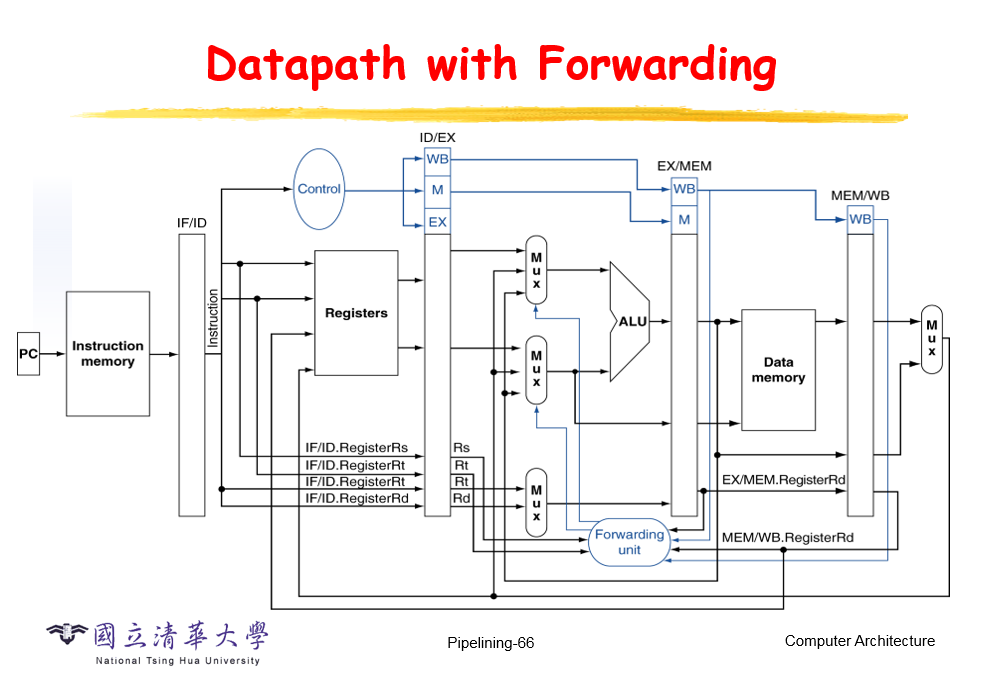

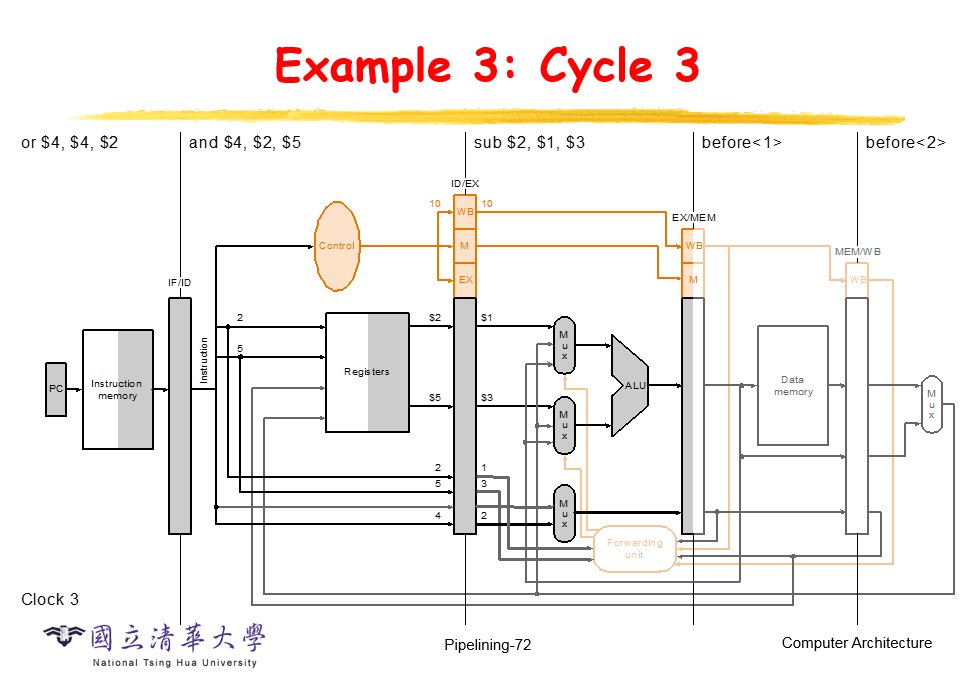

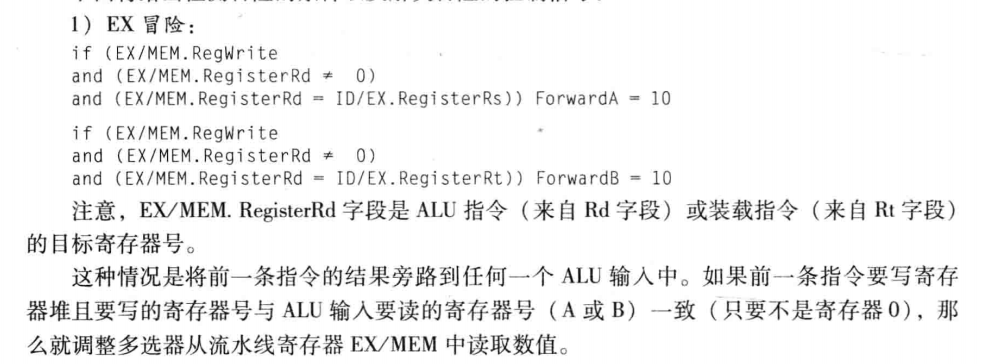

nop会浪费时间;stall是停;forwarding要注意两点:datapath的设计和什么时候要control

ALU要计算的值可能要用到不同pipeline里暂存的值:

这一部分书上写得更清楚一点,206页

·

·

load指令后面是R型指令就要stall,加一个nop;因为alu计算的是memory的地址,从EX/MEM流水线寄存器中拿到的是memory的地址而不是里面存储的值,所以要在memory之后才能拿到值

branch hazard就是一种control hazard

flush的方法:把control信号设为0,就是一个气泡,一个nop

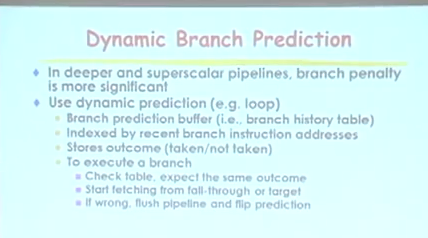

动态分支预测

branch prediction buffer:记录分支上次跳转到的指令,pc中分支指令的地址是知道的,table里面有index,只记录最近地址有跳转的

取指令之后要拿着指令去匹配这个table,匹配上的话就有输出;

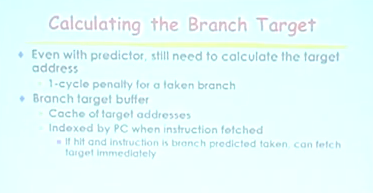

还要记录跳转到的指令的地址:

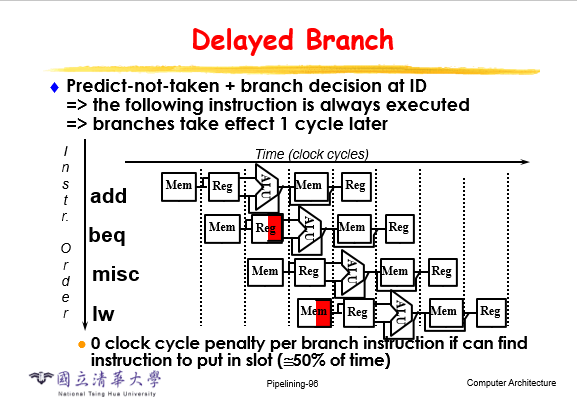

不管跳或不跳都要执行的指令.........branch的预测在第二个stage做决定;

第一个stage此时会取出下一个指令,可能是pc+4得到的,也可能是跳转的target address;

但是这两种都可能出错,因为不知道branch的结果到底是什么,但是等到当前的时钟周期结束,在第二个stage就能得到target address,

就知道到底是要跳还是顺序执行;

那么这个等待的时钟周期用什么来填补呢?

就是找出跳或者不跳都要执行的指令(50%的概率会找到)来填补,这样在下一个时钟周期就能拿到正确的指令。

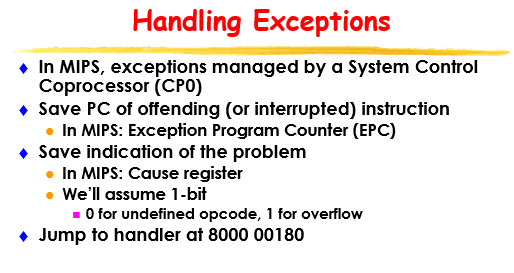

Exceptions:

不可预测的事件,可视为一种control hazard;

I/O的中断发生要等当前这条指令执行完毕,回来后继续执行下一条指令;

但是exception是当前的指令出错,情况不正常,所以要把当前指令再执行一遍;

指令的地址被存放在Exception Program Counter(EPC)

exception的处理有两种方式,在记录错误类型(MIPS里面只有两种,见ppt)后第一种:跳到一个入口(Single)

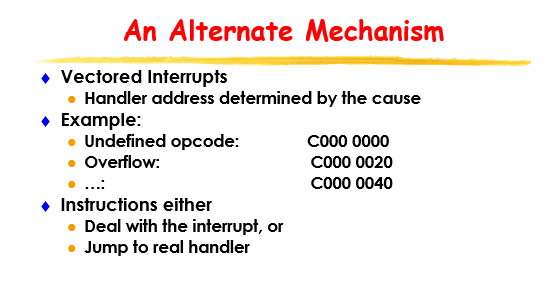

第二种:根据错误类型(作为index),直接跳到不同的位置处理:(Vectored Interrupts)

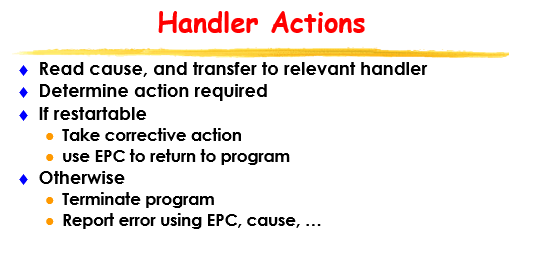

接下来是handler要做的事:

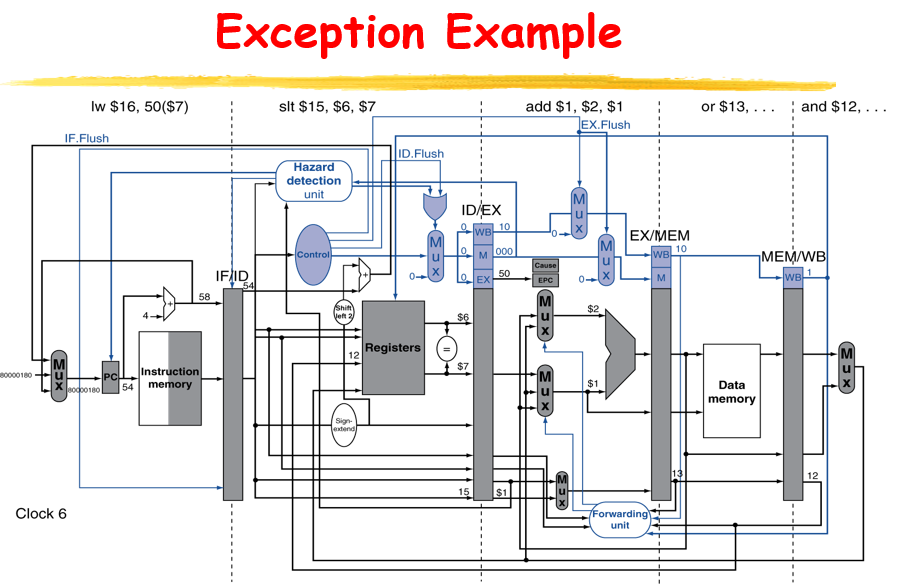

pipeline中的exception:

flush就是把control signal设成0,大体上和上面差不多

举例说明:

4c overflow 在80000180(指令)sw

出现多个exception的话,流水线又很多级,就丢给系统

流水线是指令集并行ILP的体现