第一部分

1、哈弗结构与冯氏结构

(1)区别:

是否有独立的存储架构和信号通道。

(2)举例:

8086:冯氏结构(相同的存储相同的通道)

STM32F103:哈弗结构(不同的存储、通道)

8051:改进的哈弗结构(不同的存储,相同的通道)

ARM9:改进的冯氏结构(相同的存储不同的通道)

高性能:单片机(冯氏结构)因为数据和程序都存储在cache中

单片机:哈弗结构,性能较低

2、总线和IO访问

总线:计算机各部件之间传递信息的公共干线,根据传递的信息的种类可以分为数据总线、控制总线、地址总线。

统一编址:从存储器地址空间中划出地址给IO端口

独立编址:IO端口地址空间和存储器的地址空间独立

3、处理机的状态

(1)ARM状态:

执行效率高。

(2)THUMB状态:

代码密度好(同一段代码,对于不同的单片机,编译之后占用的空间是不同)

4、处理机模式

(1)模式类型:

User(usr):一般的执行状态,不能切换到其他模式(只能通过中断和异常)

FIQ(fiq):快速中断,优先级较高

IRQ(irq):中断

Supervisor(svc):保护模式

Abort mode(abt):发生异常时进入

System(sys):用户安全模式

Undefined(und):未定义的指令

(2)目的:

提高响应速度

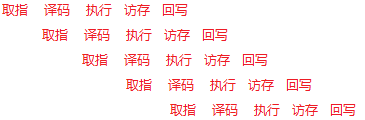

(3)ARM流水线

指令执行过程:

每条指令包括五个步骤:取指、译码、执行、访存、回写

单流水:

ARM9(五级流水):

第二部分

1、ARM内部寄存器:设计在CPU内部

(1)特点:速度快

(2)数量:一共有37个:

6个状态寄存器;

31个通用寄存器(R0-R12)

R13(SP):栈指针,不同模式下栈空间是不一样的

R14(LR):链接寄存器(存放断点),硬件自动完成

R15(PC):程序指针,取指令的位置

在FIQ模式下是独立的与其他模式不同

R16 PSR--CPSR(当前状态寄存器)

SPSR:程序状态寄存器

条件状态(NZCV)保留字 I F T 模式位(M4-M0)

SFR(Special Function Register)特殊功能寄存器

IO端口/寄存器,它属于外设的组成部分,ARM是采用与寄存器统一编址的方式

使用软件编程控制某一硬件,其实就是编程读写该硬件的寄存器

2、ARM异常处理

(1)模式与异常

异常的类型:

Reset:复位

undefined instruction:未定义

swi:软中断

prefect/bort

data/abort

Reserved

IRQ:中断

FIQ:快速中断

处理器的模式:每一个异常对应一种模式,但不是一一对应关系

(2)ARM异常处理的过程:

进入异常硬件完成下面动作:

(1)断点:放到LR里面,

(2)CPSR的值放到SPSR

(3)修改CPSR中的模式位

(4)PC跳到中断向量(异常向量)

软件完成下面的动作:

(1)中断散转,二级中断(由硬件完成,不需要手动代码)

(2)保护现场

(3)中断服务程序

(4)恢复现场(LR赋给PC,SPSR的值返回CPSR)

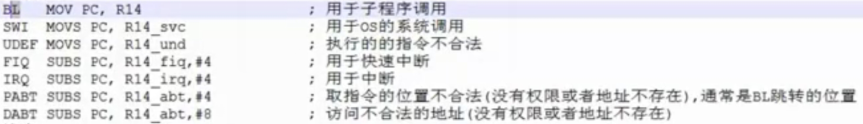

3、中断向量表

4、异常返回

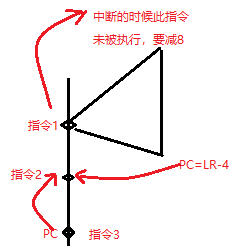

(1) PC在不同的情况下含义不一样,例如:PC(excute执行地址)=PC(fetch取址地址)-8,程序进入异常时LR的值(LR=PC-4)

(2)异常会清除处理器的流水线

(3)每种异常发生的时期不一样,对于中断而言,指令还未被执行就产生了,对于BL/SWI/UNEF而言,指令是执行过了的,当发生预言终止,将预取的指令标记为无效,在指令达到流水线执行阶段执行才进入异常,如果指令在流水线中因为分支而没有执行,异常不会发生。

(4)PATH和DABT常结合MMU和OS来使用,abort的处理程序就必须找出异常的原因,使要求的数据可用,并重试被终止掉的指令

5、存储系统

(1)存储器与存储控制器

存储器单元:存放数据的位置,地址是挂在系统总线

存储控制器:初始化存储器器件,有对应的寄存器配置,寄存器是挂在系统总线上

(2)存储器存储数据格式

大端格式:8051 ARM处理器将最高位字节保存在最低地址,最低字节保存在最高地址

小端格式:ARM,X86 一个字当中最低地址的字节被看做是最低位字节,最高地址的字节被看做是最高位字节

(3)对齐访问与非对齐访问

PC中的bit[1:0]为0

0x4000 0000 0x4000 0001 0x4000 0002 0x4000 0003 0x3322 1100

0x00 0x11 0x22 0x33

非对齐访问处理:

(1)不可预测

(2)忽略造成访问不对齐的低地址位

(3)先忽略最低两位,然后使用最低两位地址位控制装载数据循环右移(0x0033 2211)

知识点总结:

(1)PC(program counter:程序计数器):用于存放下一条指令所在单元的地址。

(2)LR(Link Register:连接寄存器)

作用有两种:

用来保存子程序返回地址;

当异常发生时,LR中保存的值等于异常发生时PC的值减4(或者减2),因此在各种异常模式下可以根据LR的值返回到异常发生前的相应位置继续执行。