来源:http://blog.csdn.net/yishuige/article/details/50434746

这一章涉及intel8086系列cpu的保护模式编程,应该是学习内核编程,驱动编程及嵌入式编程一些基础知识。不过对于没接触过底层编程的我来说,感觉还是好复杂 。

。

不过里面也有许多以前汇编学过的东西,大部分还是能看懂的 。我觉得图表就能说明大部分内容了,细节东西,不能都做笔记,所以大部分笔记都是图表- -。

。我觉得图表就能说明大部分内容了,细节东西,不能都做笔记,所以大部分笔记都是图表- -。

1,首先是关于8086cpu的各个标志寄存器,其内容如下:

2,内存管理的寄存器,主要用于实现分段内存管理机制,GDTR是全局段描述符表寄存器,IDTR是中断向量表寄存器,TR是任务寄存器,LDTR是局部描述符表寄存器。

其中,GDTR的内容基本上是不变的,一个系统一般只有一个全局段描述符表。LDTR则是在切换任务时重新加载,每个任务都有自己的局部描述符表。

3,控制寄存器,cr0~cr3,很重要的寄存器,控制cpu操作模式及当前任务的特性等等。具体各个寄存器的用法内容太多,还是看书吧 = =.

CR0:含有控制处理器操作模式和状态的系统控制标志。

CR1:保留不用。。。

CR2:含有导致页错误的线性地址,用于分页机制。

CR3:含有页目录表物理内存地址,也被称为页目录基地址寄存器PDBR。

用于操作以上寄存器的指令列表:

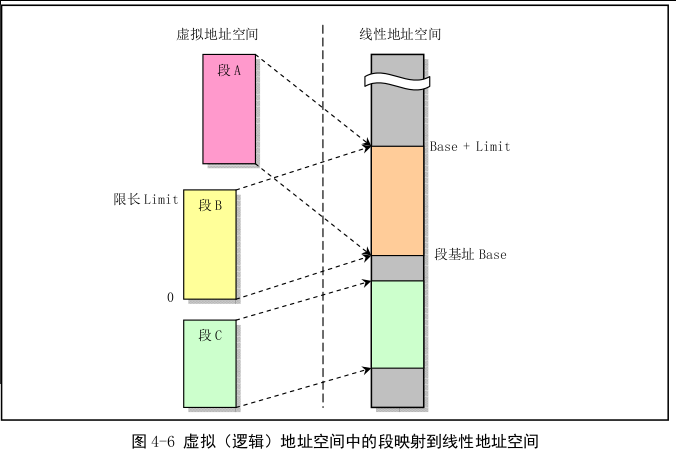

4,内存寻址方面,8086汇编都有讲过了。这里主要是分段管理机制与分页管理机制。

虚拟地址:http://baike.baidu.com/view/1499823.htm

分段机制中,每个段的大小不是固定的,因此使用段时必需通过查找段描述符表来获得段的信息。而分页机制中页的大小刚是固定的,每个页大小为4KB,。

分页存储是实现虚拟内存的关键,没有使用分页的话,要将整个段在主存与磁盘的虚拟内存之间移动,在效率及实现上都是不可接受的,通过分页,每次移4KB的数据是较好的方式。

由于线性地址为4GB,可分为1024*1024个页面,每个记录页表信息的页表项大小为4B,总共需要4MB的内存空间,这在早期物理内存只有可怜的几MB的计算机上是不允许的。所以又采用了二级页表的方式,通过一个4KB的页目录表可寻址到1024个页表,每个页表4KB存放1024个页表项。这样做并没有减少使用的内存总量,反而还多了4KB,之所以这样做是因为可以将二级页表整个移动到虚拟内存空间中,同一时间内只有几个活动的页表,可以节省大量的空间(对那个时候来说,0.12版只能支持最大16MB的主存 = =)。

没有使用分页机制的话,计算出来的线性地址将直接作为物理内存的地址。

分段跟分页都可以有保护机制,分页的保护比分段更底层,分段保证对段的访问有正确的权限及范围,而分页由图可以看出在分段保护通过后还会再进行分页机制的保护,保护内容主要是读写及访问权限。保护有任务之间的保护,保证任务不会访问到其他任务的内存空间,还有特权级的保护,控制系统任务与用户任务之间的访问关系。

5,分段的细节:

内容太多了,还是弄弄图就好了。

段与段之间并不一定是完全分开的,有可能交叉甚至重叠。

访问段,通过选择符定位找到段描述符表中的一个描述符,再通过段描述符访问具体的段。一个描述符表只有2^13=8192个描述符,所以选择符前三个位不用于定位,前两位用于表示特权级,第三位用于表示要访问的段是在全局描述符表中还是局部描述符表中。

局部描述符表也作为一个段,其段描述符保存在全局描述符表中