简单介绍:

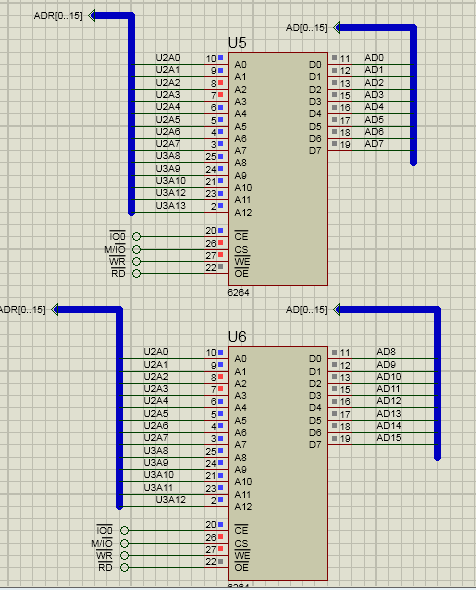

在8086系统中,CPU有16根数据线,而存储器一个基本单元(字节)有8根数据线,因此通常将存储系统分为偶体存储器和奇体存储器与8086cpu相连的方法。根据8086cpu的规定,偶地址单元在数据线低8位上传输,奇地址单元的数据在高8位数据线上传输。一个存储体包含全部偶数地址的单元,叫偶体存储器;另一个存储体包含全部奇数地址单元,叫奇体存储器。偶体存储器的8根数据线连接到数据总线低8位上,地址线最低位A0用作偶体存储器,奇体存储器的8根数据线连接到数据总线的高8位上,8086引脚用BHE(上划线)低电平作为奇体存储器的选择信号。

存储器的操作有4中情况:

1.8086cpu访问偶地址的字节单元时,cpu输出A0=0,选中偶体存储器,数据总线的低8位上传输,花费一个总线周期。

2.访问奇地址的字节单元时,输出A0=1,BHE(上划线)低电平,选中奇体存储器,数据在数据总线的高8位上传输,花费一个总线周期。

3.访问偶地址开始的一个字单元时,此时输出A0=0,BHE=0,两个存储器同时被选中,数据线的低8位与高8位同时传输,因此,对所有位于偶地址的字单元,8086只需要一个总线周期。

4.访问奇地址开始的一个字单元时,第一个总线周期,cpu输出A0=1,BHE=0,奇体存储器被选中,奇体存储器中低字节数据在数据总线的高8位上传输,第二个总线周期,cpu=A0,BHE=1,偶体存储器被选中,数据在数据总线的低8位上传输。

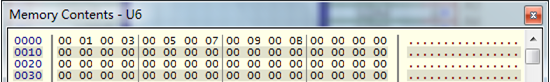

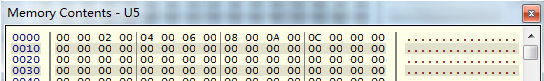

使用Proteus仿真进行仿真看一下字节单元的情况: