Verilog语言中讲的阻塞赋值与非阻塞赋值,但从字面意思来看,阻塞就是执行的时候在某个地方卡住了,等这个操作执行完在继续执行下面的语句,而非阻塞就是不管执行完没有,我不管执行的结果是什么,反正我继续下面的事情。而Verilog中的阻塞赋值与非阻塞赋值正好也是这个意思,通过执行一个例子,就可以简单地明白了:

1、阻塞赋值可以理解为语句的顺序执行,因此语句的执行顺序很重要

2、非阻塞赋值可以理解为语句的并行执行,所以语句的执行不考虑顺序

3、在assign的结构中,必须使用的是阻塞赋值

//阻塞

module blocking(clk,a,b,c ); input[3:0] a; output[3:0] b,c; input clk; reg[3:0] b,c; always @(posedge clk) begin b=a; c=b; $display("Blocking: a=%d,b=%d,c=%d",a,b,c); end endmodule

//非阻塞

module non_blocking(clk,a,b,c ); input[3:0] a; output[3:0] b,c; input clk; reg[3:0] b,c; always @(posedge clk) begin b<=a; c<=b; $display("non_Blocking: a=%d,b=%d,c=%d",a,b,c); end endmodule

//测试

module test; wire[3:0] b1,c1,b2,c2; reg[3:0] a; reg clk; initial begin clk=0; forever #50 clk=~clk; end initial begin a=4'h3; $display("__________________"); #100 a=4'h5; $display("__________________"); #100 a=4'hf; $display("__________________"); #100 a=4'ha; $display("__________________"); #100 a=4'h6; $display("__________________"); #100 a=4'h2; $display("__________________"); #100 $display("__________________"); $stop; end blocking blocking(clk,a,b1,c1); non_blocking non_blocking(clk,a,b2,c2); endmodule

结果:

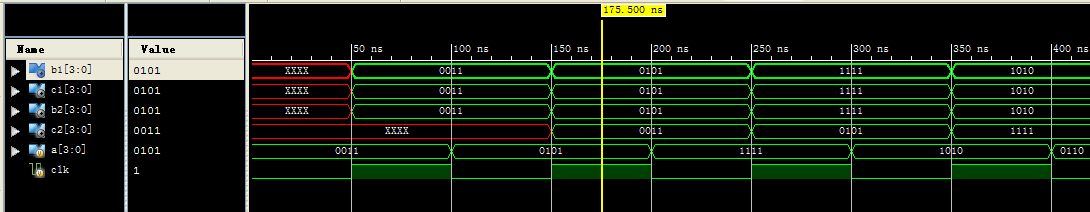

仿真波形: